Visible to Intel only — GUID: scr1669056709160

Ixiasoft

Visible to Intel only — GUID: scr1669056709160

Ixiasoft

G.3.2. DTK Margin Evaluation Based on Margin Mask Values

This section describes the process of margin evaluation obtained by the Eye Viewer against the Margin Mask provided in Margin Mask Values for the P-Tile Avalon Streaming Intel FPGA IP for PCI Express. It also defines the conversion steps to pass from mUI or mV to ticks for the margin evaluation.

Once the eye plot is complete in DTK, the eye height, eye width and eye diagram are displayed. You have to manually check if the current margins are above the Margin Mask values defined in Margin Mask Values for the P-Tile Avalon Streaming Intel FPGA IP for PCI Express, following the next steps.

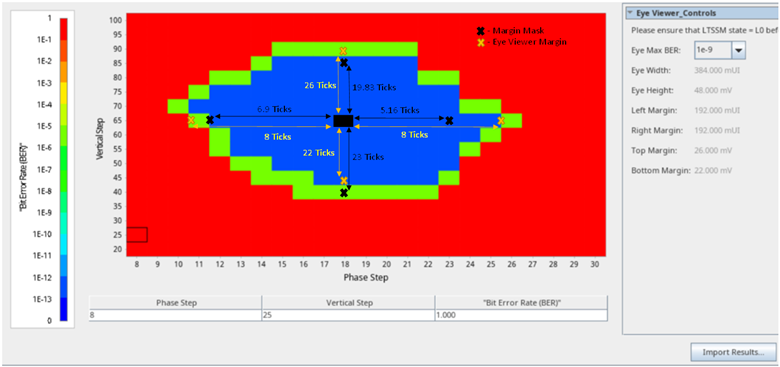

As an example, we are going to use Comparing Mask and Eye Viewer which has margin results on Lane 0 at Gen 4.0 speed with Eye Max BER 1e-9.

- To check if the Left Margin is above the Timing Left Margin Mask value defined in Margin Mask Values for the P-Tile Avalon Streaming Intel FPGA IP for PCI Express, you need to manually convert the resulted margin value from mUI to tick, where one tick is equal to 24 mUI at Gen 4 speed. So, taking the values of Comparing Mask and Eye Viewer, 192.000mUI / 24mUI = 8 ticks for the Left Margin. In this case, run a 1x1 (1 part x 1 repetition) and take the timing values of the 2x5 at PCIe 4.0 BER 1-9 in Margin Mask Values for the P-Tile Avalon Streaming Intel FPGA IP for PCI Express because this is the minimum experiment number. Checking the Timing Left Margin value from this table, you can see that the current Left Margin (8 ticks) is above the value defined in the table, which is 6.9 Ticks. Comparing Mask and Eye Viewer was manually edited to show where margin values are on the eye plot.

- Follow the same process as defined in step 1 to check if the Right Margin is above the Timing Right Margin Mask value defined in Margin Mask Values for the P-Tile Avalon Streaming Intel FPGA IP for PCI Express. You need to manually convert the resulted margin value from mUI to tick, where one tick is equal to 24 mUI at Gen 4 speed. So, taking the values of Comparing Mask and Eye Viewer, 192.000mUI / 24mUI = 8 ticks for the Right Margin. Comparing the Timing Right Margin value from Margin Mask Values for the P-Tile Avalon Streaming Intel FPGA IP for PCI Express, you can see that the current Right Margin (8 ticks) is above the value defined in the table, which is 5.16 ticks. Comparing Mask and Eye Viewer was manually edited to show where margin values are on the eye plot.

- Now, check if the Up Margin is above the Voltage Up Margin Mask value defined in Margin Mask Values for the P-Tile Avalon Streaming Intel FPGA IP for PCI Express. You need to manually convert the resulted margin value from mV to tick, where one tick is equal to 1 mV at Gen 4 speed. So, taking the values of Comparing Mask and Eye Viewer, 26.000 mV = 26 ticks for Up margin. Verifying the Voltage Up Margin value from Margin Mask Values for the P-Tile Avalon Streaming Intel FPGA IP for PCI Express, you can see that the current Up Margin (26 ticks) is above the value defined in the table, which is 19.83 ticks. Comparing Mask and Eye Viewer was manually edited to show where margin values are on the eye plot.

- Finally, check if the Down Margin is above the Voltage Down Margin Mask value defined in Margin Mask Values for the P-Tile Avalon Streaming Intel FPGA IP for PCI Express. You need to manually convert the resulted margin value from mV to tick, where one tick is equal to 1 mV at Gen 4 speed. So, taking the values of Comparing Mask and Eye Viewer, 22.000 mV = 22 ticks. You can check that the current Down Margin (22 ticks) is below the value defined in Margin Mask Values for the P-Tile Avalon Streaming Intel FPGA IP for PCI Express, which is 23.00 ticks. In this particular case, you need to consider that we are using 2x5. However, in the case where five parts are tested, the Voltage Down Margin is lower.

If any value of the Eye Viewer is over the Margin Mask value, it means that the test values are good and exceed the minimum values required. Otherwise, if the value of the Eye Viewer is under the Margin Mask value, it means that there are more CRC errors than expected and the link has not been trained well.

In the figure below, you have an example of how to compare the values of the Margin Mask and the Eye Viewer Margins.