Visible to Intel only — GUID: ptf1567033152484

Ixiasoft

Visible to Intel only — GUID: ptf1567033152484

Ixiasoft

E.1. Overview

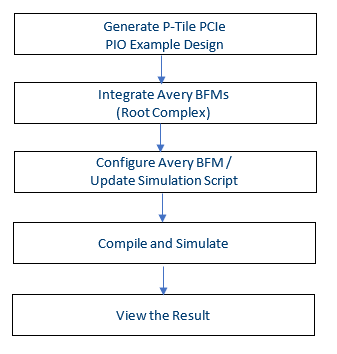

This appendix describes how to set up an Intel P-Tile PCIe Gen4 x16 Endpoint simulation using Avery BFMs for the Synopsys VCS simulator.

The Avery BFM simulation example described here is based on the PCIe Programmed I/O (PIO) example design generated from the Intel® Quartus® Prime PCIe IP GUI. Although the simulation flow and testbench setup leverage the Intel® Quartus® Prime example design testbench files, a similar flow and setup can be used for other PCIe system simulations with the P-Tile PCIe IP core.

- Intel® Quartus® Prime version 20.3 or later

- Intel P-Tile Avalon® -MM/ Avalon® -ST PCIe IP version 3.1.0 or later

- Avery BFM version 2.2b

- Synopsys VCS Simulator version O-2018.09-SP2-2

Simulation Script Files

The following table describes the files required for running simulations and the locations where they need to be. Contact your local Field Applications Engineer (FAE) to get a sample copy of these files.

You can use these files as-is for Gen4 x16 PIO simulations based on the P-Tile PCIe PIO example design.

| File Name | Description | Destination Folder |

|---|---|---|

| apci_top_rc.sv | Avery BFMs (Gen4 x16) and memory write & read traffic generation | <example design folder>/pcie_ed_tb/pcie_ed_tb/sim |

| pci_ed_tb.sv | Top-level testbench including Avery BFMs and PCIe PIO example design | <example design folder>/pcie_ed_tb/pcie_ed_tb/sim |

| vcs_files.tcl | List of design example simulation files

Note: The testbench top level is a System Verilog file called pcie_ed_tb.sv.

|

<example design folder>/pcie_ed_tb/pcie_ed_tb/sim/common |

| avery_files_vcs.f | Avery BFM simulation files | <example design folder>/pcie_ed_tb/pcie_ed_tb/sim/synopsys/vcs |

| vcs_setup.sh | VCS simulation script | <example design folder>/pcie_ed_tb/pcie_ed_tb/sim/synopsys/vcs |