AN 793: Intel® Arria® 10 DisplayPort 4Kp60 with Video and Image Processing Pipeline Retransmit Reference Design

Reference Design Debug Features

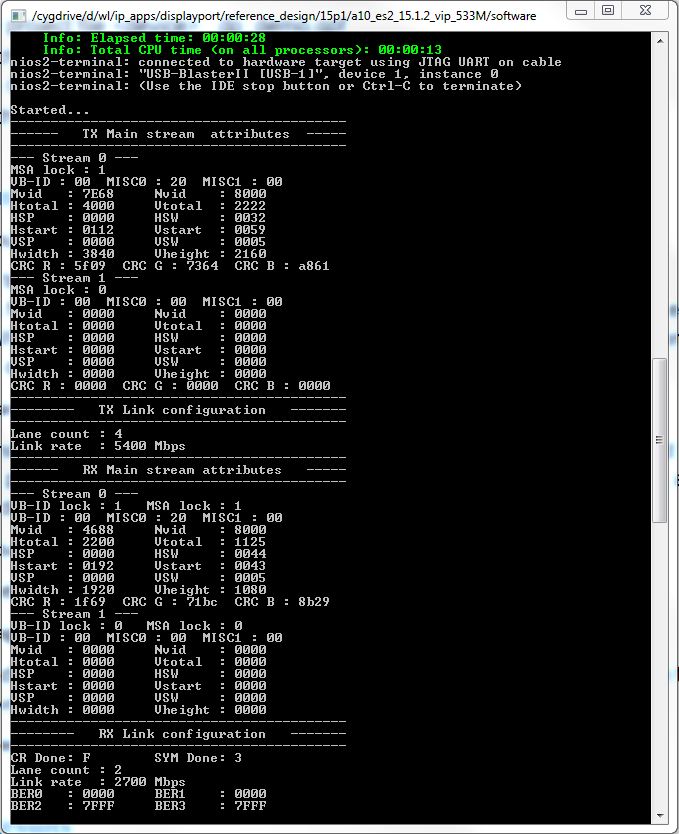

Main Stream Attribute Info

This debug feature is a part of the DisplayPort IP Core hardware demonstration design example. To display the Main Stream Attribute (MSA) of DisplayPort TX and RX cores, press the PB0 push button (S3) on the development kit. The TX and RX stream MSA values appears on the Nios II terminal.

Auxiliary Channel Traffic Monitor

#define BITEC_AUX_DEBUG 1 // Set to 1 to enable AUX CH traffic monitoring Rebuild the Nios II software and download the ELF image into the FPGA.

Logic Analyzer

If you want to monitor the Avalon-ST stream of the Clocked Video Input II, Clocked Video Output II, and Mixer II signals, recompile this reference design by enabling the SignalTap II Logic Analyzer using dp_vip_xcvr.stp. This STP file also includes a list of clocked video signals of DisplayPort sink–Clocked Video Input II, DisplayPort source–Clocked Video Output II, and DisplayPort–transceiver interfaces.

You can monitor the TX and RX recovered clock frequency by reading the values at the refclock_measure ports in the mr_rate_detect.v module.

System Console

- The TCL script in the tcl folder allows you to control the operation of the VIP IP cores.

- The main.tcl script contains the procedures to access the Clocked Video Input II, Clocked Video Output II, Mixer II, and Frame Buffer II control and status registers.

- The vip_csr_offset.tcl file contains the CSR offset of the Clocked Video Input II, Clocked Video Output II, Mixer II, and Frame Buffer II IP cores.

- The system_base_addr_map.tcl contains the Qsys base address of these VIP IP cores.

- Drill into the VIP Qsys subsystem and enable the CSR Avalon-MM interface of the IP core.

- Connect the control port (Avalon-MM slave) to the m0 port of the Avalon-MM Pipeline Bridge component, mm_bridge_vip.

When assigning the base address in the VIP Qsys subsystem of the Avalon-MM slave of the VIP IP cores, follow the address map in the system_base_addr_map.tcl file:

- Clocked Video Input II: 0x0000

- Mixer II: 0x0200

- Clocked Video Output II: 0x0400

- Frame Buffer II: 0x0800

In dp_core.qsys, open the Address Map tab, and ensure the base address for connecting master_0.master and vip.mm_bridge_vip_s0 starts from 0x0000.

Move up to the top-level Qsys from VIP subsystem, regenerate the Qsys and perform a full compilation. To have full control of the VIP IP cores CSR, (e.g. to debug no video output issue), stop the Nios II processor from accessing the CSR.

- Clear the ALT_VIP flag in config.h:

#define ALT_VIP 0 // Set to 1 if a VIP IP core (e.g. Mixer II) is used

- Rebuild the Nios II software and program the updated ELF file.

- Launch the system console and type these commands to load the main.tcl file and display the Mixer II output:

cd tcl

source main.tcl

go

Note: You may need to modify the master_index variable in the main.tcl file to access the correct service path. - To stop the Mixer II from displaying video stream at its input 0 port and display the color bar only, type

mixer_input0_stop