Visible to Intel only — GUID: iiq1683037264543

Ixiasoft

Visible to Intel only — GUID: iiq1683037264543

Ixiasoft

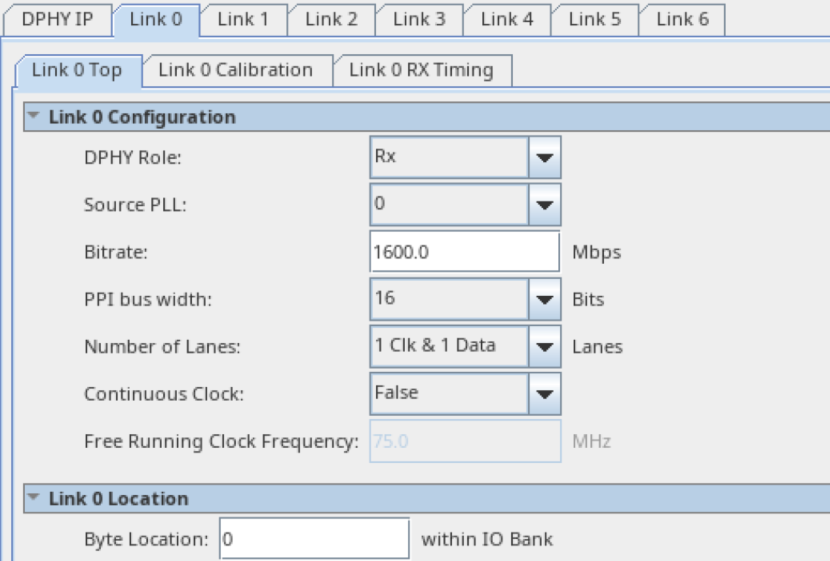

5.3. Configuring the MIPI D-PHY RX Mode

You need to specify the MIPI D-PHY link location on the I/O bank during IP configuration. Look for the Byte Location parameter under the Link n Location for each Link n tab. For the physical pin location of each byte location, refer to the table in the Identifying Pin Assignments Based on Byte Location topic.

| Parameter Name | Description | Setting |

|---|---|---|

| D-PHY Role | Configure D-PHY mode as Tx or Rx. If not using the channel, please remain it as unused. | TX/RX/Unused. (Default value is Unused.) |

| Source PLL | Specify which PLL source to drive the link's clock. 0 = PLL from Bottom Sub bank 1 = PLL from Top Sub bank |

0 or 1. (Default value is 0.) |

| Bit Rate | Configure the MIPI D-PHY data rate. | D-Series: 150Mbps - 3500Mbps E-Series device group A: 150Mbps - 3500Mbps E-Series device group B: 150Mbps - 2500Mbps |

| PPI bus width | Set PPI bus width for data lanes in the link : 16 bits. | 16. |

| Number of Lanes | Set number of data lanes for the link : 1, 2, 4 or 8. | 1 Data & 1 Clk 2 Data & 1 Clk 4 Data & 1 Clk 8 Data & 1 Clk (Default is 1 Data & 1 Clk.) |

| Continuous Clock | Specify that the clock lane is continuous. | True or False. (Default value is False.) |

| Free Running Clock Frequency | Rx free running clock frequency in MHz. When calibration is enabled, this will be fixed to RX clock. | |

| Byte Location | Specifies D-PHY links BYTE location within the I/O bank. | 0-7. |

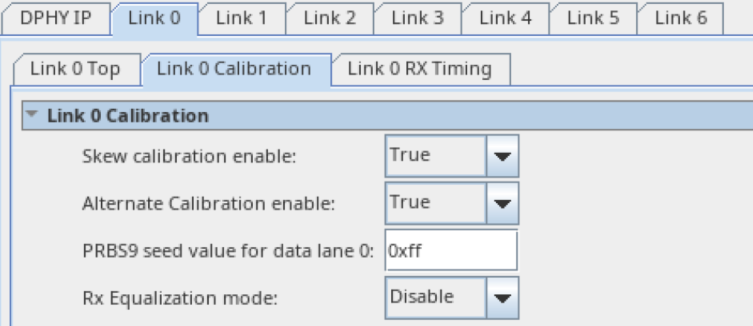

Link Calibration Configuration

On the Link Calibration tab you can enable the skew and alternate calibration functions and RX equilization mode. You can run simulation to validate which RX equalization mode suits your design intent.

| Parameter Name | Description | Setting |

|---|---|---|

| Skew Calibration Enable | Generate logic to support skew calibration. | True or False. (Default value is False.) |

| Alternate Calibration Enable | Generate logic to support alternate calibration. (Available when skew calibration mode is enabled.) | True or False. (Default value is False.) |

| PRBS9 seed value for data lane n | PRBS value for data lane used by Tx / Rx alt cal and test mode. (Available when Alternate Calibration is enabled.) | 0xFF |

| Rx Equalization mode | Rx Equalization mode | Disable or EQ SML or EQ MED or EQ LRG. Default value is Disable. |

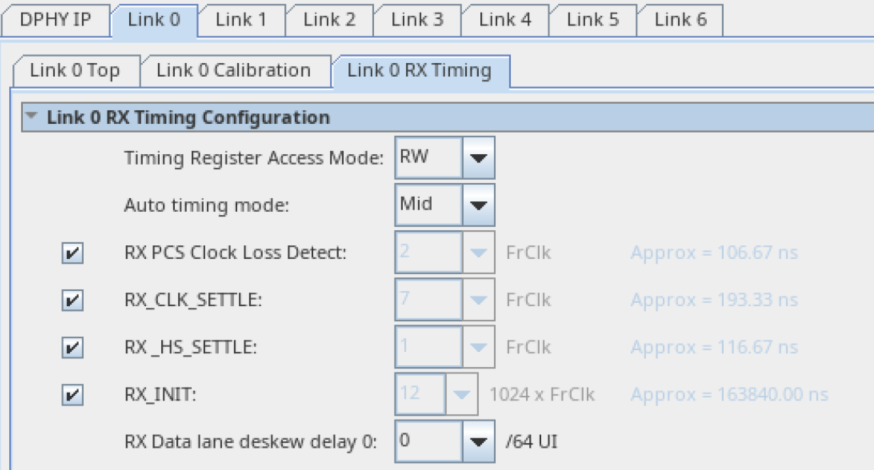

Link RX Timing Configuration

On the Link RX Timing tab you can configure the receive timing parameters.

| Parameter Name | Description | Setting |

|---|---|---|

| Timing Register Access Mode | Set to implement timing registers as R/W or RO. When using R/W mode, more register consumes in logic element resources. |

RW or RO. (Default is RW.) |

| Auto Timing mode | Set Rx to be fixed at MID. Choose to use min timing, max timing or mid for default values of timing registers set to "Auto". All timing registers have a min specified timing, but not all have a max specified timing. For those with no max specified timing, max is set to register max value.

|

Max, Mid, or Min. (Default is Mid.) |

| RX PCS Clock Loss Detect | Timeout for D-PHY PCS to detect absence of Clock transitions and deassert RxClkActiveHS on the PPI bus. Min value should be equal to 3 x RX_CLK-period (in ns). This is different from the D-PHY specification TCLK-MISS. This will be used to clock gate MIPI RX forwarded clock delay computations (approx): - TRX_CLK_LOSS_DETECT = (RX_CLK_LOSS_DETECT + 6) * Core_CLK_period. |

0-255. (Default is 2.) |

| RX_CLK_SETTLE | Time interval during which the HS receiver should ignore any Clock Lane HS transitions, starting from the beginning of TCLK-PREPARE. Delay computation (approx): TRX-CLK-SETTLE = (RX_CLK_SETTLE + 6) * Core_CLK_period + 2 * RX_CLK_period. | 0-255. (Default is 7.) |

| RX_HS_SETTLE | Time interval during which the HS receiver shall ignore any Data Lane HS transitions, starting from the beginning of THS-PREPARE. The HS receiver shall ignore any Data Lane transitions before the minimum value, and the HS receiver shall respond to any Data Lane transitions after the minimum val Delay computation (approx): THS-SETTLE = (RX_HS_SETTLE + 7) * Core_CLK_period + RX_CLK_period. | 0-255. (Default is 1.) |

| RX_INIT | After power-up, the RX side PHY shall be initialized when the TX PHY drives a Stop State (LP-11) for a period longer than TINIT. RX side shall ignore all Line states prior to this Initialization period. | 0-255. (Default is 12.) |

| RX Data Lane deskew Delay 0 | Manual data Lane 0 deskew delay setting . | 0-63. (Default is 0.) |