Visible to Intel only — GUID: ldr1683035972064

Ixiasoft

Visible to Intel only — GUID: ldr1683035972064

Ixiasoft

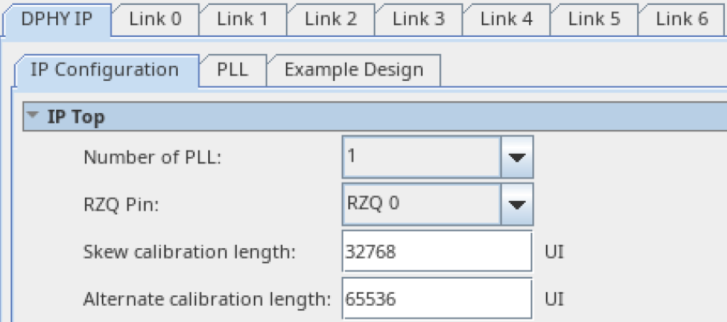

5.2. Configuring the D-PHY IP Tab

| Parameter Name | Description | Setting |

|---|---|---|

| Number of PLL | Set number of PLL to use for clock generation. The IP can use up to 2 PLLs to share among the different D-PHY links. The bit rates of the D-PHY links has to be the same to share a PLL. | 1 or 2. (Default value is 1.) |

| RZQ Pin | Set RZQ pin location to use for the D-PHY IP. | RZQ0 or RZQ1. (Default value is RZQ0.) Pin 38 in one I/O bank is RZQ0 and pin 62 is RZQ1. Pin 38 reserves BYTE LOCATION 3, and pin 62 reserves BYTE LOCATION 5. |

| Skew calibration length | Length of initial skew calibration pattern automatically generated by D-PHY TX IP when SKEW_CAL_EN = 1. This is done automatically after the t INIT period. When SKEW_CAL_EN = 0, protocol IP is responsible to drive TxSkewCalHS to generate init skew sequence. SKEW_CAL_LEN is ignored by D-PHY RX IP. | 32768 (This is the default value and the minimum.) |

| Alternate calibration length | Length of alternate calibration pattern automatically generated by D-PHY TX IP when ALT_CAL_EN = 1. This is done automatically after the init skew. When SKEW_CAL_EN = 0, protocol IP is responsible to drive TxAlTCalHS to generate alt cal sequence.ALT_CAL_LEN is ignored by D-PHY RX IP. | 65536 (This is the default value and the minimum.) |

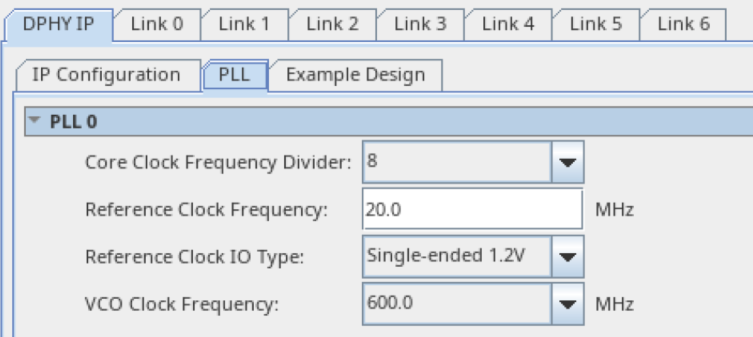

D-PHY IP PLL Tab

On the PLL tab, you configure the PLL settings such as core clock divider, PLL reference clock frequency, I/O standard selection, and VCO clock frequency.

| Parameter Name | Description | Setting |

|---|---|---|

| Core clock frequency divider | Set core clock frequency divider to generate core clock from VCO output. MIPI only supports divided by 4 or 8. | 4 or 8. (Default value is 8.) |

| Reference clock frequency | PLL reference clock frequency. | 10MHz - 300MHz. (Default value is 20MHz.) |

| Reference clock I/O type | Reference Clock I/O standard. | Single Ended 1.2V, LVDS 1.2V Single Ended 1.1V, LVDS 1.1V . |

| Share Reference Clock I/O | Enable PLL1 share reference clock with PLL0. | True or False. (Default value is True.) |

| VCO Clock Frequency | Sets the VCO clock frequency for PLL. - MIPI TX with bitrate > 1.2Gbps: VCO freq = 1/2 bit rate. - MIPI TX with bitrate 1.2Gbps: VCO freq = 1/2 bitrate * Tx bitrate divider (1, 2, 4 of 8). - MIPI RX with skew calibration disabled: no dependency between VCO freq and bit rate. -MIPI RX with skew calibration enabled: VCO freq = 1/2 bitrate |

600MHz - 1740MHz. |