Visible to Intel only — GUID: faq1683074513574

Ixiasoft

Visible to Intel only — GUID: faq1683074513574

Ixiasoft

6.1.6. AXI-Lite CSR Access

Multiple links are accessed from the same AXI-Lite interface using the memory map described below. Aside from allowing access to the D-PHY internal IP registers, the AXI-Lite bus is designed to allow access to external registers which are used for accessing the PPI TG.

| Start | End | Link Number | Register Space |

|---|---|---|---|

| 0x000 | 0x07F | 0 | D-PHY IP registers for Link 0 |

| 0x080 | 0x0FF | D-PHY IP shared (mirrored) | |

| 0x100 | 0x17F | External Shared (mirrored) | |

| 0x180 | 0x1FF | External registers for Link 0 | |

| 0x200 | 0x27F | 1 | D-PHY IP registers for Link 1 |

| 0x280 | 0x2FF | D-PHY IP shared (mirrored) | |

| 0x300 | 0x37F | External Shared (mirrored) | |

| 0x380 | 0x3FF | External registers for Link 1 | |

| 0x400 | 0x47F | 2 | D-PHY IP registers for Link 2 |

| 0x480 | 0x4FF | D-PHY IP shared (mirrored) | |

| 0x500 | 0x57F | External Shared (mirrored) | |

| 0x580 | 0x5FF | External registers for Link 2 | |

| 0x600 | 0x67F | 3 | D-PHY IP registers for Link 3 |

| 0x680 | 0x6FF | D-PHY IP shared (mirrored) | |

| 0x700 | 0x77F | External Shared (mirrored) | |

| 0x780 | 0x7FF | External registers for Link 3 | |

| 0x800 | 0x87F | 4 | D-PHY IP registers for Link 4 |

| 0x880 | 0x8FF | D-PHY IP shared (mirrored) | |

| 0x900 | 0x97F | External Shared (mirrored) | |

| 0x980 | 0x9FF | External registers for Link 4 | |

| 0xA00 | 0xA7F | 5 | D-PHY IP registers for Link 5 |

| 0xA80 | 0xAFF | D-PHY IP shared (mirrored) | |

| 0xB00 | 0xB7F | External Shared (mirrored) | |

| 0xB80 | 0xBFF | External registers for Link 5 | |

| 0xC00 | 0xC7F | 6 | D-PHY IP registers for Link 6 |

| 0xC80 | 0xCFF | D-PHY IP shared (mirrored) | |

| 0xD00 | 0xD7F | External Shared (mirrored) | |

| 0xD80 | 0xDFF | External registers for Link 6 |

Each link has its own register space, with additional space reserved for connecting to an external agent. Those registers in the mirrored addresses are shared by all links. For an example of these mirrored registers, refer to the topic. For the D-PHY IP design example, the reserved space is used for TG registers as shown below:

| Start | End | Link Number | Register Space |

|---|---|---|---|

| 0x000 | 0x07F | 0 | D-PHY IP registers for Link 0 |

| 0x080 | 0x0FF | D-PHY IP shared (mirrored) | |

| 0x100 | 0x17F | TG top level registers mirrored across all links (mirrored) | |

| 0x180 | 0x1FF | TG registers for Link 0 | |

| 0x200 | 0x27F | 1 | D-PHY IP registers for Link 1 |

| 0x280 | 0x2FF | D-PHY IP shared (mirrored) | |

| 0x300 | 0x37F | TG top level registers mirrored across all links (mirrored) | |

| 0x380 | 0x3FF | TG registers for Link 1 | |

| 0x400 | 0x47F | 2 | D-PHY IP registers for Link 2 |

| 0x480 | 0x4FF | D-PHY IP shared (mirrored) | |

| 0x500 | 0x57F | TG top level registers mirrored across all links (mirrored) | |

| 0x580 | 0x5FF | TG registers for Link 2 | |

| 0x600 | 0x67F | 3 | D-PHY IP registers for Link 3 |

| 0x680 | 0x6FF | D-PHY IP shared (mirrored) | |

| 0x700 | 0x77F | TG top level registers mirrored across all links (mirrored) | |

| 0x780 | 0x7FF | TG registers for Link 3 | |

| 0x800 | 0x87F | 4 | D-PHY IP registers for Link 4 |

| 0x880 | 0x88F | D-PHY IP shared (mirrored) | |

| 0x900 | 0x97F | TG top level registers mirrored across all links (mirrored) | |

| 0x980 | 0x9FF | TG registers for Link 4 | |

| 0xA00 | 0xA7F | 5 | D-PHY IP registers for Link 5 |

| 0xA80 | 0xAFF | D-PHY IP shared (mirrored) | |

| 0xB00 | 0xB7F | TG top level registers mirrored across all links (mirrored) | |

| 0xB80 | 0xBFF | TG registers for Link 5 | |

| 0xC00 | 0xC7F | 6 | D-PHY IP registers for Link 6 |

| 0xC80 | 0xCFF | D-PHY IP shared (mirrored) | |

| 0xD00 | 0xD7F | TG top level registers mirrored across all links (mirrored) | |

| 0xD80 | 0xDFF | TG registers for Link 6 |

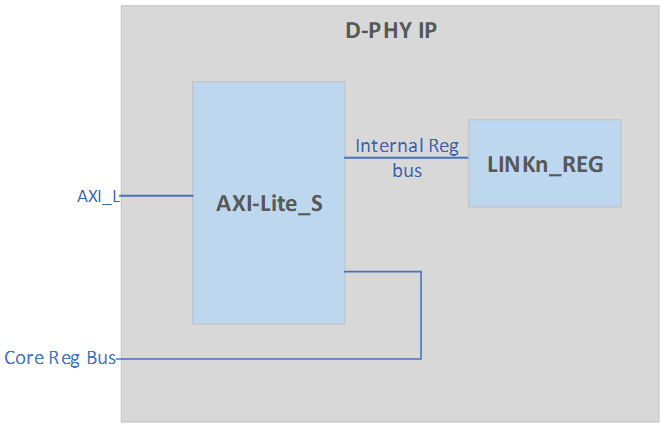

The external register space is accessed using a simple register bus as shown below:

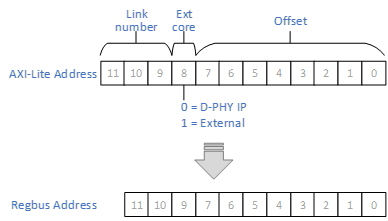

The AXI-Lite client on the D-PHY IP does sub-decode by looking at bit[8] of the AXI-Lite address. The register bus address bits are mapped as shown below:

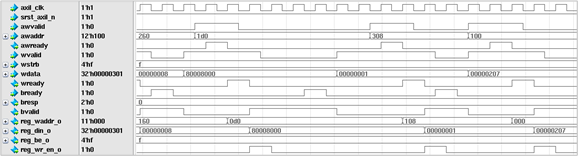

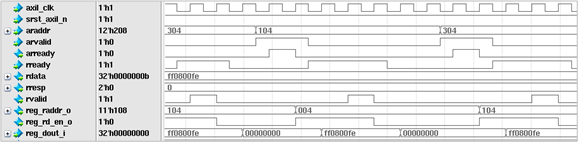

The waveform diagram below shows AXI-Lite write and read to external registers: