Visible to Intel only — GUID: tai1705946035853

Ixiasoft

Visible to Intel only — GUID: tai1705946035853

Ixiasoft

5.7. Pulse Synchronizer Parameterizable Macro (ipm_cdc_pulse_sync)

For proper operation, you must sample the input data two or more times by the destination clock. You can define the number of register stages used in the synchronizers.

This macro also requires the following minimum gap between subsequent pulse inputs:

2 *larger clock period of src_clk or dst_clk

The Quartus® Prime software measures the minimum gap between the falling edge of src_pulse to the rising edge of the next src_pulse . You must assert src_rst and dst_rst simultaneously for at least the following duration to fully reset all logic in the macro:

((NUM_STAGES +2) *dst_clk period) + (2*src_clk period)

When you assert reset, the input pulse signal should not toggle, and the output pulse signal is not valid and you can ignore the output pulse signal.

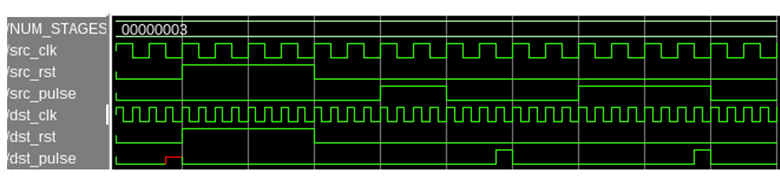

The following waveform demonstrates how to reset the macro and transfer back-to-back pulses with minimum gap between each pulse: