Intel® FPGA SDK for OpenCL™ Pro Edition: Programming Guide

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: wwk1597930724368

Ixiasoft

Visible to Intel only — GUID: wwk1597930724368

Ixiasoft

9.2.2.1. Creating a Project

Perform the following steps to create a project using Eclipse CDT:

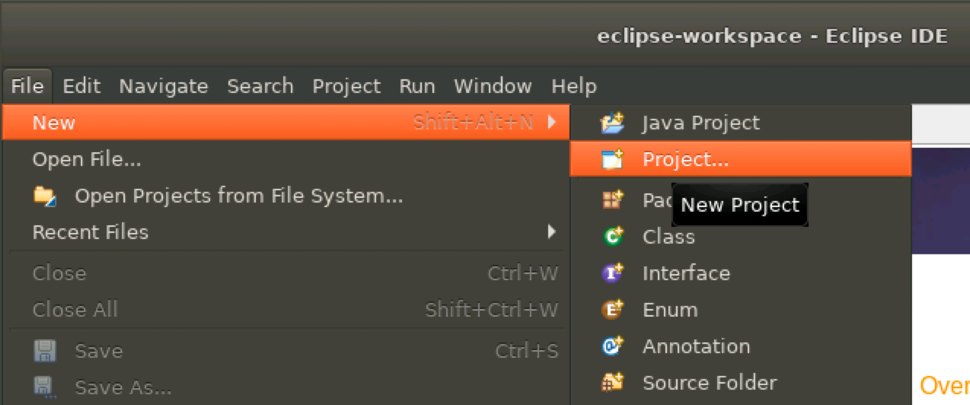

- Select File > New > Project menu option.

Figure 19. Eclipse CDT File Menu

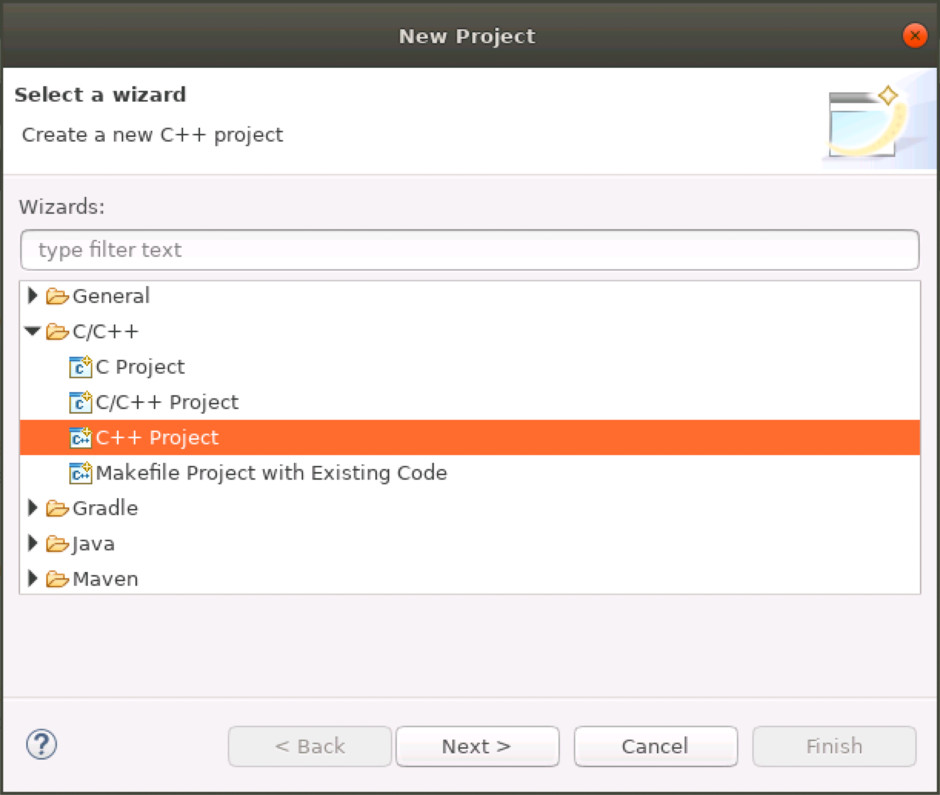

- Select the type of project you want to create. For this tutorial, expand the C/C++ folder, select C++ Project, and click the Next button.

Figure 20. New Project Wizard

The C++ Project wizard opens. By default, the CDT filters the Project Type and Toolchain based on the language supported for the C++ Project wizard you selected for this tutorial.

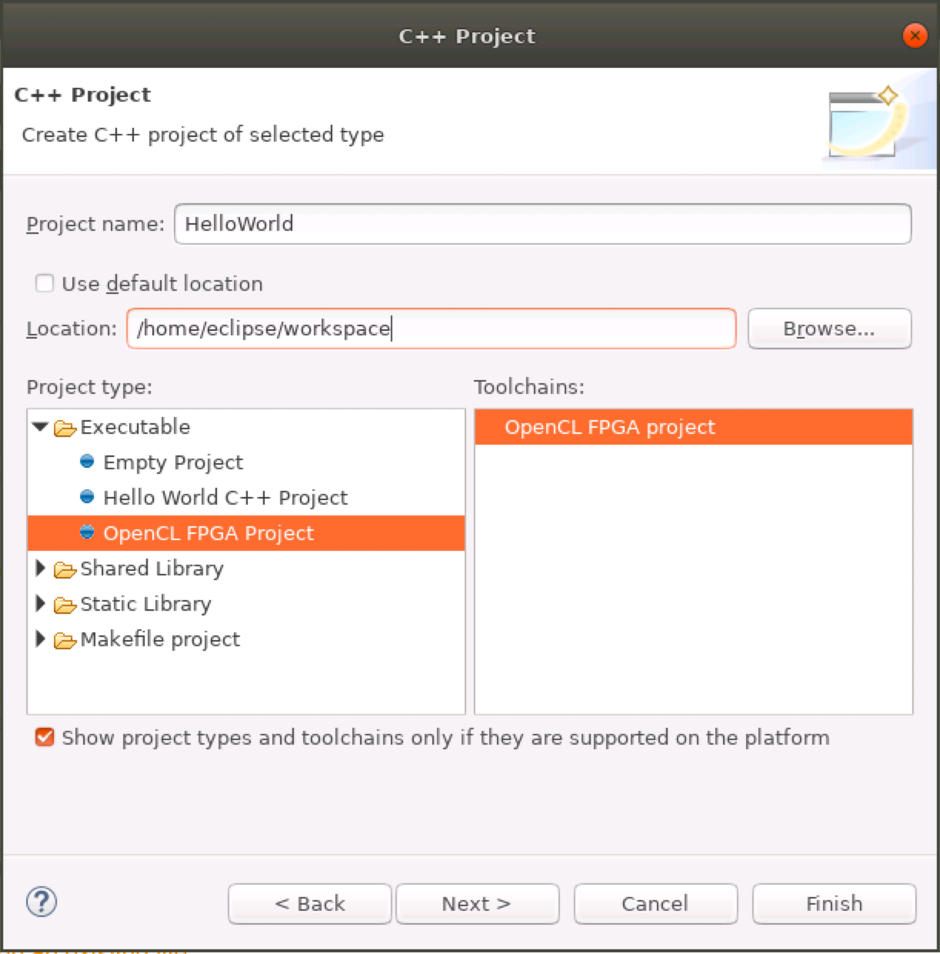

The C++ Project wizard opens. By default, the CDT filters the Project Type and Toolchain based on the language supported for the C++ Project wizard you selected for this tutorial. - In the C++ Project wizard, perform these steps:

Figure 21. C++ Project Wizard

- In the Project name field, type a name for the project. For example, HelloWorld.

- In the Project type list, expand Executable folder and select OpenCL FPGA Project. This project type provides a simple Hello World application in OpenCL and the makefile is automatically created by the CDT.

- Under Toolchains, select OpenCL FPGA project.

- Click the Next button.

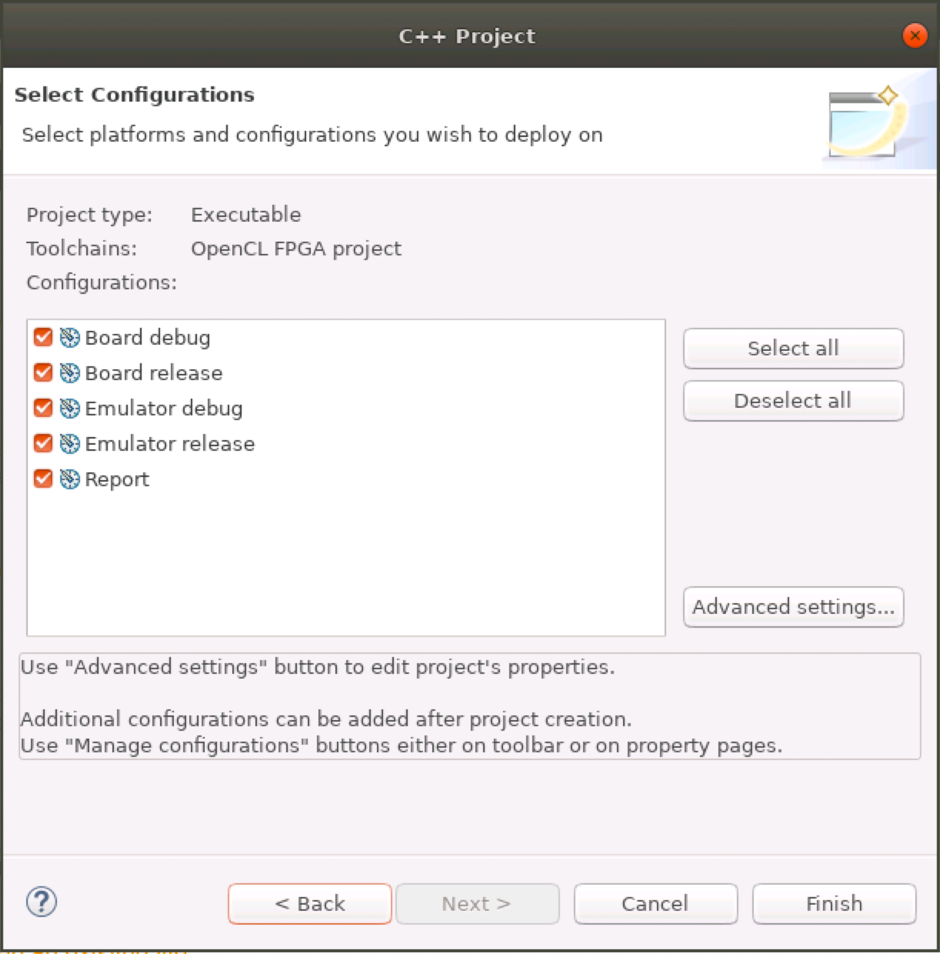

The Select Configurations dialog box displays a list of configurations based on the project type and toolchain selected earlier.Figure 22. Select Configurations Dialog Note: Board debug and Board release configuration options are equivalent to HW Debug and HW Release build target options in the Microsoft Visual Studio IDE. When you use these options, board compiles for hardware and executes on a board.

Note: Board debug and Board release configuration options are equivalent to HW Debug and HW Release build target options in the Microsoft Visual Studio IDE. When you use these options, board compiles for hardware and executes on a board. - Optional: If you want to change the default project settings, click the Advanced settings button. The Project Properties dialog launches for your new project, allowing you to change any of the project specific settings, such as includes paths, compiler options, and libraries.

- Click the Finish button.

Note: If the C++ perspective is not currently set as the default, you are prompted to determine if you want this project to be associated with the C/C++ perspective. Click Yes.

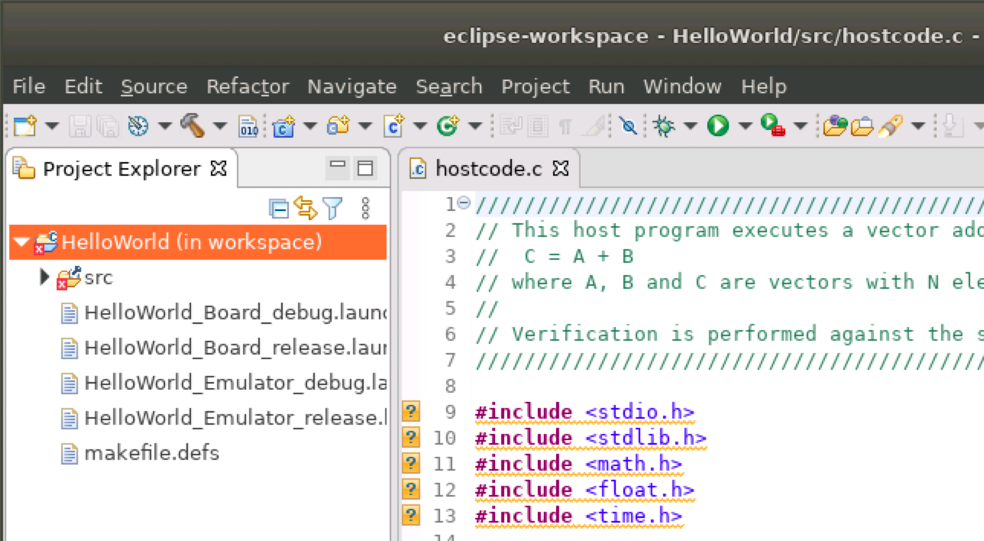

A project is created with the default settings and a full set of configurations based on the project type and toolchain you selected. You should now see the new project in the Project Explorer view.