Visible to Intel only — GUID: lro1432741036872

Ixiasoft

1.5.1. Nios II Booting General Flow

1.5.2. Summary of Nios II Processor Vector Configurations and BSP Settings

1.5.3. Nios II Processor Application Execute-In-Place from CFI Flash

1.5.4. Nios II Processor Application Copied from CFI Flash to RAM Using Boot Copier

1.5.5. Nios II Processor Application Copied from EPCS Flash to RAM Using Boot Copier

Visible to Intel only — GUID: lro1432741036872

Ixiasoft

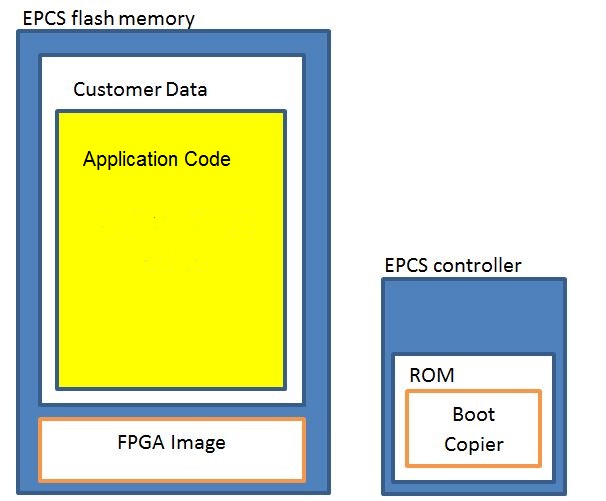

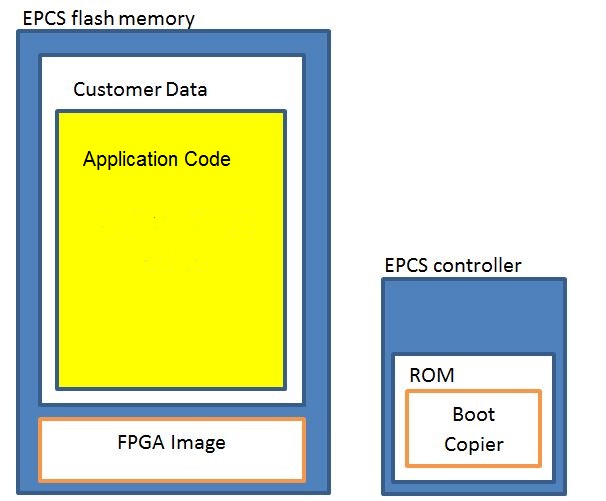

1.4.2. EPCS Controller-Based Boot Copier

EPCS controller-based boot copier supports EPCS memory only. Boot copier is stored in the ROM within the EPCS flash controller. The boot copier is included during Qsys and Quartus Prime project compilation time.

The next stage boot image is located in the EPCS memory flash. The EPCS controller-based boot copier is automatically appended into the SREC image (*.flash) file during the elf2flash utility execution in the Nios II Flash Programming flow method.

Figure 3. Memory Map for EPCS Flash with EPCS Controller-based Bootcopier

Note: Quartus Prime and Nios II Flash programming flow is briefly described in the Nios II Booting General Flow diagram.

Related Information