Visible to Intel only — GUID: uku1533001518481

Ixiasoft

1. Stratix® 10 Configuration User Guide

2. Stratix® 10 Configuration Details

3. Stratix® 10 Configuration Schemes

4. Including the Reset Release Intel® FPGA IP in Your Design

5. Remote System Update (RSU)

6. Stratix® 10 Configuration Features

7. Stratix® 10 Debugging Guide

8. Stratix® 10 Configuration User Guide Archives

9. Document Revision History for the Stratix® 10 Configuration User Guide

2.1. Stratix® 10 Configuration Timing Diagram

2.2. Configuration Flow Diagram

2.3. Device Response to Configuration and Reset Events

2.4. Additional Clock Requirements for HPS, PCIe* , eSRAM, and HBM2

2.5. Stratix® 10 Configuration Pins

2.6. Configuration Clocks

2.7. Maximum Configuration Time Estimation

2.8. Generating Compressed .sof File

2.9. Dual-die Configuration on Stratix® 10 GX 10M

3.1.1. Avalon® -ST Configuration Scheme Hardware Components and File Types

3.1.2. Enabling Avalon-ST Device Configuration

3.1.3. The AVST_READY Signal

3.1.4. RBF Configuration File Format

3.1.5. Avalon-ST Single-Device Configuration

3.1.6. Debugging Guidelines for the Avalon® -ST Configuration Scheme

3.1.7. IP for Use with the Avalon® -ST Configuration Scheme: Parallel Flash Loader II Intel® FPGA IP (PFL II)

3.1.7.1. Functional Description

3.1.7.2. Designing with the Parallel Flash Loader II Intel® FPGA IP for Avalon-ST Single Device Configuration

3.1.7.3. Generating the Parallel Flash Loader II Intel® FPGA IP

3.1.7.4. Constraining the Parallel Flash Loader II Intel® FPGA IP

3.1.7.5. Using the Parallel Flash Loader II Intel® FPGA IP

3.1.7.6. Supported Flash Memory Devices

3.1.7.3.1. Controlling Avalon-ST Configuration with Parallel Flash Loader II Intel® FPGA IP

3.1.7.3.2. Mapping Parallel Flash Loader II Intel® FPGA IP and Flash Address

3.1.7.3.3. Creating a Single Parallel Flash Loader II Intel® FPGA IP for Programming and Configuration

3.1.7.3.4. Creating Separate Parallel Flash Loader II Intel® FPGA IP Functions

3.1.7.4.1. Parallel Flash Loader II Intel® FPGA IP Recommended Design Constraints to FPGA Avalon-ST Pins

3.1.7.4.2. Parallel Flash Loader II Intel® FPGA IP Recommended Design Constraints for Using QSPI Flash

3.1.7.4.3. Parallel Flash Loader II Intel® FPGA IP Recommended Design Constraints for using CFI Flash

3.1.7.4.4. Parallel Flash Loader II Intel® FPGA IP Recommended Constraints for Other Input Pins

3.1.7.4.5. Parallel Flash Loader II Intel® FPGA IP Recommended Constraints for Other Output Pins

3.2.1. AS Configuration Scheme Hardware Components and File Types

3.2.2. AS Single-Device Configuration

3.2.3. AS Using Multiple Serial Flash Devices

3.2.4. AS Configuration Timing Parameters

3.2.5. Skew Tolerance Guidelines

3.2.6. Programming Serial Flash Devices

3.2.7. Serial Flash Memory Layout

3.2.8. AS_CLK

3.2.9. Active Serial Configuration Software Settings

3.2.10. Quartus® Prime Programming Steps

3.2.11. Debugging Guidelines for the AS Configuration Scheme

5.1. Remote System Update Functional Description

5.2. Guidelines for Performing Remote System Update Functions for Non-HPS

5.3. Commands and Responses

5.4. Quad SPI Flash Layout

5.5. Generating Remote System Update Image Files Using the Programming File Generator

5.6. Remote System Update from FPGA Core Example

5.7. Debugging Guidelines for RSU Configuration

5.6.1. Prerequisites

5.6.2. Creating Initial Flash Image Containing Bitstreams for Factory Image and One Application Image

5.6.3. Programming Flash Memory with the Initial Remote System Update Image

5.6.4. Reconfiguring the Device with an Application or Factory Image

5.6.5. Adding an Application Image

5.6.6. Removing an Application Image

7.1. Configuration Debugging Checklist

7.2. Stratix® 10 Configuration Architecture Overview

7.3. Understanding Configuration Status Using quartus_pgm command

7.4. SDM Debug Toolkit Overview

7.5. Configuration Pin Differences from Previous Device Families

7.6. Configuration File Format Differences

7.7. Understanding SEUs

7.8. Reading the Unique 64-Bit CHIP ID

7.9. E-Tile Transceivers May Fail To Configure

7.10. Understanding and Troubleshooting Configuration Pin Behavior

7.11. Configuration Debugger Tool

Visible to Intel only — GUID: uku1533001518481

Ixiasoft

5.6.3. Programming Flash Memory with the Initial Remote System Update Image

You can program the initial remote system update image from the command line. In the following command, substitute your .jic for output_file.jic if necessary.

quartus_pgm -c 1 -m jtag -o "pvi;./output_file.jic"

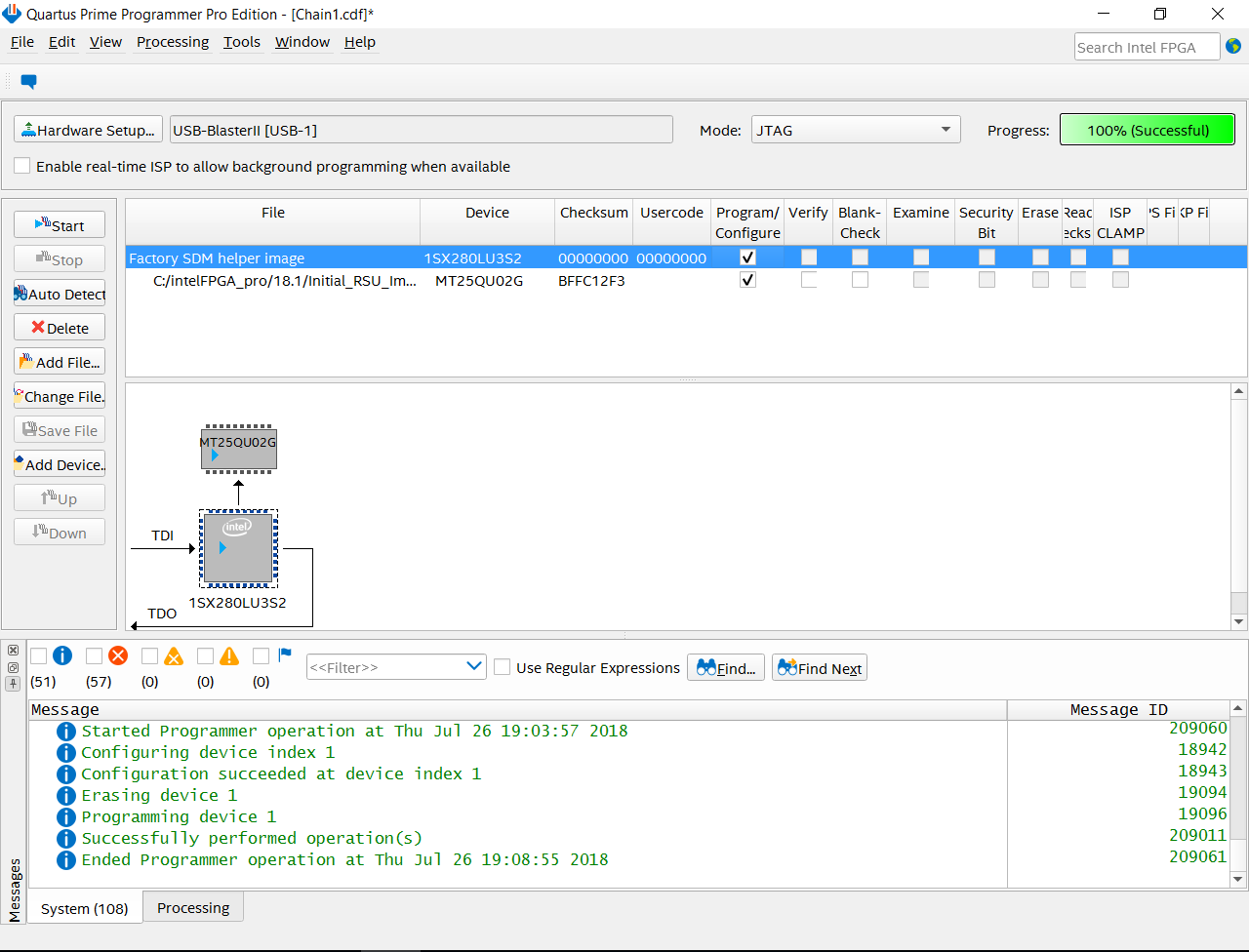

Alternatively, you can use the Quartus® Prime Programmer to program the initial RSU update image by completing the following procedure:

- Open the Programmer and click Add File. Select the generated .jic file (output_file.jic) and click Open.

- Select the checkbox for the Program/Configure for the attached .jic file.

- To begin programming the flash memory with the initial remote system update image, click Start.

- Configuration is complete when the progress bar reaches 100%. Power cycle the board to automatically configure the Stratix® 10 device with the application image using the AS x4 configuration scheme.

Figure 85. Programming the Flash Memory with the Initial RSU Image

Note: This example does not assign the Direct to Factory Image pin. Consequently, the Programmer configures the device with the application image. The application image is the default image if the design does not use the Direct to Factory Image pin.

Note: This example does not assign the Direct to Factory Image pin. Consequently, the Programmer configures the device with the application image. The application image is the default image if the design does not use the Direct to Factory Image pin. - Use the RSU_STATUS command to determine which bitstream image the Programmer is using as shown in the following example:

- In the Quartus® Prime software, select Tools > System Debugging Tools > System Console to launch the system console.

- In the Tcl Console pane, type source rsu1.tcl to open the example of Tcl script to perform the remote system update commands. Refer to the Related Information for a link to rsu1.tcl.

- Type the rsu_status command to report the current remote system update status. You can retrieve the current running image address from the remote system update status report. The current image address must match the start address for the application image printed in the .map file.

Figure 86. Running Tcl Commands Available in rsu1.tcl

Related Information