E-Tile JESD204C Intel Agilex® 7 FPGA IP Design Example User Guide

ID

683702

Date

12/21/2023

Public

Visible to Intel only — GUID: nxx1550759995541

Ixiasoft

1. About the E-Tile JESD204C Intel Agilex® 7 FPGA IP Design Example User Guide

2. JESD204C Intel® FPGA IP Design Example Quick Start Guide

3. Detailed Description for the JESD204C Design Example

4. E-Tile JESD204C Intel Agilex® 7 FPGA IP Design Example User Guide Archives

5. Document Revision History for the E-Tile JESD204C Intel Agilex® 7 FPGA IP Design Example User Guide

Visible to Intel only — GUID: nxx1550759995541

Ixiasoft

2.4. Compiling and Simulating the Design

The design example testbench simulates your generated design.

To simulate the design, perform the following steps:

- Change the working directory to <example_design_directory>/simulation/<Simulator>.

- In the command line, run the simulation script. The table below shows the commands to run the supported simulators.

Simulator Command ModelSim*

QuestaSim*

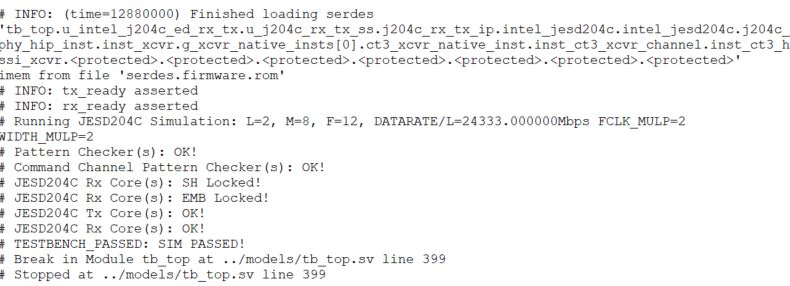

vsim -do modelsim_sim.tcl vsim -c -do modelsim_sim.tcl (without ModelSim* or QuestaSim* GUI) VCS* sh vcs_sim.sh VCS* MX sh vcsmx_sim.sh Xcelium* Parallel sh xcelium_sim.sh The simulation ends with messages that indicate whether the run was successful or not.Figure 4. Successful SimulationThe average simulation run time including design elaboration is approximately 8 minutes on VCS* , and 26 minutes on ModelSim* - Intel® FPGA Starter Edition for preset with L=2, M=8, and F=12.