Visible to Intel only — GUID: mwh1410471330960

Ixiasoft

Visible to Intel only — GUID: mwh1410471330960

Ixiasoft

3.2.1. WYSIWYG Primitive Resynthesis

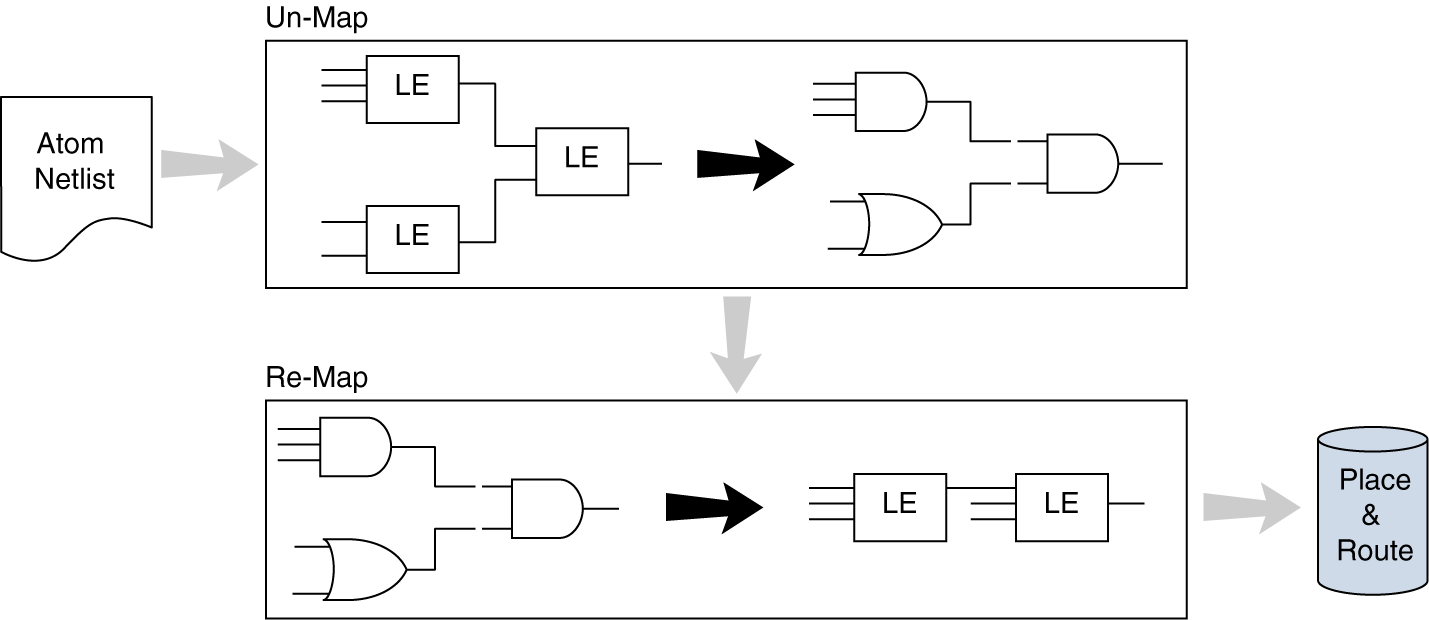

The Perform WYSIWYG primitive resynthesis option directs the Quartus® Prime software to un-map the logic elements (LEs) in an atom netlist to logic gates, and then re-map the gates back to Intel-specific primitives. Third-party synthesis tools generate either an .edf or .vqm atom netlist file using Intel-specific primitives. When you turn on the Perform WYSIWYG primitive resynthesis option, the Quartus® Prime software uses device-specific techniques during the re-mapping process. This feature re-maps the design using the Optimization Technique specified for your project (Speed, Area, or Balanced).

The Perform WYSIWYG primitive resynthesis option unmaps and remaps only logic cells, also referred to as LCELL or LE primitives, and regular I/O primitives (which may contain registers). Double data rate (DDR) I/O primitives, memory primitives, digital signal processing (DSP) primitives, and logic cells in carry chains are not remapped. This process does not process logic specified in an encrypted .vqm file or an .edf file, such as third-party intellectual property (IP).

The Perform WYSIWYG primitive resynthesis option can change node names in the .vqm file or .edf file from your third-party synthesis tool, because the primitives in the atom netlist are broken apart and then re-mapped by the Quartus® Prime software. The re-mapping process removes duplicate registers. Registers that are not removed retain the same name after re-mapping.

Any nodes or entities that have the Netlist Optimizations logic option set to Never Allow are not affected during WYSIWYG primitive resynthesis. You can use the Assignment Editor to apply the Netlist Optimizations logic option. This option disables WYSIWYG resynthesis for parts of your design.

If you use the Quartus® Prime software to synthesize your design, you can use the Preserve Register (preserve) and Keep Combinational Logic (keep) attributes to maintain certain nodes in the design.