Intel® Quartus® Prime Pro Edition User Guide: Platform Designer

A newer version of this document is available. Customers should click here to go to the newest version.

Visible to Intel only — GUID: cbn1505151723396

Ixiasoft

Visible to Intel only — GUID: cbn1505151723396

Ixiasoft

4.3.5. Defining HDL Parameters in _hw.tcl

- To define an alterable HDL parameter, you must declare the following two attributes for the parameter:

- set_parameter_property <parameter_name> HDL_PARAMETER true

- set_parameter_property <parameter_name> AFFECTS_GENERATION false

- To have parameterized ports created in the instantiation wrapper, you can either set the width expression when adding a port to an interface, or set the width expression in the port property in _hw.tcl:

-

To set the width expression when adding a port:

add_interface_port <interface> <port> <signal_type> <direction> <width_expression> -

To set the width expression in the port property:

set_port_property <port> WIDTH_EXPR <width_expression>

-

- To create and generate the IP component in Platform Designer editor, click the Open System > IP Variant tab, specify the new IP variant name in the IP Variant field and choose the _hw.tcl file that defines user alterable HDL parameters in the Component type field.

- Click Generate HDL to generate the IP core. Platform Designer generates a parameterized HDL module for you directly.

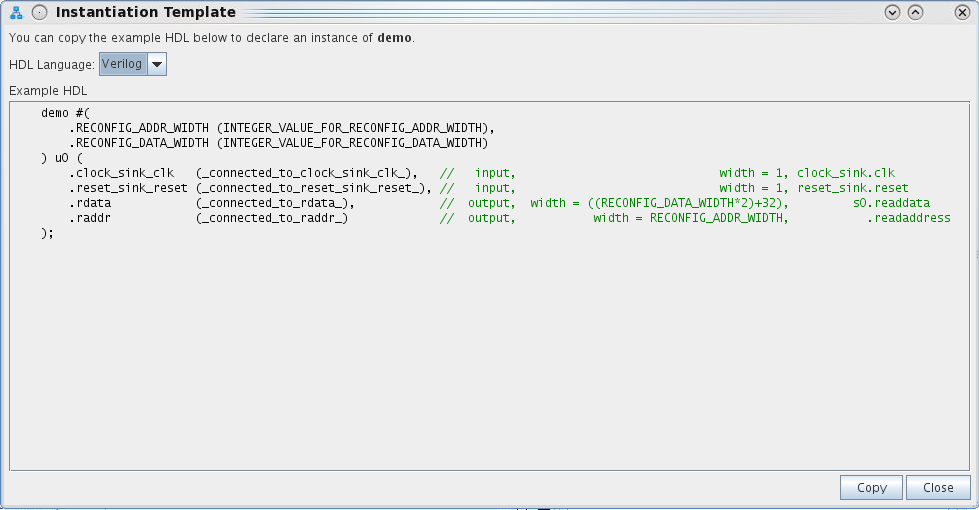

To instantiate the IP component in your HDL file, click Generate > Show Instantiation Template in the Platform Designer editor to display an instantiation template in Verilog or VHDL. Now you can instantiate the IP core in your top-level design HDL file with the template code.

The following sample contains _hw.tcl to set exportable width values:

Sample _hw.tcl Component with User Alterable Expressions

package require -exact qsys 17.1

set_module_property NAME demo

set_module_property DISPLAY_NAME "Demo"

set_module_property ELABORATION_CALLBACK elaborate

# add exportable hdl parameter RECONFIG_DATA_WIDTH

add_parameter RECONFIG_DATA_WIDTH INTEGER 48

set_parameter_property RECONFIG_DATA_WIDTH AFFECTS_GENERATION false

set_parameter_property RECONFIG_DATA_WIDTH HDL_PARAMETER true

# add exportable hdl parameter RECONFIG_ADDR_WIDTH

add_parameter RECONFIG_ADDR_WIDTH INTEGER 32

set_parameter_property RECONFIG_ADDR_WIDTH AFFECTS_GENERATION false

set_parameter_property RECONFIG_ADDR_WIDTH HDL_PARAMETER true

# add non-exportable hdl parameter

add_parameter l_addr INTEGER 32

set_parameter l_addr HDL_PARAMETER false

# add interface

add_interface s0 conduit end

proc elaborate {} {

add_interface_port s0 rdata readdata output "reconfig_data_width*2 + l_addr"

add_interface_port s0 raddr readaddress output [get_parameter_value RECONFIG_ADDR_WIDTH]

set_port_property raddr WIDTH_EXPR "RECONFIG_ADDR_WIDTH"

}