Intel® Quartus® Prime Pro Edition User Guide: Platform Designer

A newer version of this document is available. Customers should click here to go to the newest version.

5.2. Using Hierarchy in Systems

Hierarchy can simplify verification control of agents connected to each host in a memory-mapped system. Before you implement subsystems in your design, you should plan the system hierarchical blocks at the top-level, using the following guidelines:

- Plan shared resources—Determine the best location for shared resources in the system hierarchy. For example, if two subsystems share resources, add the components that use those resources to a higher-level system for easy access.

- Plan shared address space between subsystems—Planning the address space ensures you can set appropriate sizes for bridges between subsystems.

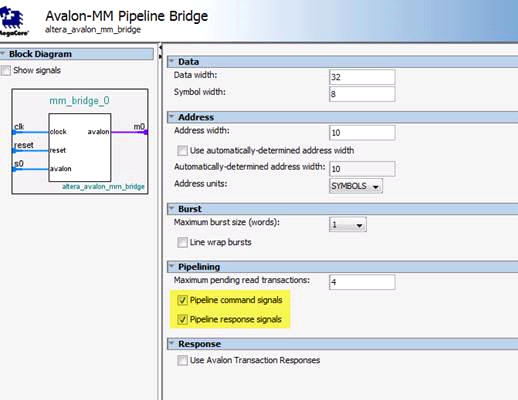

- Plan how much latency you may need to add to your system—When you add an Avalon® Memory Mapped Pipeline Bridge between subsystems, you may add latency to the overall system. You can reduce the added latency by parameterizing the bridge with zero cycles of latency, and by turning off the pipeline command and response signals.

Figure 114. Avalon® Memory Mapped Pipeline Bridge

In this example, two Nios® II processor subsystems share resources for message passing. Bridges in each subsystem export the Nios® II data host to the top-level system that includes the mutex (mutual exclusion component) and shared memory component (which could be another on-chip RAM, or a controller for an off-chip RAM device).

You can also design systems that process multiple data channels by instantiating the same subsystem for each channel. This approach is easier to maintain than a larger, non-hierarchical system. Additionally, such systems are easier to scale because you can calculate the required resources as a multiple of the subsystem requirements.