Visible to Intel only — GUID: aet1512527999140

Ixiasoft

AN 838: Interoperability between Intel® Arria® 10 NBASE-T Ethernet Solution and Aquantia Ethernet PHY Reference Design

Getting Started Intel® Arria® 10 Multi Speed Ethernet Solution and Aquantia Ethernet PHY Reference Design

Generating the 10G USXGMII Ethernet Example Design

Reference Design Walk Through

Debugging the Reference Design

Document Revision History for AN 838: Interoperability between Intel® Arria® 10 NBASE-T Ethernet Solution and Aquantia Ethernet PHY Reference Design

Visible to Intel only — GUID: aet1512527999140

Ixiasoft

Running Basic Packet Transfer

Follow these steps to run basic packet transfer using the reference design once the links between Intel 1G/2.5G/5G/10G Multi-rate Ethernet PHY and Aquantia AQR105 Ethernet PHY are successfully connected:

- Depending on which Intel® Arria® 10 GX Transceiver SI development kit you would like the loop back mechanism to be, enable the Avalon® ST interface loop back in the System Console using the following command:

SET_TRAFFIC_CONTROLLER_STD_CHANNEL_BASE_ADDR 1 SET_AVALON_ST_LOOPBACK_ENA - In the System Console from the Intel® Arria® 10 GX Transceiver SI development kit without the Avalon® ST interface loop back, use the following command to start packets transfer. This reference design connects channel 1 of the transceiver to the SFP+ interface.

TEST_EXT_LB <channel> <speed> <burst_size>.Example: TEST_EXT_LB 1 10G 80000000.

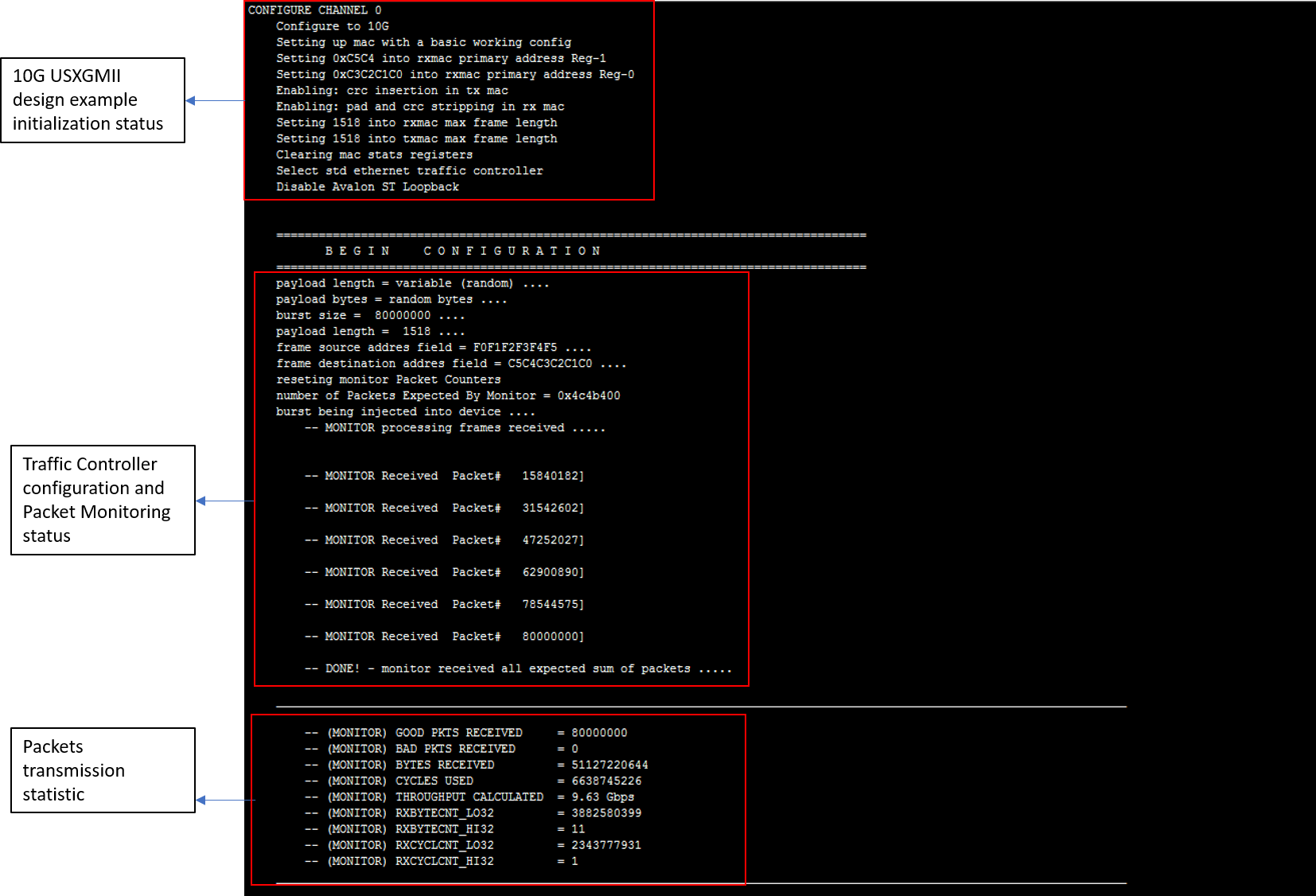

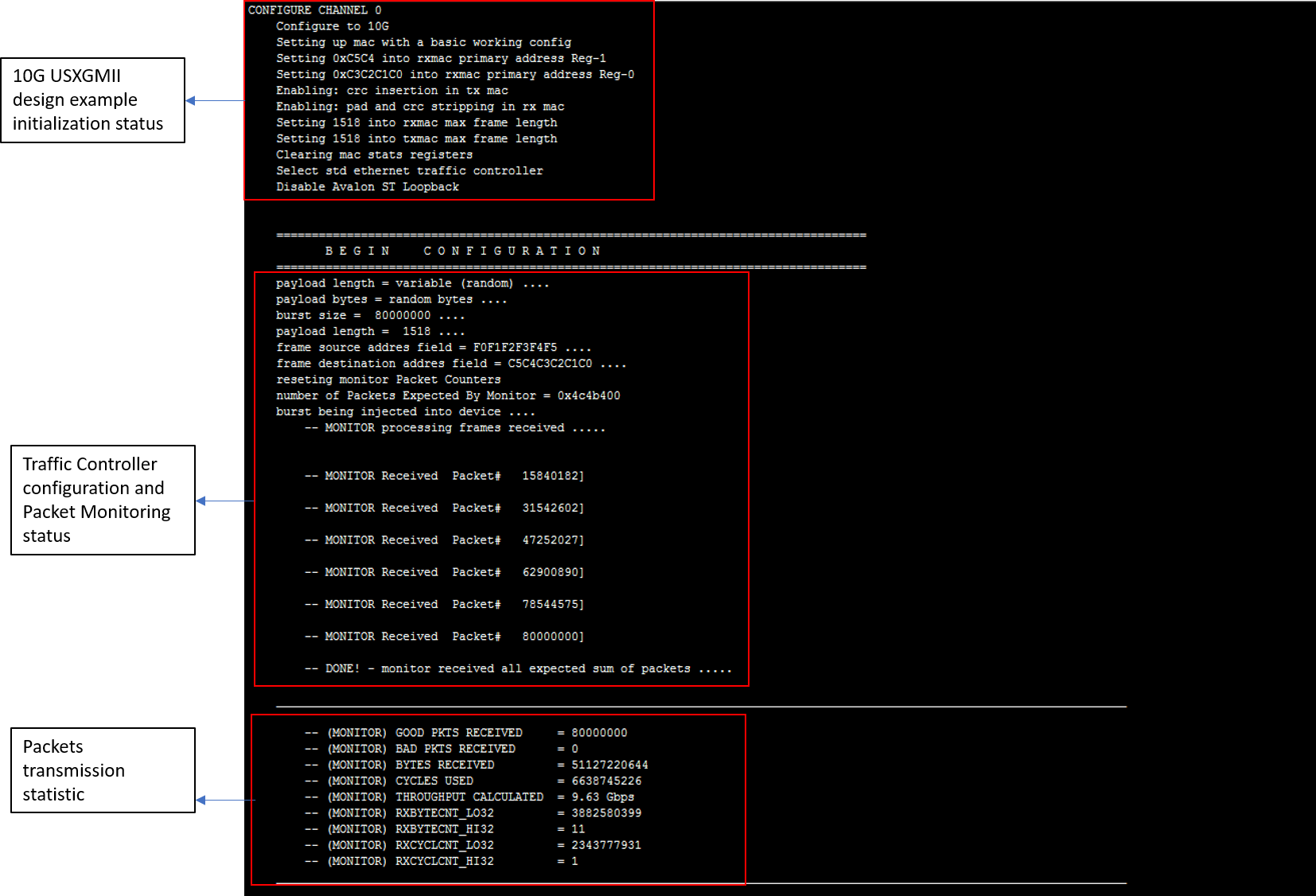

The following diagram shows an example of successful packets transfer during basic packet transfer test.

Figure 6. Example of Basic Transfer Test Result