Visible to Intel only — GUID: aet1634249574066

Ixiasoft

3.5.2.5.1. Build and Install Netdev Driver

3.5.2.5.2. Enable VFs if SRIOV is Supported

3.5.2.5.3. Configure the Number of Channels Supported on the Device

3.5.2.5.4. Configure the MTU Value

3.5.2.5.5. Configure the Device Communication

3.5.2.5.6. Configure Transmit Queue Selection Mechanism

3.5.2.5.7. Test Procedure by Using Name Space Environment

3.5.2.5.8. PIO Test

Visible to Intel only — GUID: aet1634249574066

Ixiasoft

For x4 BAS:

- Set the PCIe_SLOT “2” in rte_pmd_mcdma.h(dpdk/drivers/net/mcdma/rte_pmd_mcdma.h)

- X4 BAS supports burst length 32 by default. In the file perfq_app.h (dpdk/examples/mcdma-test/perfq/perfq_app.h)

#define IFC_MCDMA_BAS_X4_BURST_LENGTH 32

If the BAS support is enabled on hardware, enable the following flag in: dpdk/dpdk/drivers/net/mcdma/rte_pmd_mcdma.h

#define PCIe_SLOT 0 /* 0 – x16, 1 – x8, 2 - x4 */

To enable the config IFC_QDMA_INTF_AVST in the file "software/dpdk/dpdk/patches/v20.05-rc1/dpdk/drivers/net/mcdma/base/mcdma_ip_params.h", use the following command:

#undef IFC_QDMA_INTF_AVST

Commands:

- To verify the write operation:

./build/mcdma-test -- -b 0000:01:00.0 --bar=0 --bas -s 512 -t

Figure 42. BAS Write Operation

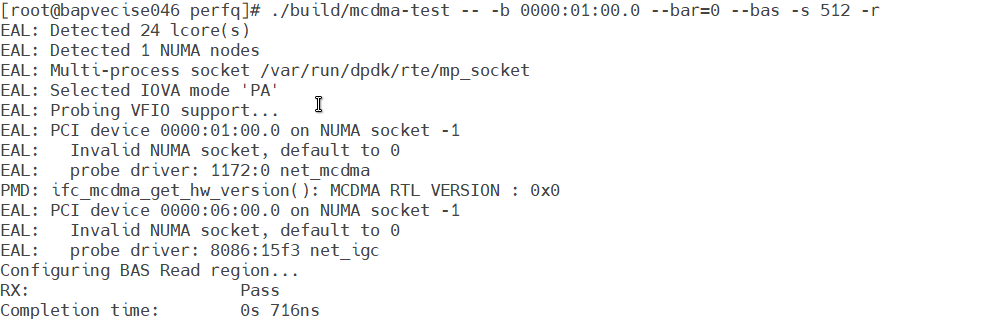

- To verify the read operation:

./build/mcdma-test -- -b 0000:01:00.0 --bar=0 --bas -s 512 -r

Figure 43. BAS Read Operation

- To verify the write and read operation:

./build/mcdma-test -- -b 0000:01:00.0 --bar=0 --bas -s 512 -z

Figure 44. BAS Write and Read Operation

Performance test:

The below log is collected on Gen3x16 H-tile./build/mcdma-test -- -b 0000:01:00.0 --bar=0 --bas_perf -s 16384 -z

Figure 45. Performance Test Note: For DPDK: VF/PF cannot run BAM+BAS+MCDMA simultaneously within one VM or hypervisor, You need to run one instance of VF / PF in independent VM.

Note: For DPDK: VF/PF cannot run BAM+BAS+MCDMA simultaneously within one VM or hypervisor, You need to run one instance of VF / PF in independent VM.