Visible to Intel only — GUID: djk1490922139168

Ixiasoft

Visible to Intel only — GUID: djk1490922139168

Ixiasoft

A.1. Reviewing the Summary Report

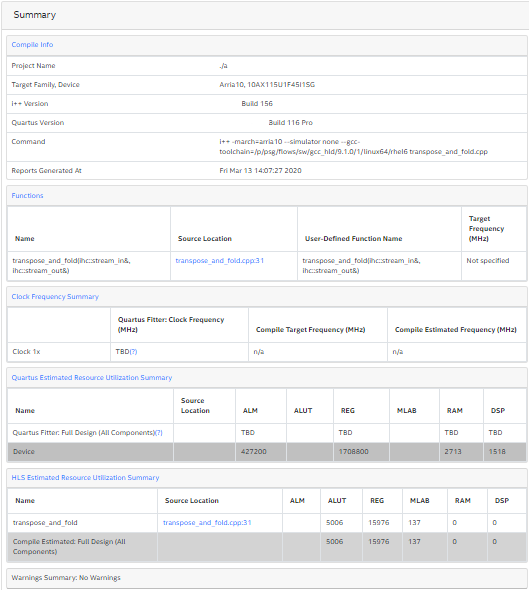

The Summary Report gives you a quick overview of the results of compiling your design including a summary of each component in your design and a summary of the estimated resources that each component in your design uses.

- Compile Info

- Functions

- Clock Frequency Summary

- Quartus Estimated Resource Utilization Summary

- HLS Estimated Resource Utilization Summary

- Warnings Summary

Compile Info

- Name of the project

- Target FPGA family and device

- HLS compiler version

- Intel® Quartus® Prime version

- The command that was used to compile the design

- The date and time at which the reports are generated

Functions

For overloaded and templated functions in your hardware design, this section of the Summary Report shows you the short names generated by the Intel® HLS Compiler for the functions to prevent name collisions.These short names are used in other parts of the High Level Design Report.

The Synthesized Function Name Mapping section does not show testbench functions. Only functions that are synthesizable to hardware are shown.

Clock Frequency Summary

- Quartus Fitter Clock Frequency

- Compiler Target Frequency (MHz)

- Compiler estimated frequency (MHz)

The Quartus Fitter clock frequency is the maximum clock frequency that can be achieved for the design. When the compiler estimates a lower frequency than the targeted frequency, the frequency value is highlighted in red.

Both the Functions section and Clock Frequency Summary display the target clock frequency applied at the source on the component. When the values of the source is different than the compilation flag you applied, the Clock Frequency Summary Compiler Target Frequency shows “Various” instead of reporting a number.

Quartus Estimated Resource Utilization Summary

After you compile your design with Intel® Quartus® Prime software, the Quartus Estimated Resource Utilization Summary section shows the total area utilization both for the entire design, and for each component individually. There is no breakdown of area information by source line.

Function Summary

When you compile your design to target Intel Agilex® 7 or Intel® Stratix® 10 devices, this section of the report indicates whether a function in your design uses a modified handshaking protocol.You can control the use of the modified handshaking protocol with the --hyper-optimized-handshaking option of the i++ command.

HLS Estimated Resource Utilization Summary

The HLS Estimated Resource Utilization Summary section shows a summary of the estimated resources used by each component in your design, as well as the total resources used for all components.

Warnings Summary

The Warnings Summary section shows the compiler warnings generated during the compilation.