Visible to Intel only — GUID: mkp1582302768237

Ixiasoft

Visible to Intel only — GUID: mkp1582302768237

Ixiasoft

11.4.1.2.1. RTL Module Interface Signals

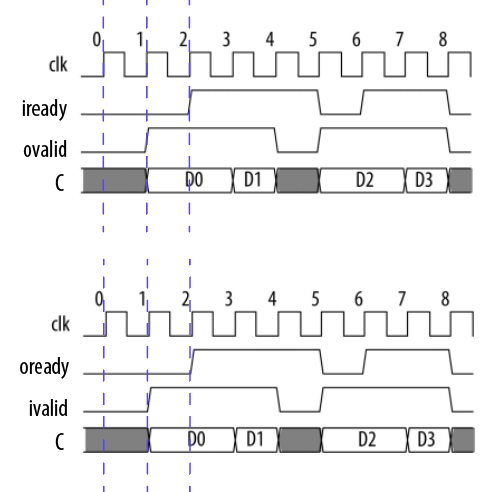

The Intel® HLS Compiler expects the RTL module to support a single interface with readyLatency = 0, at both input and output.

- ivalid and iready as the input ready/valid interface

- ovalid and oready as the output ready/valid interface

For an RTL module with a fixed latency, the output signals (ovalid and oready) can have constant high values, and the input ready signal (iready) can be ignored.

A stall-free RTL module might receive an invalid input signal (ivalid is low). In this case, the module ignores the input and produces invalid data on the output. For a stall-free RTL module without an internal state, it might be easier to propagate the invalid input through the module. However, for an RTL module with an internal state, you must handle an ivalid = 0 input carefully.

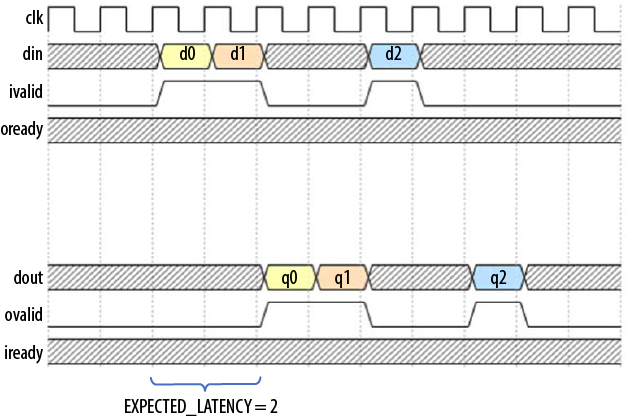

Example Timing Diagram of a Stall-free RTL Component

Consider the following example timing diagram of a stall-free RTL component:

- IS_STALL_FREE value = "yes"

- IS_FIXED_LATENCY value = "yes"

- EXPECTED_LATENCY value = "2"

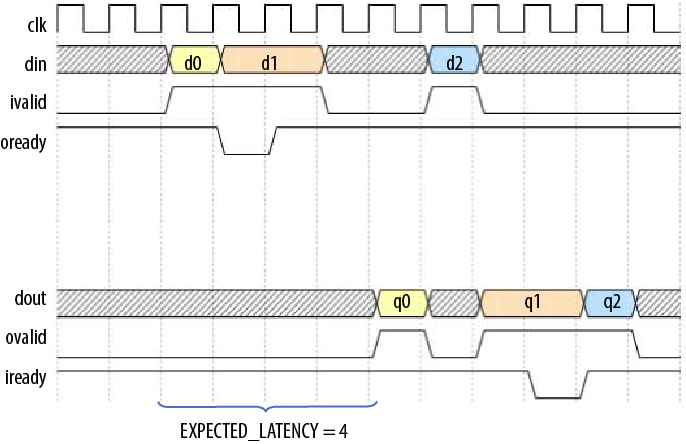

Example Timing Diagram of a Non-stall-free RTL Component

Consider the following example timing diagram of a non-stall-free RTL component:

- IS_STALL_FREE value = "no"

- IS_FIXED_LATENCY value = "no"

- EXPECTED_LATENCY value = "4"