DSP Builder for Intel® FPGAs (Advanced Blockset): Handbook

A newer version of this document is available. Customers should click here to go to the newest version.

3.1.2.8. Simulink vs Hardware Design Representations

In a typical wideband CDMA macro-cell system, the DUC module in the RF card needs to process eight inphase (I) and quadrature (Q) data pairs, resulting in 16 independent channels on the datapath. The input sample rate to a DUC is at sample rate 3.84 MHz as defined in the 3GPP specification. A high-performance FPGA running at 245.76 MHz typically maximizes parallel processing power.

| Signals | Clock Rate (MHz) | ChanCount | Data Sample Rate (MSPS) | Period | Data Signal Pattern | Interpolation Factor |

|---|---|---|---|---|---|---|

| Input to FIR1 | 245.76 | 16 | 3.48 | 64 | I1, I2, ...I8, Q1, ... Q8, zeros(1, 64–16) | 2 |

| Input to FIR2 | 245.76 | 16 | 7.68 | 32 | I1, I2, ...I8, Q1, ... Q8, zeros(1, 32–16) | 2 |

| Input to CIC | 245.75 | 16 | 15.36 | 16 | I1, I2, ...I8, Q1, ... Q8 | 8 |

| Output of CIC | 245.75 | 16 | 122.88 | 2 | I1, I2, I3, I4, I5, I6, I7, I8, Q1, Q2, Q3, Q4, Q5, Q6, Q7, Q8 | 8 |

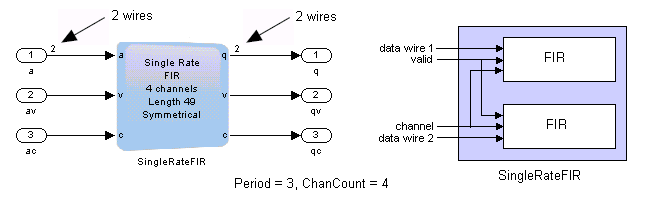

In this example, the input data at low sample rate 3.84 MSPS can accommodate all channels on a single wire. So the ChanWireCount is 1. In fact more time slots are available for processing, since period is 64 and only 16 channels are present to occupy the 64 time slots. Therefore the ChanCycleCount is 16, which is the number of cycles occupied on a wire. As the data travels down the up conversion chain, its sample rate increases and in turn period reduces to a smaller number. At the output of CIC filter, the data sample rate increases to 122.88 Msps, which means only two time slots are available on a wire. As there are 16 channels, spread them out on 8 wires, where each wire supports two channels. At this point, the ChanWireCount becomes 8, and ChanCycleCount becomes 2. The ChanCycleCount does not always equal period, as the input data to FIR1 shows.

For most systems, sample rate is less than clock rate, which gives WirePerChannel=1. In this case, ChanWireCount is the same as WireGroups, and it is the number of wires to accommodate all channels. In a super-sample rate system, a single channel's data needs to be split onto multiple wires. Use parallel signals at a clock rate to give an equivalent sample rate that exceeds the clock rate. In this case, WiresPerChannel is greater than one, and ChanWireCount = WireGroups × WiresPerChannel because one channel requires multiple wires.

When connecting two modules in DSP Builder, the output interface of the upstream module must have the same ChanWireCount and ChanCycleCount parameters as the input interface of the downstream module.