Visible to Intel only — GUID: efk1511996063310

Ixiasoft

Visible to Intel only — GUID: efk1511996063310

Ixiasoft

4.1.1. Pointer Interfaces

Pointers in a component are implemented as Avalon® Memory Mapped ( Avalon® -MM) host interfaces with default settings. For more details about pointer parameter interfaces, see Intel HLS Compiler Default Interfaces in Intel® High Level Synthesis Compiler Pro Edition Reference Manual.

component void vector_add(int* a,

int* b,

int* c,

int N) {

#pragma unroll 8

for (int i = 0; i < N; ++i) {

c[i] = a[i] + b[i];

}

}

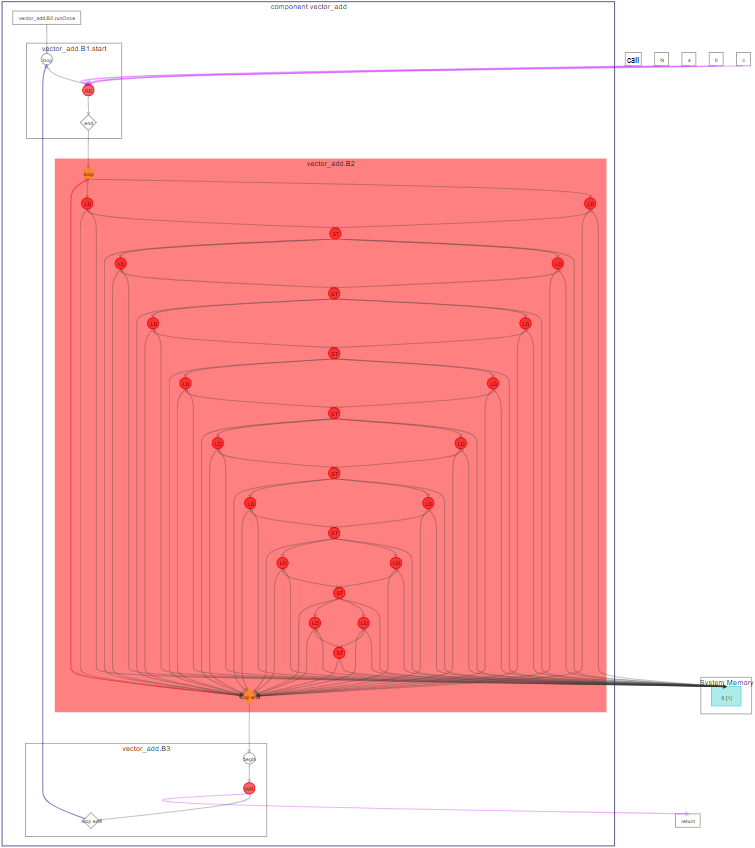

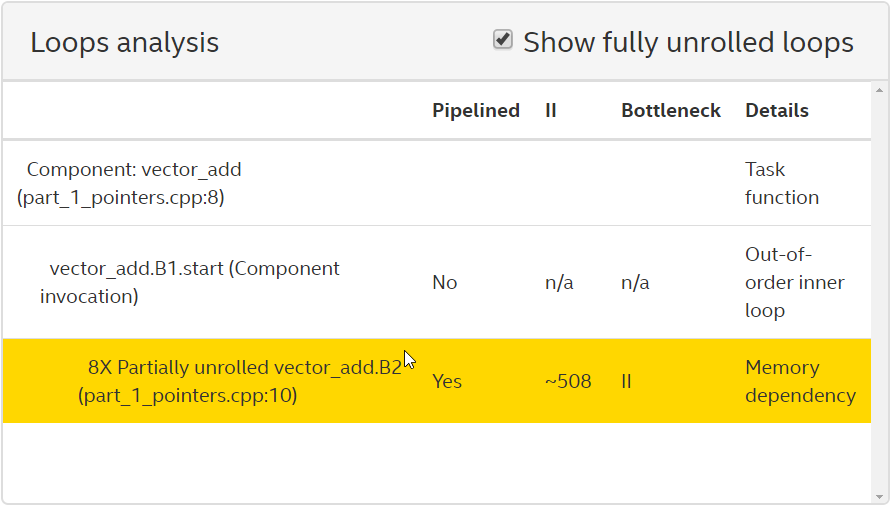

The following Loop Analysis report shows that the component has an undesirably high loop initiation interval (II). The II is high because vectors a, b, and c are all accessed through the same Avalon-MM Host interface. The Intel® HLS Compiler Pro Edition uses stallable arbitration logic to schedule these accesses, which results in poor performance and high FPGA area use.

In addition, the compiler cannot assume there are no data dependencies between loop iterations because pointer aliasing might exist. The compiler cannot determine that vectors a, b, and c do not overlap. If data dependencies exist, the Intel® HLS Compiler cannot pipeline the loop iterations effectively.

| QoR Metric | Value |

|---|---|

| ALMs | 15593.5 |

| DSPs | 0 |

| RAMs | 30 |

| fMAX (MHz)2 | 298.6 |

| Latency (cycles) | 24071 |

| Initiation Interval (II) (cycles) | ~508 |

| 1The compilation flow used to calculate the QoR metrics used Intel® Quartus® Prime Pro Edition Version 17.1. |

| 2The fMAX measurement was calculated from a single seed. |