Visible to Intel only — GUID: iga1457455310197

Ixiasoft

Visible to Intel only — GUID: iga1457455310197

Ixiasoft

38.7.3. Software Description

The software for the various example designs is very similar. For example, the difference between the software for the VIC Basic example and the software for the IIC example is the printf() call that generates the output to the terminal.

All of the software performs the following steps:

- Configures the timer used for measurement purposes

- Registers an interrupt service routine (ISR)

- Sets a global variable to 0xfeedface

- Starts the performance counter to measure the interrupt time

- Waits for the ISR to set the global variable to 0xfacefeed

- Stops the performance counter and computes the interrupt time

The VIC Daisy-Chain example performs the measurement for both VICs connected in the daisy chain, shown in Figure 139.

In all these design examples, the GCC compiler in Nios® II SBT tool is set to optimization level 2. Also, some settings are modified during BSP generation in order to reduce the code size. All these setting can be found in the create-this-bsp script included in the design example. Note that the number of clock cycles shows in these design examples will be differ from this document if the setting is different.

For details about how the VIC Table-Resident example code works, refer to “Positioning the ISR in the Vector Table”. For details about performance counter usage in the example software, refer to “Latency Measurement with the Performance Counter”.

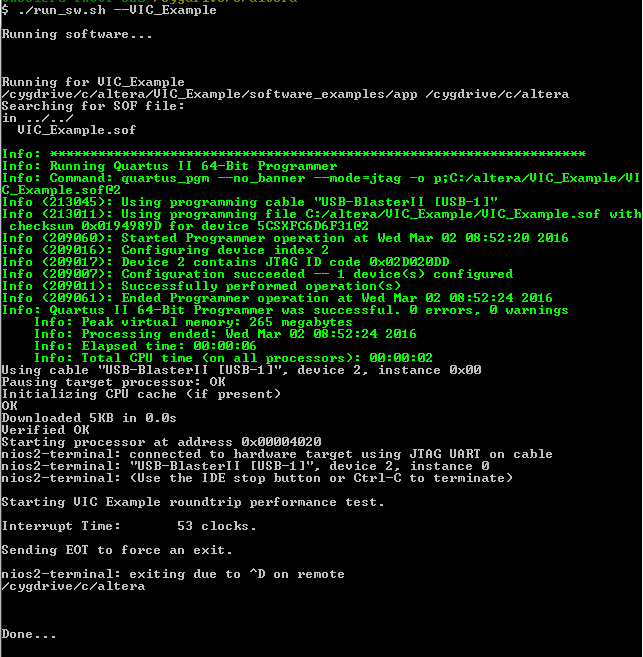

VIC Example