Visible to Intel only — GUID: zpo1628537166364

Ixiasoft

Visible to Intel only — GUID: zpo1628537166364

Ixiasoft

1.5.3. Mounting Inductance

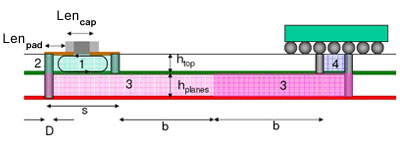

Mounting Inductance is the additional series inductance contribution associated with the mounting of the capacitor on the PCB. This parasitic inductance adds to the published ESL value that is provided by the cap vendor. Mounting inductance can be minimized by choosing smaller capacitor packages and performing proper layout of the capacitor on the PCB. Figure 3 shows the cross-section of a mounted decoupling capacitor in relation to the PCB planes and BGA device.

To estimate the mounting inductance, use the following equation:

- Lmnt = Ltrace + Lvia

Where,

- Ltrace = 128*[(2xLenpad)+Lencap]*(htop/w) pH

And,

- Lvia = 10*htop*ln(2s/D) ph

Where,

- Lenpad = Length of the capacitor pads plus trace length from pad to the via (mils)

- Lencap = Length of the capacitor body (mils)

- w = Width of the trace between the capacitor pad and via (mils)

- htop = Distance between the top layer and the nearest power/ground plane (mils)

- s = Distance between the capacitor's power via center and ground via center (mils)

- D = Outer diameter of the via (mils)

- hplanes = Distance between the power and ground plane (mils)

- b = Half the distance between the capacitor and the package power/ground vias (mils)

| Via Length (height above plane, inches) |

0603 footprint |

0603 footprint |

0603 footprint |

0603 footprint |

0402 footprint |

0402 footprint |

|---|---|---|---|---|---|---|

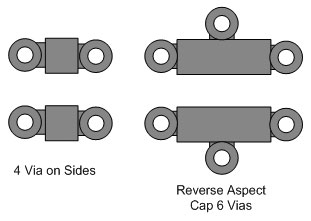

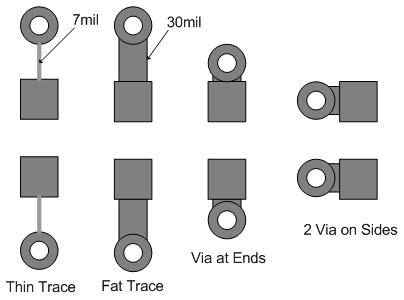

| 0.020 drill | Thin trace from pad to via | Short thick trace | Via on the end of pads | Via on the side of pads | Via on the end of pads | Via on one side of pads |

| 0.004 | 1.57 | 1.04 | 0.82 | 0.52 | 0.8 | 0.5 |

| 0.006 | 1.96 | 1.35 | 1.05 | 0.65 | 1 | 0.63 |

| 0.01 | 2.51 | 1.87 | 1.4 | 0.88 | 1.34 | 0.86 |

| 0.02 | 3.45 | 2.87 | 2.13 | 1.39 | 1.99 | 1.36 |

| 0.010 drill | ||||||

| 0.004 | 1.61 | 1.08 | 0.86 | 0.56 | 0.84 | 0.54 |

| 0.006 | 1.99 | 1.39 | 1.08 | 0.69 | 1.04 | 0.67 |

| 0.01 | 2.55 | 1.92 | 1.45 | 0.92 | 1.38 | 0.9 |

| 0.02 | 3.49 | 2.91 | 2.17 | 1.44 | 2.03 | 1.4 |