Intel® Quartus® Prime Standard Edition User Guide: Timing Analyzer

Visible to Intel only — GUID: mwh1442946322464

Ixiasoft

Visible to Intel only — GUID: mwh1442946322464

Ixiasoft

2.3.6.4. Create Timing Netlist

You must generate the timing netlist before running timing analysis. You can use the Create Timing Netlist dialog box or the Create Timing Netlist command in the Tasks pane. Create Timing Netlist also generates Advanced I/O Timing reports if you turn on Enable Advanced I/O Timing in the Timing Analyzer page of the Settings dialog box.

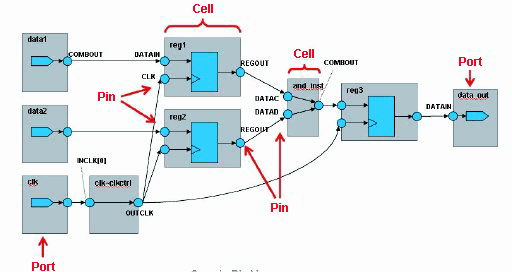

The following diagram shows how the Timing Analyzer interprets and classifies timing netlist data for a sample design.