Visible to Intel only — GUID: nht1638929263901

Ixiasoft

Visible to Intel only — GUID: nht1638929263901

Ixiasoft

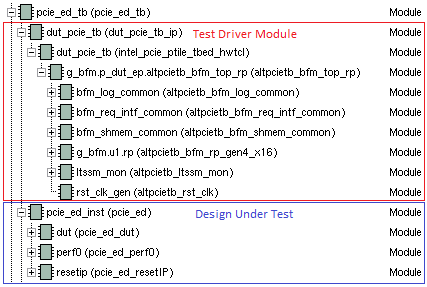

2.3.2.4. Performance Design Example Testbench

The figure below shows the Performance design example simulation design hierarchy. The tests for the Performance design example are defined with the apps_type_hwtcl parameter set to 3. The tests run under this parameter value are defined in ebfm_cfg_rp_ep_rootport, find_mem_bar and perf_ed_dma_write/perf_ed_dma_read.

- Issue a memory write command to set up the Performance design example's target memory write address.

- Issue a memory write command to trigger the Performance design example to send 10 memory writes with 128 bytes in length.

- Issue a memory write command to set up the Performance design example's target memory read address.

- Issue a memory write command to trigger the Performance design example to send 10 memory reads with 128 bytes in length.

The first memory write takes place around 205 us. The 10 memory writes and 10 memory reads with completions from the RP BFM appear shortly after the memory write requests at the Avalon-ST RX interface.