仅对英特尔可见 — GUID: vdw1520273647413

Ixiasoft

仅对英特尔可见 — GUID: vdw1520273647413

Ixiasoft

10.5. 优化数据路径控制

以下结构或功能特性会阻止英特尔 Stratix 10数据路径优化:

- 带有循环的NDRange设计

- 可停顿的LSU,突发合并(burst-coalesced)LSU除外

突发合并LSU是离线编译器例化的默认LSU类型。突发合并LSU例化的实例:

kernel void burst_coalesced (global int * restrict in, global int * restrict out){ int i = get_global_id(0); int value = in[i/2]; //Burst-coalesced LSU out[i] = value; }在System Viewer中,您可以将鼠标悬停在High Level Design Report中的加载或者存储操作上来查看各种指令中LSU的类型。请参阅Load-Store Units小节获得有关如何影响离线编译器例化LSU的类型的更多信息。

- 具有多个调用站点的通道

- 可停顿的RTL库调用

请参考创建RTL模块小节了解更多信息。

- 在已优化的控制流图中重新收敛控制流,使用新的控制优化的循环除外

以下是一个简单的重收敛控制流的伪代码实例,它显示了代码流入两条路径的其中一条。离线编译器对每个路径实现不同的控制逻辑。它还在两条路径完成后实现重新收敛控制流的逻辑。

while (some_some condition){ if (some_other_condition){ for(...){ } } else{ for(...){ } } } - 不使用新的循环控制方案的循环

请参阅循环控制优化小节来了解关于受该限制影响的循环的更多信息。

- 基本块结构,但以下情况除外:

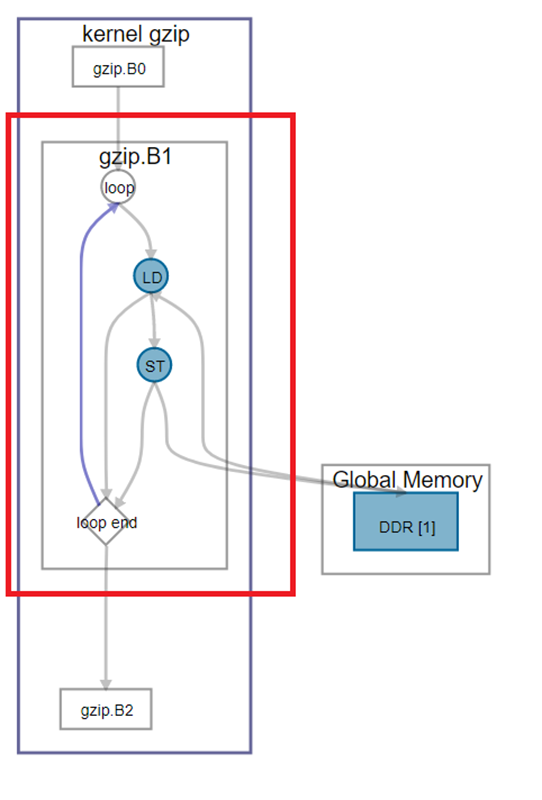

- 只有一个前驱(predecessor)的基本块,如图具有一个前驱的基本块结构所示

- 具有两个前驱的基本块,其中一个前驱是循环的后端,如具有两个前驱的基本块结构所示

注: 大多数优化的设计都属于两个受支持的基本块结构之一。您可以在High Level Design Report的System Viewer中查看这些基本块的图像。以下代码实例生成两种类型受支持的基本块结构:

__attribute__((max_global_work_dim(0))) void kernel basic_block(global unsigned int *myvar, unsigned int insize) { for(int i=0; i < insize; i++){ myvar[i] += insize; } }