# THE PARALEL UNDERSOR

# Heterogeneous Programming Using oneAPI

Accelerating Compression on Intel<sup>®</sup> FPGAs

Is Your Game GPU-Bound?

New Threading Capabilities in Julia v1.3

# CONTENTS

FEATURE

| Letter from the Editor<br>Happy New Year—and Welcome to the Era of oneAPI<br>by Henry A. Gabb, Senior Principal Engineer, Intel Corporation                                                                      | 3  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Heterogenous Programming Using oneAPI<br>How to Deliver Uncompromised Performance for Diverse Workloads Across Multiple Architectures                                                                            | 5  |

| Accelerating Compression on Intel <sup>®</sup> FPGAs<br>How oneAPI is Making FPGAs More Accessible than Ever                                                                                                     | 19 |

| Is Your Game GPU-Bound?<br>It's Easy to Find Out with a GPU and Device Context Queue Analysis                                                                                                                    | 29 |

| New Threading Capabilities in Julia v1.3<br>Unleashing the Full Power of Modern CPUs                                                                                                                             | 37 |

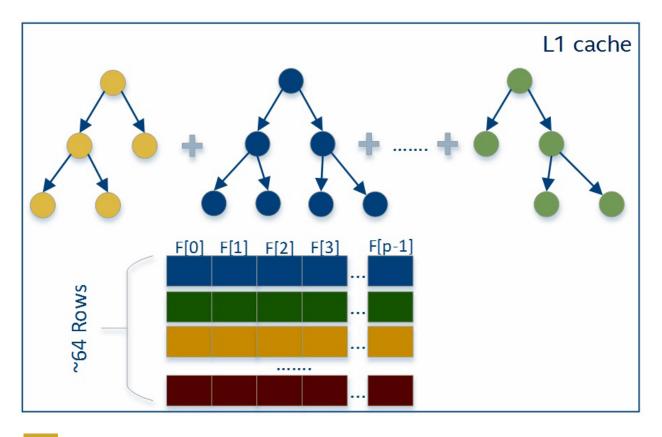

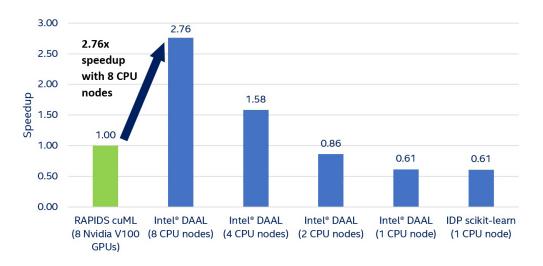

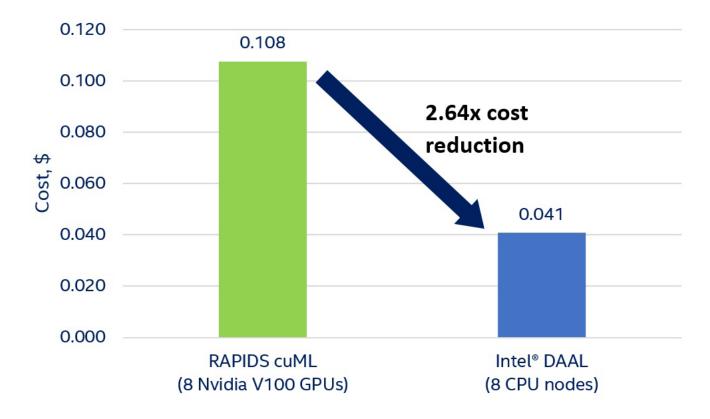

| Fast Gradient Boosting Tree Inference for Intel <sup>®</sup> Xeon <sup>®</sup> Processors<br>How to Boost Prediction Quality and Performance Using GBT in Intel <sup>®</sup> Data Analytics Acceleration Library | 49 |

| K-means Acceleration with 2nd Generation Intel <sup>®</sup> Xeon <sup>®</sup> Scalable Processors<br>Intel's Hardware and Software Stack for Big Data                                                            | 61 |

| Measuring Graph Analytics Performance<br>What Is Graph Analytics? And Why Does It Matter?                                                                                                                        | 71 |

# **LETTER FROM THE EDITOR**

Henry A. Gabb, Senior Principal Engineer at Intel Corporation, is a longtime high-performance and parallel computing practitioner who has published numerous articles on parallel programming. He was editor/coauthor of "Developing Multithreaded Applications: A Platform Consistent Approach" and program manager of the Intel/Microsoft Universal Parallel Computing Research Centers.

## **Happy New Year**

Welcome to the Era of oneAPI

Welcome to another year of *The Parallel Universe*. 2020 promises to be interesting. Some readers may know that I used to dread the trend toward heterogeneous computing. Then I came to accept it as inevitable. Now, I'm embracing it. Sure, heterogeneity is both a blessing and a curse. The blessing is better performance and efficiency. The curse is increased complexity. My hope is that someday machines will just take care of it for me (see **Why More Software Development Needs to Go to the Machines**), but until then, practical steps are being taken to minimize this complexity, starting with **oneAPI**. oneAPI is an **open specification** that describes a single software abstraction across diverse compute architectures.

The Intel implementation of oneAPI was recently announced by Raja Koduri (senior vice president, chief architect, and general manager of Intel Architecture, Graphics, and Software) at the Intel® HPC Developer Conference. Our feature article, Heterogeneous Programming Using oneAPI, gives an overview of this unified, standards-based approach to heterogeneous computing. Accelerating Compression on Intel® FPGAs shows how Data Parallel C++ makes FPGAs more accessible. Continuing this theme of heterogeneity, Is Your Game GPU-Bound? shows you how to answer this question using analysis tools like Intel® Graphics Performance Analyzers.

In the last issue, I briefly covered composable threading in the Julia\* programming language. Jameson Nash and Jeff Bezanson from Julia Computing, Inc., and Kiran Pamnany from Caltech, were kind enough to provide a more detailed look at the **New Threading Capabilities in Julia v1.3** for this issue. They walk through several code examples illustrating task parallelism using Julia.

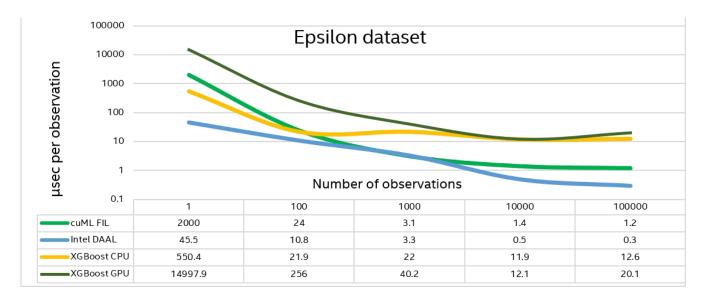

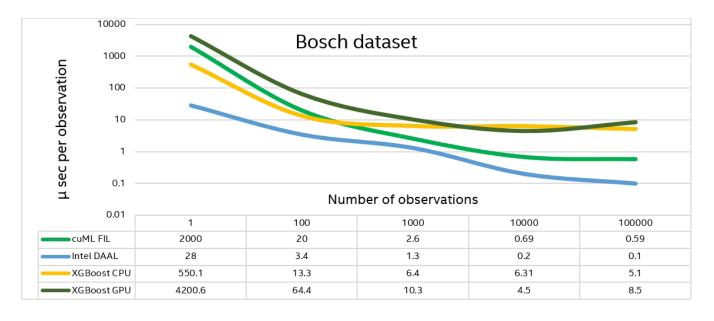

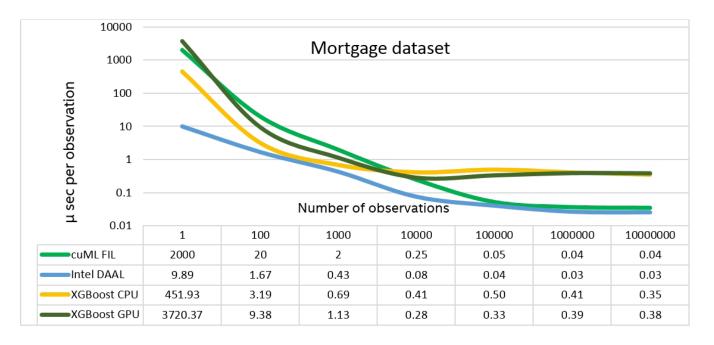

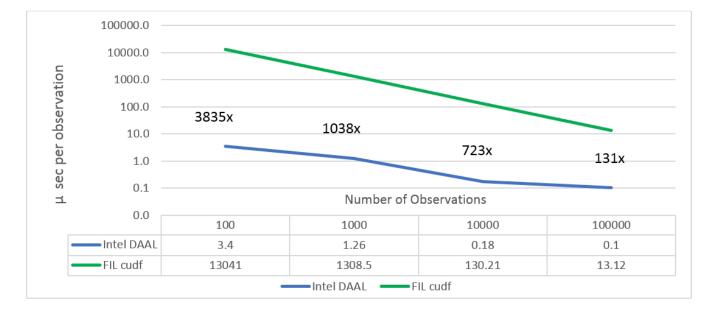

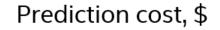

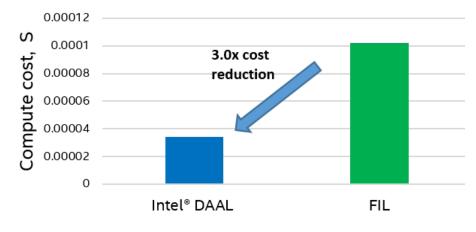

We close this issue with three articles on data analytics. The first, **Fast Gradient Boosting Tree Inference for Intel® Xeon® Processors**, shows how to use the XGBoost\* library to 3

improve the performance of model predictions. If you recall, the feature article in our **last** issue covered performance improvements for XGBoost training. The second, **K-means** Acceleration with 2nd Generation Intel<sup>®</sup> Xeon<sup>®</sup> Scalable Processors, shows how to take advantage of optimizations in Intel<sup>®</sup> Distribution for Python\* and the Intel<sup>®</sup> Data Analytics Acceleration Library to do k-means clustering. Finally, in Measuring Graph Analytics Performance, I discuss the right ways—and wrong ways—to do graph analytics benchmarking. However, the graph analytics landscape is large and varied, so please let me know if you disagree with my assertions.

Expect to see more articles on oneAPI in future issues. And, as always, don't forget to check out **Tech.Decoded** for more information on Intel's solutions for code modernization, visual computing, data center and cloud computing, data science, and systems and IoT development.

Henry A. Gabb January 2020

# HETEROGENOUS PROGRAMMING USING ONEAPI

How to Deliver Uncompromised Performance for Diverse Workloads Across Multiple Architectures

Nitya Hariharan, Application Engineer; Rama Kishan Malladi, Performance Modeling Engineer; Amarpal S. Kapoor, Technical Consulting Engineer; Kevin P O'Leary, Technical Consulting Engineer; Intel Corporation

Getting the maximum achievable performance out of today's hardware is a fine balance between optimal use of underlying hardware features and using code that is portable, easily maintainable, and power-efficient. These factors don't necessarily work in tandem. They require prioritizing based on user needs. It's non-trivial for users to maintain separate code bases for different architectures. A standard, simplified programming model that can run seamlessly on scalar, vector, matrix, and spatial architectures will give developers greater productivity through increased code reuse and reduced training investment. oneAPI is an industry initiative designed to deliver these benefits. It's based on standards and open specifications and includes the **Data Parallel C++ (DPC++)** language as well as a set of domain libraries. The goal of oneAPI is for hardware vendors across the industry to develop their own compatible implementations targeting their CPUs and accelerators. That way, developers only need to code in a single language and set of library APIs across multiple architectures and multiple vendor devices.

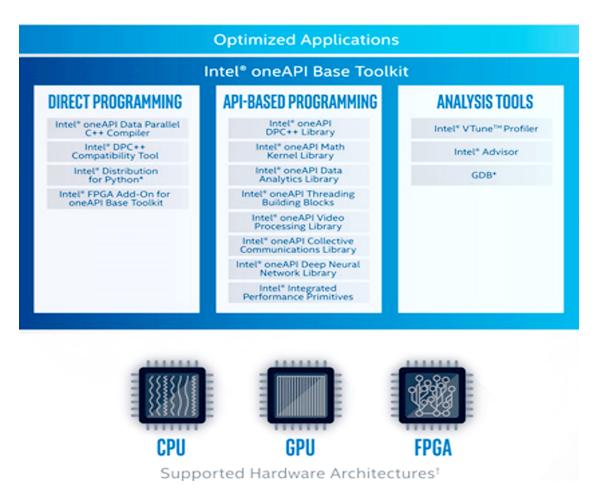

The Intel beta oneAPI developer tools implementation, targeting Intel<sup>®</sup> CPUs and accelerators, consists of the Intel<sup>®</sup> oneAPI Base Toolkit along with multiple domain specific toolkits—Intel<sup>®</sup> HPC, IoT, DL Framework Developer, and Rendering toolkits—which cater to different users.

**Figure 1** shows the different layers that are part of the beta **Intel oneAPI** product and the Base Toolkit, which consists of the Intel oneAPI DPC++ Compiler, the Intel® DPC++ Compatibility Tool, multiple optimized libraries, and advanced analysis and debugging tools. Parallelism across architectures is expressed using the DPC++ language, which is based on SYCL\* from Khronos Group. It uses modern C++ features along with Intel-specific extensions for efficient architecture usage. DPC++ language features allow code to be run on the CPU and to be offloaded onto an available accelerator—making it possibled to reuse code. A fallback property allows the code to be run on the CPU when an accelerator isn't available. The execution on the host and accelerator, along with the memory dependencies, are clearly defined.

Users can also port their codes from CUDA\* to DPC++ using the Intel DPC++ Compatibility Tool. It assists developers with a one-time migration and typically migrates 80 to 90% of the code automatically.

In addition to DPC++, the Intel oneAPI HPC Toolkit supports OpenMP\* 5.0 features that allow code to be offloaded onto a GPU. Users can either transition to using DPC++ or make use of the offload features on their existing C/C++/Fortran code. API-based programming is supported through a set of libraries (e.g., the Intel® oneAPI Math Kernel Library), which will be optimized for Intel GPUs.

The beta Intel oneAPI product also offers new features in **Intel® VTune™ Profiler**<sup>1</sup> and **Intel® Advisor**<sup>2</sup>, which allow users to debug their code and look at performance-related metrics when code is offloaded onto an accelerator.

# INTEL® ADVISOR Optimize Code for Modern Hardware

#### 1 Components of the Beta Intel<sup>®</sup> oneAPI Base toolkit

This article introduces the beta release of the oneAPI product to facilitate heterogeneous programming. We'll introduce the oneAPI software model and then discuss the compilation model and the binary generation procedure. oneAPI provides a single binary for all architectures, so the compile and link steps are different from normal methods of binary generation. Finally, we'll examine some sample programs. Note that we use the terms accelerator, target, and device interchangeably throughout this article.

#### oneAPI Software Model

The oneAPI software model, based on the SYCL specification, describes the interaction between the host and device in terms of code execution and memory usage. The model has four parts:

- 1. A platform model specifying the host and device

- 2. An execution model specifying the command queues and the commands that will be run on the device

- 3. A memory model specifying memory usage between the host and device

- 4. A kernel model that targets computational kernels to devices

#### **Platform Model**

The oneAPI platform model specifies the host and multiple devices that communicate with each other or the host. The host controls the execution of kernels on the devices and coordinates among them if there are multiple devices. Each device can have multiple compute units. And each compute unit can have multiple processing elements. The oneAPI specification can support multiple devices like GPUs, FPGAs, and ASICs as long as the platform satisfies the minimum requirements of the oneAPI software model. This typically means the hosts need to have a specific operating system, a specific GNU\* GCC version, and certain drivers needed by the devices. (See the release notes for each oneAPI component for details on the platform requirements.)

#### **Execution Model**

The oneAPI execution model specifies how the code is executed on the host and device. The host execution model creates command groups to coordinate the execution of kernels and data management between host and devices. The command groups are submitted in queues that can be run with either an in-order or out-of-order policy. Commands within a queue can be synchronized to ensure data updates on the device are available to the host before the next command is executed.

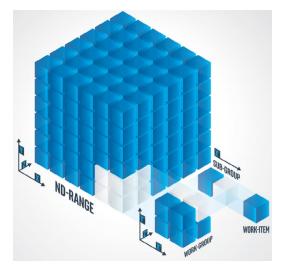

The device execution model specifies how the computation is done on the accelerator. The execution ranges over a set of elements that can either be a one-dimensional or multi-dimensional data set. This range is split into a hierarchy of ND-Range, work-groups, sub-groups, and work-items as shown in **Figure 2** for a three-dimensional case.

#### 2 Relationship between ND-Range, work-groups, sub-groups and work-items

Note that this is similar to the SYCL model, with the exception of sub-groups, which are an Intel extension. The work-item is the smallest execution unit in the kernel. And the work-groups determine how data is shared among these work-items. These hierarchical layouts also determine the kind of memory that should be used to get better performance. For example, work-items typically operate on temporary data that's stored in the device memory and work-groups use global memory. The sub-group classification was introduced to provide support for hardware resources that have a vector unit. This allows parallel execution on elements.

From **Figure 2**, it's clear that the location of the work-group or work-item within ND-Range is important, since this determines the data point being updated within the computational kernel. The index into ND-Range that each work-item acts upon is determined using intrinsic functions in the nd\_item class (global\_id, work\_group\_id, sub\_group\_id, and local\_id).

#### Memory Model

The oneAPI memory model defines the handling of memory objects by the host and device. It helps a user decide where memory will be allocated depending on the application's needs. Memory objects are classified as type buffer or images. An accessor can be used to indicate the location of the memory object and the mode of access. The accessor provides different access targets for objects residing on the host, global memory on the device, the device's local memory, or images residing on the host. The access types can be read, write, atomic, or read and write.

The Unified Shared Memory model allows the host and device to share memory without the use of explicit accessors. Synchronization using events manages the dependencies between host and device. A user can either explicitly specify an event to control when data updated by a host or device is available for reuse, or implicitly depend on the runtime and device drivers to determine this.

#### Kernel Programming Model

The oneAPI kernel programming model specifies the code that's executed on the host and device. Parallelism isn't automatic. The user needs to specify it explicitly using language constructs.

The DPC++ language requires a compiler that can support C++11 and later features on the host side. The device code, however, requires a compiler that supports C++03 features and certain C++11 features like lambda expressions, variadic templates, rvalue references, and alias templates. It also requires std::string,std::vector, and std::function support. There are restrictions on certain features for the device code which include virtual functions and virtual inheritance, exception handling, run-time type information (RTTI), and object management employing new and delete operators. The user can decide to use different schemes to describe the separation between the host and device code. A lambda expression can keep the kernel code in line with the host code. A functor keeps the host code in the same source file, but in a separate function. For users who are porting OpenCL code, or those who require an explicit interface between the host and device code, the kernel class provides the necessary interface.

The user can implement parallelism in three different ways:

- A single task that executes the whole kernel in a single work-item

- **The parallel\_for construct**, which distributes the tasks among the processing elements

- **The parallel\_for\_work\_group**. The parallel\_for\_work\_group construct distributes the tasks among the work-groups and can synchronize work-items within a work-group through the use of barriers.

# oneAPI Compilation Model

The oneAPI compilation model consists of build and link steps. However, the binary generated needs to support the execution of the device code on multiple accelerators. This means a DPC++ compiler and linker have to carry out additional commands to generate the binary. This complexity is generally hidden from the user, but can be useful for generating target-specific binaries.

The host code compilation is done in the default way for a standard x86 architecture. The binary generation for the accelerator is more complex because it needs to support single or multiple accelerators in addition to optimizations that are specific to each accelerator. This accelerator binary, known as a fat binary, contains a combination of:

- An intermediate Standard Portable Intermediate Representation (SPIR-V) representation, which is device-independent and generates a device-specific binary during compilation.

- **Target-specific binaries** that are generated at compile-time. Since oneAPI is meant to support multiple accelerators, multiple code forms are created.

Multiple tools generate these code representations, including the clang driver, the host and device DPC++ compiler, the standard Linux\* (ld) or Windows\* (link.exe) linker, and tools to generate the fat object file. During execution, the oneAPI runtime environment checks for a device-specific image within the fat binary and executes it, if available. Otherwise, the SPIR-V image is used to generate the target-specific image.

#### oneAPI Programming Examples

In this section, we look at sample code for the beta Intel oneAPI DPC++ Compiler, OpenMP device offload, and the Intel DPC++ Compatibility Tool.

#### Writing DPC++ Code

Writing DPC++ code requires a user to exploit the APIs and syntax of the language. **Listing 1** shows some sample code conversion from C++ (CPU) code to a DPC++ (host and accelerator) code. It's an implementation of the Högbom CLEAN\* algorithm posted on GitHub<sup>4</sup>. The algorithm iteratively finds the highest value in the image and subtracts a small gain of this point source convolved with the point spread function of the observation until the highest value is smaller than some threshold. The implementation has two functions: findPeak and subtractPSF. These have to be ported from C++ to DPC++ as shown in **Listings 1** and **2**.

#### Listing 1. Baseline and DPC++ implementation of the subtractPSF code

```

subtractPSF C++ code: baseline

for (int y = starty; y <= stopy; ++y) {

lhsIdx = y * residualWidth + startx;

rhsIdx = (y - diffy) * psfWidth + (startx - diffx);

for (int x = startx; x <= stopx; ++x, lhsIdx++, rhsIdx++)

residual[lhsIdx] -= MUL * psf[rhsIdx];

}</pre>

```

```

subtractPSF DPC++ code

sycl::qpu selector device selector;

sycl::queue d queue(device selector);

sycl::buffer<float, 1> a device(psf.data(), psf.size());

sycl::buffer<float, 1> b device(residual.data(), residual.size());

unsigned long size par = (stopy - starty);

sycl::range<1> a size{size par};

auto offset = sycl::id<1>(starty);

d queue.submit([&](sycl::handler &cqh) {

auto a in = a device.get access<sycl::access::mode::read>(cgh);

auto b res = b device.get access<sycl::access::mode::write>(cqh);

cqh.parallel for<class T>(a size,offset, [=] (sycl::id<1> idx) {

int y = idx[0];

int lhsIdx = y * residualWidth + startx;

int rhsIdx = (y - diffy) * psfWidth + (startx - diffx);

for (int x = startx; x < stopx; ++x, lhsIdx++, rhsIdx++) {

b res[lhsIdx] -= MUL * a in[rhsIdx];

}

});

});

d queue.wait and throw();

```

Code changes required to port from C/C++ to DPC++ include:

- Introduction of the device queue for a given device (using the device selector API)

- Buffers created/accessed on the device (using the sycl::buffer/get\_access APIs)

- Invocation of the parallel\_for to spawn/execute the computational kernel

- Wait for the completion of the kernel execution (and optionally catch any exceptions)

- Intel® DPC++ Compiler and flags: dpcpp -std=c++11 -02 -lsycl -lOpenCL

**Listing 2** shows the code changes for the findPeak function implementation. To better exploit parallelism in the hardware, DPC++ code has support for local\_work\_size, global\_id/local\_id, workgroup, and many other APIs, similar to the constructs used in OpenCL and OpenMP.

Listing 2. Baseline (top) and DPC++ (bottom) implementation of the findPeak code. clPeak is a structure of value and position data. Concurrent execution of work-groups is accomplished using the global and local IDs, and barrier synchronization across multiple threads (work-items) in a work-group. The result of this parallel\_for execution is further reduced (not shown) to determine the maximum value and position across work-groups.

#### findPeak: Baseline

```

maxVal = 0.0;

maxPos = 0;

const size_t size = image.size();

for (size_t i = 0; i < size; ++i) {

if (abs(image[i]) > abs(maxVal)) {

maxVal = image[i];

maxPos = i;

}

}

```

```

findPeak: DPC++

auto bufacc = buf.get_access<sycl::access::mode::read>(cgh);

auto resacc = res.get_access<sycl::access::mode::read_write>(cgh);

sycl::accessor<clPeak, 1, sycl::access::mode::read_write,</pre>

sycl::access::target::local>

local_res(sycl::range<1>(local_size), cgh);

cgh.parallel_for<class ex1>

(sycl::nd_range<1>(sycl::range<1>(global_size),

sycl::range<1>(local size)), [=] (sycl::nd item<1> item)

{

size_t global_id = item.get_global_id(0);

size_t local_id = item.get_local_id(0);

size_t local_dim = item.get_local_range(0);

size_t group_id = item.get_group(0);

local res[local id].val = 0.0;

local_res[local_id].pos = 0;

if(fabs(bufacc[global_id]) > fabs(local_res[local_id].val)){

local_res[local_id].val = bufacc[global_id];

local res[local id].pos = global id;

}

item.barrier(sycl::access::fence_space::local_space);

if (local id == 0) {

resacc[group_id].val = 0.0;

resacc[group_id].pos = 0;

for (int i=0; i < local_dim; i++) {</pre>

if(fabs(local_res[i].val) > fabs(resacc[group_id].val)){

resacc[group_id].val = local_res[i].val;

resacc[group_id].pos = local_res[i].pos;

}

}

}

});

```

#### **OpenMP Offload Support**

The beta Intel oneAPI HPC Toolkit provides OpenMP offload support, which enables users to take advantage of OpenMP device offload features. We look at a sample open-source Jacobi code<sup>3</sup> written in C++ with OpenMP pragmas. The code has a main iteration step that:

- Calculates the Jacobi update

- Calculates the difference between the old and new solution

- Updates the old solution

- Calculates the residual

The iteration code snippet is shown in Listing 3.

#### Listing 3. Sample Jacobi solver with OpenMP pragmas

```

// Iterate M times

#pragma omp parallel private (i, t)

{

#pragma omp for { // Jacobi update on xnew using b and x }

#pragma omp for reduction (+:d) { // Calculate difference d }

#pragma omp for { //overwrite x with x_new }

#pragma omp for reduction (+:r) { // Calculate residual r }

}

```

**Listing 4** shows the updated code with the omp target clause, which can be used to specify the data to be transferred to the device environment, along with a data modifier that can either be to, from, tofrom, or alloc. Since array b is not modified, we use the clause to. And since x and xnew are initialized before the offload directives and updated within the device environment, we use the tofrom clause. The reduction variables d and r are also set and updated during each iteration and have the tofrom map clause.

#### Listing 4. Sample Jacobi solver updated with OpenMP offload pragmas

```

// Iterate M times

#pragma omp target data map(tofrom:x,xnew) map(to:n,b) map(tofrom:d,r)

{

#pragma omp parallel for { // Jacobi update }

#pragma omp parallel for reduction (+:d) { // Calculate difference d }

#pragma omp parallel for { // Overwrite x_old with x_new }

#pragma omp parallel for reduction (+:r) { // Calculate residual r }

}

```

To compile the offload target code with the oneAPI compiler, the user needs to set:

- The environment variables pertaining to the compiler path

- The relevant libraries

- The different components

The path to these environment variables will depend on the oneAPI setup on the user machine. We look at the compilation process for now, which will be similar across machines, to demonstrate the ease of use of the specification. To compile the code, use the LLVM-based icx or icpc -qnextgen compiler as follows:

```

$ icpc -fiopenmp -fopenmp-targets=spir64 -D_STRICT_ANSI__ jacobi.cpp -o

jacobi

```

The -D\_\_STRICT\_\_ANSI flag ensures compatibility with GCC 7.x and higher systems. The spir64 flag refers to the target independent representation of the code and is ported to target-specific code during the link stage or execution. To execute the code, run these commands:

```

$ export OMP_TARGET_OFFLOAD="MANDATORY"

$ export LIBOMPTARGET_DEBUG=1

$./jacobi

```

The MANDATORY option for OMP\_TARGET\_OFFLOAD indicates that the offload has to be run on the GPU. It's set to DEFAULT by default, which indicates offload can be run on CPU and GPU. The LIBOMPTARGET\_DEBUG flag, when set, provides offload runtime information that helps in debugging.

The OpenMP offload support example is for C/C++ programs, but Fortran offload is also supported. This allows HPC users with Fortran code bases to run their code on GPUs as well.

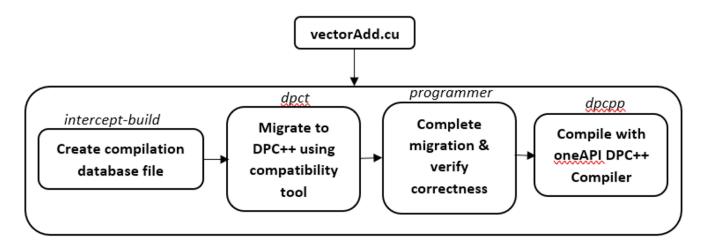

#### Intel DPC++ Compatibility Tool

The Intel DPC++ Compatibility Tool is a command-line-based code migration tool available as part of the Intel oneAPI Base Toolkit. Its primary role is to enable the porting of existing CUDA sources to DPC++. Source locations where automatic migration isn't possible are flagged through suitable errors and warnings. The Intel DPC++ Compatibility Tool also inserts comments in source locations where user interventions are necessary.

**Figure 3** shows a typical workflow that CUDA users can use to port their source code to DPC++. The Intel DPC++ Compatibility Tool currently supports the Linux\* and Windows\* operating systems. This article assumes a Linux environment. The Intel DPC++ Compatibility Tool currently requires header files that are shipped with CUDA SDK. To demonstrate the migration process, we use the VectorAdd sample from CUDA SDK 10.1, typically found in a location similar to:

\$ ls /usr/local/cuda-10.1/samples/0\_Simple/vectorAdd

#### **3** Recommended workflow for migrating existing CUDA applications

VectorAdd is a single-source example with around 150 lines of code. The CUDA kernel device code in this case computes the vector addition of arrays A and B into array C.

Note that the commands, paths, and procedure shown here are correct at the time of publishing. Some changes may be introduced in the final version of the product.

To initialize the environment to use the Intel DPC++ Compatibility Tool, run the following command:

\$ source /opt/intel/inteloneapi/setvars.sh

The setvars.sh script not only initializes the environment for the Intel DPC++ Compatibility Tool, but all other tools available in the Intel oneAPI Base Toolkit.

A simplified version of the CUDA Makefile is used, as shown in Listing 5.

#### Listing 5. Makefile for porting CUDA code to DPC++

#### < The Parallel Universe</p>

The next step intercepts commands issued as the Makefile executes and stores them in a compilation database file in JSON format. The Intel DPC++ Compatibility Tool provides a utility called intercept-build for this purpose. Here's a sample invocation:

\$ intercept-build make

The real conversion step is then invoked:

```

$ dpct -p compile_commands.json --in-root=. --out-root=dpct_output

vectorAdd.cu

```

The --in-root and --out-root flags set the location of user program source and location where the migrated DPC++ code must be written. This step generates ./dpct output/vectorAdd.dp.cpp.

To ensure that vector addition is deployed onto the integrated GPU, explicit specification of the GPU queue is made instead of the submission to the default queue. The list of supported platforms is obtained with the list of devices for each platform by calling get\_platforms() and platform.get\_devices(). With the target device identified, a queue is constructed for the integrated GPU and the vector add kernel is dispatched to this queue. Such a methodology may be used to target multiple independent kernels to different target devices connected to the same host/node.

Next, the modified DPC++ code is compiled using:

```

$ dpcpp -std=c++11 -I=/usr/local/cuda-10.1/samples/common/inc

vectorAdd.dp.cpp -lOpenCL

```

The resulting binary is then invoked, and the vector addition is confirmed to be executing on the integrated GPU, shown in **Listing 6**.

#### Listing 6. Output from running the ported DPC++ code on the integrated GPU

```

$ ./a.out

[Vector addition of 5000000 elements]

Platform: Intel(R) OpenCL HD Graphics

Device: Intel(R) Gen9 HD Graphics NEO

Platform: Intel(R) OpenCL

Device: Intel(R) Core(TM) i7-7567U CPU @ 3.50GHz

Platform: SYCL host platform

Device: SYCL host device

Copy input data from the host memory to the device

kernel launch with 19532 blocks of 256 threads

Running on :Intel(R) Gen9 HD Graphics NEO

Copy output data from the device to the host memory

Test PASSED

```

For details on these tools, use these help flags:

```

$ intercept-build -h

$ dpct -h

```

## Uncompromised Performance for Diverse Workloads Across Multiple Architectures

This article introduced oneAPI and the beta Intel oneAPI Toolkits and outlined the components that are part of the Intel oneAPI Base Toolkit. The beta release includes toolkits to help users in the HPC, AI, analytics, deep learning, IoT, and video analytics domains transition to oneAPI. The DPC++ programming guide provides complete details on the various constructs supported for optimized accelerator performance. The OpenMP example shown in the article is for a C++ program. However, GPU offload will be supported for C and Fortran as well. oneAPI provides the software ecosystem you need to port and run your code on multiple accelerators.

## References

- 1. Intel<sup>®</sup> VTune<sup>™</sup> Profiler

- 2. Intel<sup>®</sup> Advisor

- 3. Jacobi solver using OpenMP

- 4. https://github.com/ATNF/askap-benchmarks/tree/master/tHogbomCleanOMP

# HIGHLIGHTS

#### oneAPI Reviews

See the ecosystem support for oneAPI from a growing, global list of companies, universities, and institutions.

Read more >

# INTEL® DEVCLOUD A DEVELOPMENT SANDBOX FOR DATA CENTER TO EDGE WORKLOADS

# Develop, Test, and Run Your Workloads on a Cluster of the Latest Intel<sup>®</sup> Hardware and Software.

With integrated Intel<sup>®</sup> optimized frameworks, tools, and libraries, you'll have everything you need for your projects.

# Try Out a Diverse Collection of Intel<sup>®</sup> Hardware.

Expand your skills and experiment with this state-of-the-art cluster that offers capabilities like natural language processing and time-series analysis—plus edge acceleration hardware.

# Develop with Intel<sup>®</sup> Software Development Tools.

Jump-start your projects without having to download, configure, or install the latest compilers, performance libraries, and tools from Intel.

# Use Popular AI Frameworks.

Accelerate your algorithms and applications with Intel<sup>®</sup> Optimized AI Frameworks that are ready for training and inference.

# **GET STARTED NOW >**

For more complete information about compiler optimizations, see our Optimization Notice at software.intel.com/articles/optimization-notice#opt-en. Intel and the Intel logo are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. © Intel Corporation

# **ACCELERATING COMPRESSION ON INTEL® FPGAS**

#### How oneAPI is Making FPGAs More Accessible than Ever

Andrei Hagiescu, FPGA Software Engineer, and David Cashman, FPGA Software Engineer, Intel Corporation

Field programmable gate arrays (FPGAs) provide a flexible hardware platform that can achieve high performance on a large variety of workloads. In this article, we'll discuss the Intel GZIP example design, implemented with **oneAPI**, and how it can help make FPGAs more accessible. (For more on oneAPI, see this issue's feature article, **Heterogeneous Programming Using oneAPI**.)

The example design implements DEFLATE, a lossless data compression algorithm essential to many storage and networking applications. The example is written in **SYCL** and compiled using the **oneAPI Data Parallel C++ (DPC++) Compiler**, demonstrating a significant acceleration in compression times with compelling compression ratio. The GZIP example design takes advantage of the massive spatial

parallelism available in FPGAs to accelerate the LZ77 compression algorithm by parallelizing memory accesses, dictionary searches, and matching. Since the design is implemented using oneAPI, the code can target any compute technology, but we specifically optimize for FPGAs. The example produces GZIP-compatible compressed data files so that developers can use standard software tools to decompress the compressed files produced by this design.

## How FPGAs Work

FPGAs are reconfigurable devices consisting of many low-level compute and storage elements (e.g., adders/multipliers, logic operations, memories) structured as a 2D array and connected by reconfigurable routing. These elements can form complex compute pipelines and specialized on-chip memory systems. In contrast to traditional architectures, which are designed to execute generic code, FPGAs can be reconfigured to implement custom architectures that boost the performance of a target application. For example, FPGAs can implement specialized compute pipelines that can execute an entire loop iteration every clock cycle. FPGAs fit well in an acceleration model, with off-chip attached memory (e.g., DDR4) and connectivity to a host CPU (e.g., through PCIe).

# **DPC++** Compilation to FPGAs

The FPGA backend of the DPC++ Compiler produces a bitstream that reconfigures the FPGA for the given code. Each kernel in the SYCL program is implemented using a subset of the FPGA resources. All implemented kernels can execute concurrently.

Within a kernel, each loop body is translated to a deep and specialized pipeline that contains all the functional units required to process an entire loop iteration. Conditional statements are refactored as predicated execution. Traversing the pipeline once executes an entire loop iteration.

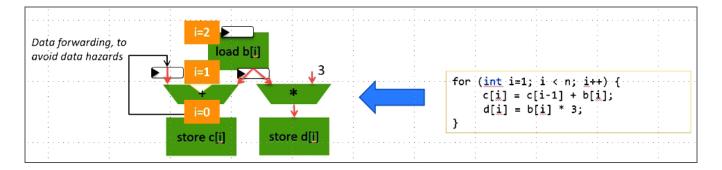

The compiler identifies instructions that can be executed in parallel, and places them in the same pipeline stages, so that they execute in parallel on arbitrarily many functional units. Further, it optimizes the pipeline by ensuring that data can be forwarded, so that subsequent loop iterations can be issued as soon as possible (often in consecutive cycles), without data hazards (**Figure 1**).

#### Contract Contract

1

#### Pipeline generated from user code

Compiling for the FPGA typically takes several hours. To accelerate the development cycle, the FPGA backend is accompanied by an emulator, static performance reports, and a dynamic profiler to guide optimization decisions. Emulation and static report generation take minutes instead of hours, vastly improving the productivity of FPGA application development compared to traditional RTL development flows.

## The oneAPI Advantage

The GZIP design takes full advantage of key oneAPI programming features such as single-source design and multiple accelerators, as well as heterogeneous computing where the accelerator runs the hotspot code and the CPU is processing the non-hotspot code. Since the design is written using oneAPI, this enables anyone who knows C++ to write an algorithm suitable for compilation to FPGAs, focusing mainly on the algorithmic details and leaving the hardware translation to the compiler backend. Since the algorithm is expressed in C++, it can be easily tested for correct functionality. Hardware performance can be anticipated by examining reports before committing to a hardware compilation.

## The Example Design

The GZIP design's architecture follows DEFLATE's dataflow. We create three kernels to do the work:

- 1. LZ77

- 2. Huffman

- 3. CRC

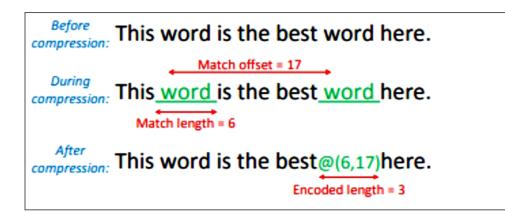

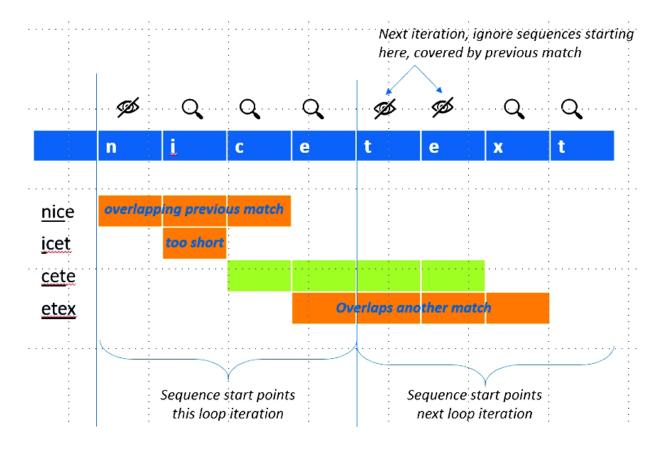

Our first kernel computes LZ77 data, searching and eliminating duplicate sequences from the file. The idea is illustrated in **Figure 2**.

#### 2 Example of LZ77 compression

A duplicated sequence is replaced with a relative reference to the previous occurrence. Less storage is required to encode the reference than the original text, reducing the file size.

To find matches, we need to remember all the sequences we've seen and pick the best candidate match. The sequence is replaced, and the matching process continues from the end of the current match—or, if we didn't find a good match, at the next symbol. This is harder than it sounds.

Our goal will be to process 16 bytes on every FPGA clock cycle. So, in one clock cycle, we need to:

- Look in our history for the best match at each of 16 starting points

- Pick the best match (or matches, if there are several that don't overlap)

- Write the result to our output

- Store the string we just read back into the dictionary

It's not obvious that this work can be done in parallel, since matches can't overlap. We can't pick a match starting at a given byte until we know that no earlier match already covers it. (We'll cover this in detail in the next section.)

The second kernel applies Huffman encoding to the data, generating the final compressed result. During this step, all symbols and references are replaced with a variable bitwidth encoding which provides codes with fewer bits for the most frequent symbols, further reducing the file size. It's easier to see how this step can be parallelized: we can have 16 (or more) independent units of hardware, each determining the Huffman code for a given symbol. There's still a problem, though. Since the output has variable length, we need to eventually write each output to the right location in the output stream—which means we need to know how large all the previous outputs were. Also, Huffman codes are not byte-aligned, so we'll need to do a lot of bit-level manipulation. Fundamentally, though, this is a less complicated problem than LZ77, and we won't go into more detail here.

Finally, a third kernel computes CRC32 on the input data. This kernel is independent of the other two and can operate in parallel. It's also relatively simple to implement on the FPGA, so we won't discuss it in detail here.

## FPGA-Optimized LZ77 Implementation

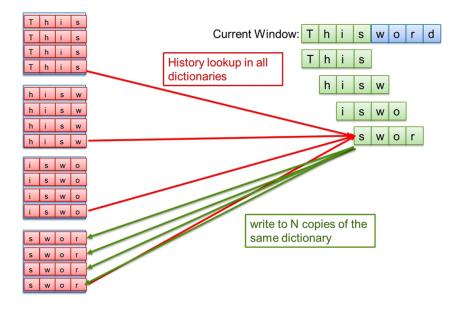

To capture the sequential nature of the data processing, the LZ77 encoder is described as a single task with a single main loop. That is, the code describes a single thread of execution, iterating symbol-by-symbol on the entire file. A set of dictionaries is created to store previously seen sequences in the datafile. These dictionaries are indexed through a hash of the data they store, similar to a hash map. However, for performance reasons, a more recent (colliding) entry overwrites dictionary data corresponding to an earlier entry with the same hash key. The dictionaries are updated by writing the newly seen input to all the dictionaries. To reduce the impact of collisions in the dictionaries, we separate the previously seen sequences in multiple disjoint sets.

Why do we need more than one dictionary? Recall that we want to process 16 bytes per cycle. This means storing 16 strings (one starting at each byte) to the dictionary and doing 16 hash lookups on every clock cycle. Each FPGA memory block only has two ports. To allow all these concurrent accesses, we create 16 separate memory systems, each storing strings at a different position. We now have our history spread across 16 dictionaries, so each of our 16 hash lookups now needs to be done in 16 different dictionaries—for a total of 256 lookups. It seems like we've just made the problem worse.

We can solve this by building 16 copies of each of our dictionaries, for a total of 256 dictionaries. All of these dictionaries use a large fraction of the FPGA's on-chip memory, but we've achieved our goal of doing 16 hash lookups and writes on every clock cycle. **Figure 3** shows an example of the dictionary structure we would need if we only wanted to process four bytes per clock cycle. (Incidentally, the FPGA area devoted to dictionaries is the main limitation preventing us from processing more than 16 bytes per cycle.)

**3** Dictionary replication for four-byte parallel access

Expressing the parallel behavior may sound tricky. But, in fact, the compiler identifies the data parallelism between the lookups on its own. That is, the code will result in specialized FPGA logic capable of executing all the dictionary lookups concurrently. In the code, VEC is the number of bytes being processed per cycle, and LEN is the size of the string. In the example design, both are set to 16. We've used template metaprogramming (the unroller) to replicate the code in the inner function for all <u>i</u> and <u>j</u>. The data from all the lookups is aggregated in a reduction-like operation as part of the same pipeline.

Our dictionaries solve one problem, but we have a lot more processing to do if we want to complete a full loop iteration on each clock cycle. Luckily, we don't need to. The FPGA compiler will automatically pipeline the datapath. So after iteration 0 of the loop finishes reading from the dictionary, iteration 1 can start, while iteration 0 starts on picking the best match. The match selection can be staged across several cycles, with a different iteration of the loop operating at each stage.

```

//loop over VEC compare windows, each has a different hash

unroller<0, VEC>::step([&] (int i){

//loop over all VEC bytes

unroller<0, LEN>::step{[&] {int j} {

compare_window[j][0][i] = dictionary_0[hash[1][j];

compare_window[j][1][i] = dictionary_0[hash[1][j];

compare_window[j][2][i] = dictionary_0[hash[1][j];

compare_window[j][3][i] = dictionary_0[hash[1][j];

compare_window[j][3][i] = dictionary_0[hash[1][j];

}};

};

```

When generating the output, one final challenge is how to correctly account for the impact of a match on subsequent matches. Once a match is identified, overlapping matches must be disregarded. In our single\_task code representation, this manifests as a loop-carried variable that needs to be computed before subsequent iterations of the loop can proceed. If the computation is too complex, it may limit the clock speed of the FPGA, or limit our ability to complete a loop iteration on every clock cycle.

Because we target an FPGA, we can customize the hardware to optimize the handling of this dependency. We simplify the data hazard by minimizing the amount of computation that depends on it. For example, we choose to do the hash lookups speculatively, determining all the possible matches, even if the lookups are related to overlapped matches. We simply prune the overlapping matches later on. The FPGA backend optimizes the required forwarding logic, fully avoiding the data hazard. **Figure 4** demonstrates the pruning of speculative matches.

4 Pruning speculative matches, accounting for matches identified in previous loop iterations, overlapped matches in the current loop iteration, and poor quality matches

# Task-Level Parallelism

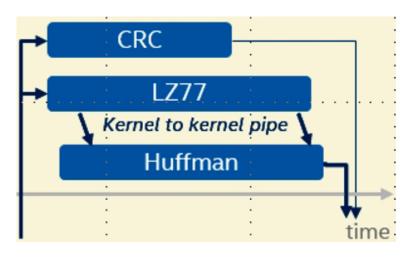

To compress a file, the three processing kernels are asynchronously submitted by the host CPU. They can run concurrently in the FPGA hardware. They operate at slightly different rates, with CRC being faster. LZ77 produces data needed by the Huffman kernel. To avoid an additional delay, and to avoid transferring data through off-chip memory, we use kernel-to-kernel communication pipes, a proposed Intel extension of the SYCL language. This extension allows different kernels to exchange data, in sequence, without writing to off-chip memory, as shown in **Figure 5**.

#### Che Parallel Universe

5 Task parallelism in GZIP

#### Building the GZIP Design

You can **download and run the GZIP design** from the **oneAPI code samples**. You may target the FPGA emulation to verify correctness and functional behavior. Attempting to compress, for example, /bin/emacs-24.3 will result in:

```

make fpga_emu

./gzip.fpga_emu /bin/emacs-24.3 -o=test.gz

Running on device: Intel(R) FPGA Emulation Device

Compression Ratio 34.2421%

PASSED

```

The next step is to generate static optimization reports for the design. When optimizing, you should inspect these reports to understand the structure of the specialized pipelines being created for your kernels. You can find the reports at gzip\_report.prj/reports/report.html.make reports.

Finally, you can compile and run the design on FPGA hardware. The optimized compilation will take a few hours.

make fpga

## Performance

Here's how we invoke GZIP:

./gzip.fpga <input\_file> [-o=<output\_file>]

To evaluate performance, the application will call the compression function repeatedly and report on the overall execution time and throughput. Here's some sample output:

```

_/gzip.fpga_emu /bin/emacs-24.3 -o=test.gz

Running on device: pac_a10 : Intel PAC Platform (pac_f400000)

3.5 GB/s

Compression Ratio 34.2421%

```

## Making FPGAs More Accessible

With oneAPI, FPGAs are more accessible than ever. Spatial architectures open great acceleration opportunities, often in domains that are not embarrassingly parallel. And it's all at your fingertips with the DPC++ compiler and oneAPI.

# **VIDEO HIGHLIGHTS**

#### oneAPI: The Path to Streamlined Cross-Architecture Development

As compute technology evolves at an increasingly accelerated pace, so, too, does the world's reliance on compute hardware that is diverse enough to handle expansive datacentric workloads. According to Bill Savage, vice president and general manager of Compute Performance and Developer Products at Intel, it's the precise focus of oneAPI, an initiative that simplifies the programming of diverse architectures—CPUs, GPUs, FPGAs, AI accelerators—to meet customer workload needs.

Watch it >

Download free Intel® Performance Libraries and start creating better, more reliable, and faster applications now.

# FREE DOWNLOAD >

For more complete information about compiler optimizations, see our Optimization Notice at software.intel.com/articles/optimization-notice#opt-en. Intel and the Intel logo are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. © Intel Corporation

# **IS YOUR GAME GPU-BOUND?**

## It's Easy to Find Out with a GPU and Device Context Queue Analysis

Oleg Fedyaev, Graphics Software Engineer, Intel Corporation

Computer graphics is an amazing, essential part of our everyday lives—while we work on computers, watch movies, use smartphones, and even drive cars. The performance of graphics processors has dramatically increased over the last 10 years. And the influence of the video gaming industry on this process is hard to underestimate. At the same time, the continuous growth of GPU capabilities is opening new opportunities for game developers, encouraging them to invent breakthrough rendering techniques and effects to gain every possible hardware advantage. But this race between GPU hardware developers and game developers creates a drawback. Often, innovative rendering techniques bump into hardware limits.

In this article, we'll walk through a quick and easy way to see whether your game is CPU-bound using a high-level system overview.

## Game Performance Fundamentals

Video game production is expensive. And investing in performance optimization is an important factor contributing to a game project's profitability. Normally, different game genres—action, adventure, strategy, and others—have different performance requirements. If a game seems visually slow, with notable lags or delays in drawing artifacts, it definitely has performance issues that must be addressed.

A formal metric to measure game performance is frame rate, the number of frames rendered per second (FPS). FPS is used for benchmarking and ranking different applications: the higher the FPS, the better. In most cases, this approach is feasible. For example, an action game with a lot of motion doesn't look good if FPS is low.

A modern game is a complex product consisting of multiple components:

- Rendering graphics

- Calculating physics

- Playing sounds

- Executing scripts

- Hosting network

- And more

Each component, separately or in combination, can affect game performance. That's why it can be tricky to identify whether an application is GPU- or CPU-bound.

Though it's only one aspect of a game, it's reasonable to start analysis from rendering, since graphics can be crucial to creating the game's unique style, spirit, and atmosphere.

## **Classic Rendering Pipeline**

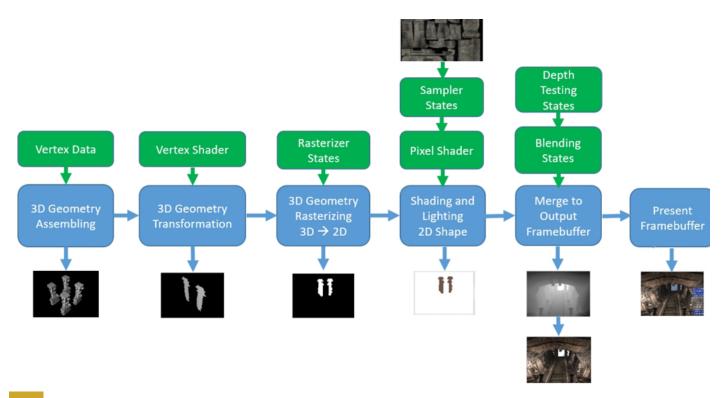

There's no way to define precisely whether the GPU is a performance bottleneck without understanding the graphics rendering pipeline, the graphics programming model, and the role of a graphics driver in this procedure. A thorough analysis of GPU activity through the whole stack—from the application code to the hardware—requires significant expertise. Fortunately, it's enough to perform a basic performance analysis to see overall GPU utilization without going into great detail. A rendering pipeline operates with resources and states. Resources bound to the pipeline specify what should be rendered and where. They can consist of geometries, textures, and render targets written in a proper format. Rasterization parameters, testing depth conditions, blending attributes, and other states specify how those resources should be interpreted and processed to generate an image on a screen. Render resources and states are tightly connected with GPU programs, also called shaders, which are executed in different stages of the rendering pipeline (**Figure 1**).

#### **1** Rendering pipeline

The pipeline's classic rendering process takes source data and sequentially modifies it, passing it through the same stages until it reaches the destination. Any rendered object is first transformed in a virtual space, and then projected onto a screen surface. After that, a visible part of that projection is colorized and merged with other rendered objects in a framebuffer.

The graphics programming model is simple. Draw context is configured, opened, and used for submitting rendering commands in the correct order: required resources, states, and programs should be bound to the pipeline before invoking any draw command that orders the pipeline to do a job. This procedure is repeated as many times as needed for objects to be rendered, until a final scene forms in a framebuffer. We can push this to a screen with a buffer swap command. Regardless of whether an application uses OpenGL\*, DirectX\*, Vulkan\* or any other graphics API, this concept stays the same.

It's now obvious how many complicated operations constitute a single draw. And each operation contributes to the draw duration. Individual draw durations vary, affecting the total frame rendering time. A long frame time may indicate a GPU-bound scenario, which we can confirm or reject after estimating the GPU load based on graphics driver performance markers.

# **Graphics Driver Activity**

A common graphics program works with a graphics driver, but never directly with the GPU. Any time we open a draw context in our application, we implicitly create a corresponding interface to a graphics driver, known as a driver device context. To make rendering possible, the driver must perform a lot of work:

- Release and allocate memory blocks on the GPU

- Upload the resources necessary for rendering from the CPU to the GPU

- Set registers of the GPU execution units

- Upload GPU programs

- Transfer results back to the CPU

- And more

Any time we invoke a sequence of graphics API calls within the application code, the driver translates them into a sequence of commands eligible for the GPU. Commands are not executed on the GPU immediately. Instead, they accumulate in a command buffer. The driver constantly batches a series of commands into packets, and then pushes these packets into a device context queue, scheduling them for execution (**Figure 2**).

|                                                  | wait in queue duration | execution duration                                   |  |  |  |

|--------------------------------------------------|------------------------|------------------------------------------------------|--|--|--|

|                                                  |                        | → ← ─ → ◆                                            |  |  |  |

| 🔽 Render { 9.27 ms }                             |                        | 🕒 🔽 Render { 2.22 ms }                               |  |  |  |

| <sup>(</sup> (•) <sup>)</sup> Signal { 9.25 ms } |                        | 🔽 <sup>((•))</sup> Signal { 2.22 ms }                |  |  |  |

| <sup>((</sup> )) Signal { 9.24 ms }              |                        | <sup>((•))</sup> <sup>((•))</sup> Signal { 2.22 ms } |  |  |  |

| 🔽 Render { 8.81 ms }                             |                        | (🕐 🔝 Present Token ( 2.2                             |  |  |  |

| <sup>((</sup> † <sup>))</sup> Signal { 8.80 ms } |                        | ((°)) Signal { 2.22 ms }                             |  |  |  |

| <sup>((</sup> † <sup>))</sup> Signal { 8.80 ms } | queue size             |                                                      |  |  |  |

| 🕒 Wait { 8.77 ms }                               |                        |                                                      |  |  |  |

| 📥 Render { 8.74 ms }                             |                        |                                                      |  |  |  |

| <sup>((</sup> † <sup>))</sup> Signal { 8.73 ms } |                        |                                                      |  |  |  |

| <sup>((</sup> † <sup>))</sup> Signal { 8.73 ms } |                        |                                                      |  |  |  |

| 🔛 Present Token { 8.71 ms }                      |                        |                                                      |  |  |  |

| <sup>((</sup> ۴ <sup>))</sup> Signal { 8.12 ms } |                        |                                                      |  |  |  |

| former formation                                 |                        |                                                      |  |  |  |

| frame duration                                   |                        |                                                      |  |  |  |

|                                                  |                        |                                                      |  |  |  |

2 Command buffer

A device context queue can contain different types of packets with different types of commands. The prevailing command type in a packet defines the packet's type. Each packet stays in the queue, waiting until the last command written in the previous packet has been executed on the GPU. (For example, see the selected render packet in **Figure 2**.)

Exploring the device context queue can give us some useful performance insights. For example, a huge queue size usually corresponds to a huge amount of graphics work submitted to the GPU. Long packet execution time may be due to computationally-intensive draw procedures. Long packet waits can be caused by inefficient rendering algorithms or synchronization.

When we've identified all the packets relating to a single frame, we can roughly estimate the frame duration, which we can calculate as a time range by submitting the first command packet in a queue until executing the last command from the last submitted packet within that frame.

However, even if a frame time is long, we can't define whether our application is GPU-bound until we explore a corresponding GPU hardware queue associated with a graphics processor performing rendering. The GPU is a shared resource that can serve multiple applications, rendering graphics simultaneously. Long rendering time may be a result of concurrent execution with another application that acquired the GPU context at the same time.

The hardware GPU queue (**Figure 3**) provides a clear picture of the overall GPU utilization. We can use this queue to identify how busy the GPU is, and which application is rendered at the time.

#### 3 Hardware GPU queue

The GPU queue snapshot in **Figure 3** shows at least two simultaneously rendered applications, differentiated by the colors of the command packets. Neither application is GPU-bound. The frame time of the application, highlighted in blue, is not much longer than 11 milliseconds, which corresponds to approximately 80 FPS. And 80 FPS is usually high enough. The green one seems to be a background process with very tiny frames (about 5 milliseconds each). Moreover, the GPU isn't even as busy as it could be, since we can see multiple gaps between executing command packets, corresponding to periods when the GPU is idle.

The concept of analyzing software and hardware queues is quite promising from a reliability perspective. Plus, these queues are easy to build, since we know how to acquire the required performance data.

# System Event Tracing

Regardless of whether we work on Windows\*, Linux\*, macOS\*, or any other operating system, we can connect to a system event trace layer, which logs different types of events associated with key execution points within different system modules. Some events are eligible for performance analysis. The graphics driver is no exception. Any time the driver pushes a command packet into a device context queue, uploads a command packet to the GPU, or executes the last command written in a command packet, it submits corresponding events into a system tracing layer so that we can easily acquire them. For example, if we want to build a device context and GPU command packet queues on Windows, we need to capture several events from the Microsoft-Windows-DxgKrnl provider of the Event Tracing for Windows\* (ETW\*) system.

Different attributes encoded into events data enable binding different events together to distinguish the current status of each packet in a queue at any time.

# **Graphics Application Analysis**

System event tracing is well documented and can be used on any platform. There are many tools that can capture or visualize system tracing data. However, the number of tools capable of proper simultaneous analysis of device context and GPU hardware queues is limited. **Intel® GPA Graphics Trace Analyzer** is one of these tools, designed to analyze the performance of graphics applications with different levels of detail, from a high-level system analysis to a single frame per-draw analysis.

Now let's apply what we've learned to a real-life, graphics-intensive game. We can try it on a workstation with a graphics processor in the middle performance range to make our experiment predictable. We'll use the just-released **Borderlands 3**\*, a well-known game from the first-person shooter genre. We'll run it on the **Intel® NUC Mini PC NUC8i7HVK**, which has two graphics processors: integrated Intel® HD Graphics 630 and discrete AMD Radeon RX Vega M GL\*. If we run this game at 2560x1440 resolution adapted for widescreen monitors and switch all graphics options in the game to a high profile, the game engine selects for rendering the most capable graphics processor, which seems to be Radeon Vega on this device.

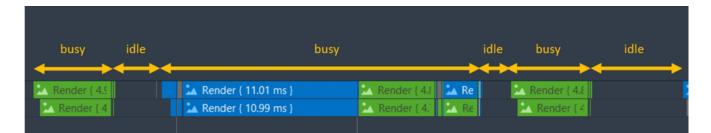

The first thing that catches our eye after five minutes of play is a lag between changing the state of an input device, such as a mouse or a gamepad, and changing a scene on a screen. Animation of some moving objects also looks a bit ragged. If we capture and open a trace with Intel GPA Graphics Trace Analyzer, we can observe all attributes of the GPU-bound scenario from the first sight at timeline tracks with a device context queue and GPU hardware queue (**Figure 4**).

#### Che Parallel Universe

|                                                                                               |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | frame duration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type filter expression (Ctrl+ <b>Q</b>                                                        | Ab 🕻  | Milliseconds                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 700                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 48.84<br>720 740                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1 ms.<br>760                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 3D Radeon RX Vega M GL Graphi                                                                 | cs P  | Rei Rend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R Render { 17.63 m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Render { 1 A Rend                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R         Render { 17.59 m           R         Present { 17.57 m                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |