# Effectively Train and Execute Machine Learning and Deep Learning Projects on CPUs

Parallelism in Python\* Using Numba\*

Boosting the Performance of Graph Analytics Workloads

# CONTENTS

| Letter from the Editor<br>Onward to Exascale<br>by Henry A. Gabb, Senior Principal Engineer, Intel Corporation                                                                     | 3  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <b>Effectively Train and Execute Machine Learning and Deep Learning</b><br><b>Projects on CPUs</b><br>Meet the Intel-Optimized Frameworks that Make It Easier                      | 5  |

| Parallelism in Python* Using Numba*<br>It Just Takes a Bit of Practice and the Right Fundamentals                                                                                  | 17 |

| <b>Boosting the Performance of Graph Analytics Workloads</b><br>Analyzing the Graph Benchmarks on Intel <sup>®</sup> Xeon <sup>®</sup> Processors                                  | 23 |

| How Effective is Your Vectorization?<br>Gain Insights into How Well Your Application is Vectorized Using Intel® Advisor                                                            | 29 |

| Improving Performance using Vectorization for Particle-in-Cell Codes<br>A Practical Guide                                                                                          | 37 |

| <b>Boost Performance for Hybrid Applications with Multiple Endpoints</b><br><b>in Intel® MPI Library</b><br>Minimal Code Changes Can Help You on the March Toward the Exascale Era | 53 |

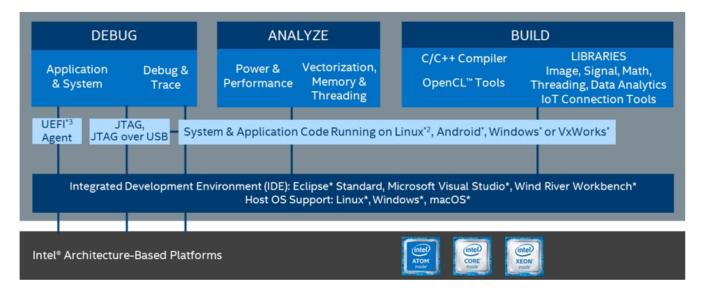

# Innovate System and IoT Apps

How to Debug, Analyze, and Build Applications More Efficiently Using Intel® System Studio

63

# **LETTER FROM THE EDITOR**

Henry A. Gabb, Senior Principal Engineer at Intel Corporation, is a longtime high-performance and parallel computing practitioner who has published numerous articles on parallel programming. He was editor/coauthor of "Developing Multithreaded Applications: A Platform Consistent Approach" and program manager of the Intel/Microsoft Universal Parallel Computing Research Centers.

# **Onward to Exascale Computing**

As you may know, I'm an old-school HPC guy—not by choice, but out of necessity. Highperformance computing (HPC) has a double meaning, depending on who you're talking to. On the one hand, it simply means improving application performance in the generic sense. Some of my friends on the compiler team see a 5% speedup as HPC. And, in their world, they're right. In my world, HPC refers to computing on a grand scale—harnessing thousands of cores to get orders of magnitude speedups. (Think **TOP500**.)

That's why I'm understandably excited about the announcement last month of the Aurora<sup>\*</sup> supercomputer Intel is collaborating on with Argonne National Laboratory. (See **U.S. Department of Energy and Intel to Deliver First Exascale Supercomputer** for the whole story.) Aurora is expected to deliver exaFLOPS performance (i.e., a quintillion, or 10<sup>18</sup>, floating-point operations per second). Exascale systems will be essential for converged workflows, as we discussed in the **last issue** of *The Parallel Universe*.

Three articles in our current issue touch on optimizations that the push to exascale demands. The Princeton Plasma Physics Laboratory is doing the type of science that will take advantage of an exascale system. Their article, **Improving Performance by Vectorizing Particle-in-Cell Codes**, describes how they fine-tuned one of their critical algorithms. **How Effective Is Your Vectorization?** shows how to take advantage of the information provided by **Intel® Advisor**. **Boost Performance for Hybrid Applications with Multiple Endpoints in Intel® MPI Library** describes enhancements that improve the scalability of applications that combine message passing and multithreading.

That's enough about HPC. What else is in this issue? The feature article, **Effectively Train and Execute Machine Learning and Deep Learning Projects on CPUs**, describes the **Intel® Math Kernel Library for Deep Neural Networks** and how it's used to accelerate AI frameworks. We also have two other articles that data scientists should find interesting: **Parallelism in Python\* Using Numba\*** and **Boosting the Performance of Graph Analytics Workloads**. The former provides practical advice on using the Numba compiler to significantly improve the performance of Python numerical kernels. The latter describes the analysis of the **GAP Benchmark Suite**, a common benchmark for graph analytics. Finally, we close this issue with a review of the analysis tools in **Intel® System Studio**: **Innovate System and IoT Apps**.

As always, don't forget to check out **Tech.Decoded**, Intel's knowledge hub for developers, for more on solutions for code modernization, visual computing, data center and cloud computing, data science, and systems and IoT development. And if you haven't already, be sure to **subscribe** to *The Parallel Universe* so you won't miss a thing.

## Henry A. Gabb

April 2019

# EFFECTIVELY TRAIN AND EXECUTE MACHINE LEARNING AND DEEP LEARNING PROJECTS ON CPUS

Meet the Intel-Optimized Frameworks that Make It Easier

Nathan Greeneltch and Jing Xu, Software Technical Consulting Engineers, Intel Corporation

When you're developing AI applications, you need highly optimized deep learning models that enable an app to run wherever it's needed and on any kind of device—from the edge to the cloud. But optimizing deep learning models for higher performance on CPUs presents a number of challenges, like:

- Code refactoring to take advantage of modern vector instructions

- Use of all available cores

- Cache blocking

- Balanced use of prefetching

- And more

These challenges aren't significantly different from those you see when you're optimizing other performance-sensitive applications—and developers and data scientists can find a wealth of deep learning frameworks to help address them. Intel has developed a number of optimized deep learning primitives that you can use inside these popular deep learning frameworks to ensure you're implementing common building blocks efficiently through libraries like Intel® Math Kernel Library (Intel® MKL).

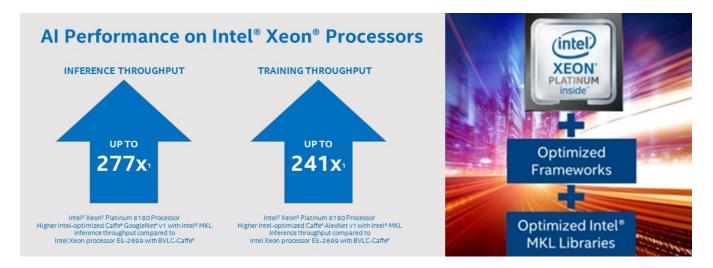

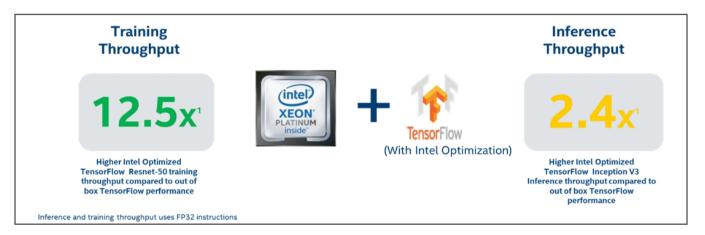

In this article, we'll look at the performance of Intel's optimizations for frameworks like Caffe\*, TensorFlow\*, and MXNet\*. We'll also introduce the type of accelerations available on these frameworks via the **Intel® Math Kernel Library for Deep Neural Networks (Intel® MKL-DNN)** and show you how to acquire and/or build these framework packages with Intel's accelerations—so you can take advantage of accelerated CPU training and inference execution with no code changes (**Figures 1** and **2**).

**1** Deliver significant AI performance with hardware and software optimizations on Intel<sup>®</sup> Xeon<sup>®</sup> Scalable processors.

2 Boost your deep learning performance on Intel Xeon Scalable processors with Intel<sup>®</sup> Optimized TensorFlow and Intel MKL-DNN.

# Intel® Math Kernel Library for DNN

Intel MKL-DNN is an open-source performance library that accelerates deep learning applications and frameworks on Intel<sup>®</sup> architectures. Intel MKL-DNN contains vectorized and threaded building blocks that you can use to implement deep neural networks (DNN) with C and C++ interfaces (**Table 1**).

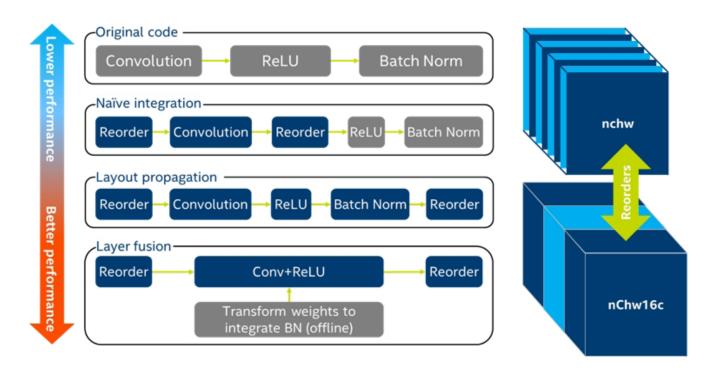

The performance benefit from Intel MKL-DNN primitives is tied directly to the level of integration to which the framework developers commit (**Figure 3**). There are reorder penalties for converting input data into Intel MKL-DNN preferred formats, so framework developers benefit from converting once and then staying in Intel MKL-DNN format for as much of the computation as possible.

Also, 2-in-1 and 3-in-1 fused versions of layer primitives are available if a framework developer wants to fully leverage the power of the library. The fused layers allow for Intel MKL-DNN math to run concurrently on downstream layers if the relevant upstream computations are completed for that piece of the data/image frame. A fused primitive will include compute-intensive operations along with bandwidth-limited ops.

| Function                        | Features                                                                                                                                                                                           |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Compute-intensive<br>operations | <ul> <li>1D, 2D and 3D spatial convolution and deconvolution</li> <li>Inner product</li> <li>General-purpose matrix-matrix multiplication</li> <li>Recurrent neural network (RNN) cells</li> </ul> |

| Memory-bound operations         | <ul> <li>Pooling</li> <li>Batch normalization</li> <li>Local response normalization</li> <li>Activation functions</li> <li>Sum</li> </ul>                                                          |

| Data manipulation               | <ul><li>Reorders/quantization</li><li>Concatenation</li></ul>                                                                                                                                      |

| Primitive fusion                | Convolution with sum and activations                                                                                                                                                               |

| Data types                      | <ul><li> fp32</li><li> int8</li></ul>                                                                                                                                                              |

#### Table 1. What's included in Intel MKL-DNN

#### **3** Performance versus level of integration and Intel MKL-DNN data format visualization

# Installing Intel MKL-DNN

Intel MKL-DNN is distributed in source code form under the Apache\* License Version 2.0. See the **Readme** for up-to-date build instructions for Linux\*, macOS\*, and Windows\*.

The VTUNEROOT flag is required for integration with **Intel<sup>®</sup> VTune<sup>™</sup> Amplifier**. The Readme explains how to use this flag.

# Installing Intel-Optimized Frameworks

# Intel® Optimization for TensorFlow\*

Current distribution channels are PIP, Anaconda, Docker, and build from source. See the **Intel® Optimization for TensorFlow\* Installation Guide** for detailed instructions for all channels.

Anaconda – Linux:

conda install -c defaults tensorflow

Anaconda – Windows:

conda install tensorflow-mkl -c defaults

## Intel<sup>®</sup> Optimization for Caffe\*

Intel has a tutorial describing how to use **Intel® Optimization for Caffe\*** to build Caffe optimized for Intel architecture, train deep network models using one or more compute nodes, and deploy networks.

```

(Ubuntu 16.04)

git clone https://github.com/intel/caffe.git

Open a Terminal window

sudo apt-get update

sudo apt-get install build-essential cmake git pkg-config

sudo apt-get install libprotobuf-dev libleveldb-dev libsnappy-dev

libhdf5-serial-dev protobuf-compiler

sudo apt-get install libatlas-base-dev

sudo apt-get install --no-install-recommends libboost-all-dev

sudo apt-get install libgflags-dev libgoogle-glog-dev liblmdb-dev

sudo apt-get install libopencv-dev

Go to Caffe root directory.

cp Makefile.config.example Makefile.config

vi Makefile.config (add the red part)

INCLUDE_DIRS := $(PYTHON_INCLUDE) /usr/local/include /usr/include/hdf5/serial

LIBRARY DIRS := $(PYTHON LIB) /usr/local/lib /usr/lib/x86 64-

linux-gnu /usr/lib/x86 64-linux-gnu/hdf5/serial

make all -j4

```

# Intel<sup>®</sup> Optimization for MXNet\*

Intel has a tutorial explaining Intel® Optimization for Apache\* MXNet.

git clone --recursive https://github.com/apache/incubator-mxnet.git cd mxnet && make -j \$(nproc) USE OPENCV=1 USE BLAS=mkl USE MKLDNN=1

# Performance Considerations and Runtime Settings

Now let's consider TensorFlow runtime settings for best performance—specifically, convolutional neural network (CNN) inference. The concepts can be applied to other frameworks accelerated with Intel MKL-DNN and other use cases. However, some empirical testing will be required. Where necessary, we'll give different recommendations for real-time inference (RTI) with batch size of 1 and maximum throughput (MxT) with tunable batch size.

# Maximum Throughput versus Real-Time Inference

Deep learning inference is usually done with two different strategies, each with different performance measurements and recommendations:

- Max Throughput (MxT) looks to process as many images per second, passing in batches of size > 1. We can achieve the best performance by exercising all the physical cores on a socket. This solution is intuitive in that we simply load up the CPU with as much work as we can, and process as many images as we can, in a parallel and vectorized fashion.

- **Real-time Inference (RTI)** is an altogether different scenario where we want to process a single image as quickly as possible. Here, we aim to avoid penalties from excessive thread launching and orchestration between concurrent processes. The strategy is to confine and execute quickly.

Let's discuss some best-known methods (BKMs) for maximizing MxT and RTI performance.

# **TensorFlow Runtime Options Affecting Performance**

These runtime options heavily affect TensorFlow performance. Understanding them will help you get the best performance out of Intel's optimizations. BKMs differ for MxT and RTI.

These runtime options heavily affect TensorFlow performance. Understanding them will help you get the best performance out of Intel's optimizations. BKMs differ for MxT and RTI. The runtime options are: {intra|inter} op parallelism threads and data layout.

## {intra|inter}\_op\_parallelism\_threads

- Recommended settings (MxT): intra\_op\_parallelism = #physical cores

- Recommended settings (RTI): intra\_op\_parallelism = #physical cores

- Recommended settings for inter\_op\_parallelism: 2

- Usage (shell): python script.py --num\_intra\_threads=cores --num\_inter\_threads=2 --mkl=True

intra\_op\_parallelism\_threads and inter\_op\_parallelism\_threads are environment variables defined in tensorflow.ConfigProto. The ConfigProto is used for configuration when creating a session. These two environment variables control number of cores to use.

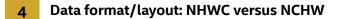

The intra\_op\_parallelism\_threads environment variable controls parallelism inside an operation. For instance, if matrix multiplication or reduction is intended to be executed in several threads, this environment variable should be set. TensorFlow will schedule tasks in a thread pool which contains intra\_op\_parallelism\_threads threads. OpenMP threads are bound to thread context as closely as possible on different cores. Setting this environment variable to the number of available physical cores is recommended.

The inter\_op\_parallelism\_threads environment variable controls parallelism among independent operations. Since these operations are not relevant to each other, TensorFlow will try to run them concurrently in the thread pool, which contains inter\_op\_parallelism\_threads threads. To minimize effects that will be brought to intra\_op\_parallelsim\_threads threads, this environment variable is recommended to be set to the number of sockets where you want the code to run. For the Intel Optimization of TensorFlow, we recommend keeping the entire execution on a single socket.

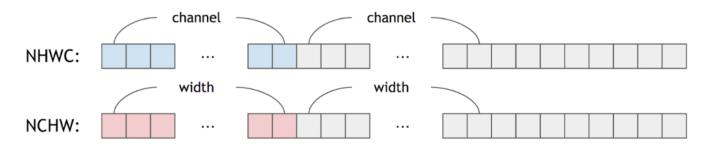

#### Data Layout

- Recommended settings: Data\_format = NCHW

- Usage (shell):

```

python

script.py --num_intra_threads=cores --num_inter_threads=2 --mkl=True

data format=NCHW

```

In modern Intel architectures, efficient use of cache and memory greatly impacts overall performance. A good memory access pattern minimizes the performance cost of accessing data in memory. To achieve this, it's important to consider how data is stored and accessed. This is usually referred as data layout. It describes how multidimensional arrays are stored linearly in the memory address space.

In most cases, data layout is represented by four letters for a two-dimensional image.

- N: Batch size, indicating number of images in a batch

- C: Channel, indicating number of channels in an image

- W: Width, indicating number of pixels in horizontal dimension of an image

- H: Height, indicating number of pixels in vertical dimension of an image

The order of these four letters indicates how pixel data are stored in 1-d memory space. For instance, NCHW indicates pixel data are stored in width-wise first, then height-wise, then channel-wise, and finally batch-wise (**Figure 4**). The data is then accessed from left to right with channels-first indexing. NCHW is the recommended data layout for Intel MKL-DNN because this is an efficient layout for the CPU. TensorFlow uses NHWC as the default data layout, but it also supports NCHW.

# NUMA Controls Affecting Performance

```

Recommended settings: --cpunodebind=0 --membind=0

```

• Usage (shell):

numactl --cpunodebind=0 --membind=0 python

script.py --num\_intra\_threads=cores --num\_inter\_threads=2 --mkl=True

data\_format=NCHW

Running on a NUMA-enabled machine brings with it special considerations. NUMA, or non-uniform memory access, is a memory layout design used in data center machines meant to take advantage of locality of memory in multi-socket machines with multiple memory controllers and blocks. The Intel Optimization for TensorFlow runs best when confining both the execution and memory usage to a single NUMA node.

# Intel MKL-DNN Technical Performance Considerations

The library takes advantage of SIMD instructions through vectorization, as well as multiple cores through multithreading. Vectorization effectively utilizes cache and the latest instruction sets. On modern Intel processors, a single core can perform up to two fused multiply and add (FMA) operations on 16 single-precision or 64 int8 numbers per cycle. Moreover, the technique of multi-threading helps in performing multiple independent operations simultaneously. Since deep learning tasks are often independent, getting available cores working in parallel is an obvious choice to boost performance.

To achieve the best possible CPU utilization, Intel MKL-DNN may use hardware-specific buffer layouts for compute-intensive operations, including convolution and inner product. All the other operations will run on the buffers in hardware-specific layouts or common layouts used by frameworks.

Intel MKL-DNN uses OpenMP to express parallelism. OpenMP is controlled by various environment variables: KMP\_AFFINITY, KMP\_BLOCKTIME, OMP\_NUM\_THREADS, and KMP\_SETTINGS. These environment variables will be described in detail in the following sections. Changing the values of these environment variables affects performance of the framework, so we highly recommend that users tune them for their specific neural network model and platform.

## KMP AFFINITY

#### • Recommended settings:

```

KMP_AFFINITY=granularity=fine,verbose,compact,1,0

```

#### • Usage (shell):

```

numactl --cpunodebind=0 --membind=0 python

script.py --num_intra_ threads=cores --num_inter_threads=2 --mkl=True

data_format=NCHW --kmp_affinity=granularity=fine,verbose,compact,1,0

```

KMP\_AFFINITY is used to restrict execution of certain threads to a subset of the physical processing units in a multiprocessor computer. Set this environment variable as follows:

KMP\_AFFINITY=[<modifier>,...]<type>[,<permute>][,<offset>]

- Modifier is a string consisting of a keyword and specifier.

- **Type** is a string indicating the thread affinity to use.

- **Permute** is a positive integer value that controls which levels are most significant when sorting the machine topology map. The value forces the mappings to make the specified number of most significant levels of the sort the least significant, and then inverts the order of significance. The root node of the tree is not considered a separate level for the sort operations.

- **Offset** is a positive integer value that indicates the starting position for thread assignment.

We'll use the recommended setting of KMP\_AFFINITY as an example to explain basic content of this environment variable:

KMP\_AFFINITY=granularity=fine,verbose,compact,1,0

The modifier is granularity=fine, verbose. The word fine causes each OpenMP thread to be bound to a single thread context, and verbose prints messages concerning the supported affinity, e.g.,

- The number of packages

- The number of cores in each package

- The number of thread contexts for each core

- OpenMP thread bindings to physical thread contexts

The word compact is the value of type, assigning the OpenMP thread <n>+1 to a free thread context as close as possible to the thread context where the <n> OpenMP thread was placed.

**Figure 5** shows the machine topology map when  $KMP\_AFFINITY$  is set to these values. The OpenMP thread <n>+1 is bound to a thread context as closely as possible to the OpenMP thread <n>, but on a different core. Once each core has been assigned an OpenMP thread, the subsequent OpenMP threads are assigned to the available cores in the same order, but they are assigned on different thread contexts.

5 Machine topology map with the setting KMP\_AFFINITY=granularity=fine, compact, 1, 0

The advantage of this setting is that consecutive threads are bound close together so that communication overhead, cache line invalidation overhead, and page thrashing are minimized. It's desirable to avoid binding multiple threads to the same core and leaving other cores not utilized. For more detailed description of KMP\_AFFINITY, see the Intel<sup>®</sup> C++ Compiler Developer Guide and Reference.

## KMP BLOCKTIME

- Recommended settings for CNN: KMP BLOCKTIME=0

- Recommended settings for non-CNN: KMP\_BLOCKTIME=1 (user should verify empirically)

- Usage (shell):

numactl --cpunodebind=0 --membind=0 python

script.py --num\_intra\_threads=cores --num\_inter\_threads=2 --mkl=True

data\_format=NCHW --kmp\_affinity=granularity=fine,verbose,compact,1,0

--kmp\_blocktime=0( or 1)

This environment variable sets the time, in milliseconds, that a thread should wait after completing the execution of a parallel region before going to sleep. Default value is 200 ms.

After completing the execution of a parallel region, threads wait for new parallel work to become available. After a certain period of time has elapsed, they stop waiting and sleep. Sleeping allows the threads to be used, until more parallel work becomes available, by non-OpenMP threaded code that may execute between parallel regions, or by other applications. A small KMP\_BLOCKTIME value may offer better overall performance if the application contains non-OpenMP threaded code that executes between parallel regions. A larger KMP\_BLOCKTIME value may be more appropriate if threads are to be reserved solely for OpenMP execution, but may penalize other concurrently-running OpenMP or threaded applications. The suggested setting is 0 for CNN-based models.

#### OMP NUM THREADS

- Recommended settings for CNN: OMP\_NUM\_THREADS = # physical cores

- Usage (shell): Export OMP\_NUM\_THREADS= # physical cores

This environment variable sets the maximum number of threads to use in OpenMP parallel regions if no other value is specified in the application. The value can be a single integer, in which case each integer specifies the number of threads for a parallel region at each nesting level. The first position in the list represents the outermost parallel nesting level. The default value is the number of logical processors visible to the operating system on which the program is executed. The recommended value equals the number of physical cores.

#### KMP SETTINGS

• Usage (shell): Export KMP\_SETTINGS=TRUE

This environment variable enables (TRUE) or disables (FALSE) the printing of OpenMP runtime library environment settings during program execution.

# Learn More

Start using Intel® optimized frameworks to accelerate your deep learning workloads on the CPU today. Check out our helpful resources on **www.intel.ai** and get support from the **Intel® AI Developer Forum**. Also, visit the new **Intel® AI Model Zoo** for solution-oriented resources for your accelerated TensorFlow\* projects. Use these resources and you can have confidence that you're using your CPU resources to their fullest capability.

#### **Configuration Note 1**

INFERENCE using FP32 Batch Size Caffe GoogleNet v1 128 AlexNet 256.

Configuration for training throughput: Tested by Intel as of 05/29/2018 Platform :2 socket Intel Xeon Platinum processor 8180 CPU @ 2.50GHz / 28 cores HT ON , Turbo ON Total Memory 376.28GB (12slots / 32 GB / 2666 MHz),4 instances of the framework, CentOS Linux-7.3.1611-Core , SSD sda RS3WC080 HDD 744.1GB,sdb RS3WC080 HDD 1.5TB,sdc RS3WC080 HDD 5.5TB , Deep Learning Framework Caffe version: a3d5b022fe026e9092fc7abc765b1162ab9940d Topology:alexnet BI OS:SE5C620.86B.00.01.0004.071220170215 MKLDNN: version: 464c268e544bae26f9b85a2acb9122c766a4c396 NoDataLayer. Measured: 1257 imgs/sec vs. Tested by Intel as of 06/15/2018 Platform: 2S Intel® Xeon® processor CPU E5-2699 v3 @ 2.30GHz (18 cores), HT enabled, turbo disabled, scaling governor set to "performance" via intel\_pstate driver, 64GB DDR4-2133 ECC RAM. BIOS: SE5C610.86B.01.01.0024.021320181901, CentOS Linux-7.5.1804 (Core) kernel 3.10.0-862.3.2.el7.x86\_64, SSD sdb INTEL SSDSC2BW24 SSD 223.6GB. Framework BVLC-Caffe: https://github.com/BVLC/caffe, Inference nd training measured with "caffe time" command. For "ConvNet" topologies, dummy dataset was used. For other topologies, data was stored on local storage and cached in memory before training. BVLC Caffe (http://github.com/BVLC/caffe), revision 2a1c552b66f026c7508d390b526f2495ed3be594

#### **Configuration Note 2**

System configuration: CPU Thread(s) per core: 2 Core(s) per socket: 28 socket(s): 2 NUMA node(s): 2 CPU family: 6 Model: 85 Model name: Intel Xeon Platinum processor 8180 CPU @ 2.50GHz HyperThreading: ON Turbo: ON Memory 376GB (12 x 32GB) 24 slots, 12 occupied 2666 MHz Disks Intel RS3WC080 x 3 (800GB, 1.6TB, 6TB) BIOS SE5C620.86B.00.01.0004. 070920180847 (microcode version 0x200004d) OS Centos Linux 7.4.1708 (Core) Kernel 3.10.0-693.11.6.el7.x86\_64 TensorFlowSource: https://github.com/tensorflow/tensorflow commit: 6a0b536a779f485edc25f6a11335b5e640acc8ab MKLDNN version: 4e333787e0d66a1dca1218e99a891d493dbc8ef1 TensorFlow benchmarks: https://github.com/tensorflow/benchmarks

# **INTEL® MATH KERNEL LIBRARY** Fast Math Processing for Intel®-Based Systems

Configurations for Inference throughput: Tested by Intel as of 6/7/2018. :Platform :two-socket Intel<sup>®</sup> Xeon<sup>®</sup> Platinum processor, 8180 CPU @ 2.50GHz /28 cores HT ON , Turbo ON. Total Memory: 376.28GB (12slots /32 GB /2666 MHz), four instances of the framework, CentOS Linux\*-7.3.1611-Core , SSD sda RS3WC080 HDD 744.1GB,sdb RS3WC080 HDD 1.5TB,sdc RS3WC080 HDD 5.5TB , Deep Learning Framework Caffe version: a3d5b022fe026e9092fc7abc7654b1162ab9940d. Topology:GoogleNet\* v1 BIOS:SE5C620.86B.00.01.0004.071220170215 MKLDNN: version: 464c268e544bae26f9b85a2acb9122c766a4c396 NoDataLayer. Measured: 1449 imgs/sec vs Tested by Intel as of 06/15/2018 Platform: 2S Intel<sup>®</sup> Xeon<sup>®</sup> processor CPU E5-2699 v3 @ 2.30GHz (18 cores), HT enabled, turbo disabled, scaling governor set to "performance" via intel\_pstate driver, 64GB DDR4-2133 ECC RAM. BIOS: SE5C610.86B.01.01.0024.021320181901, CentOS Linux-7.5.1804(Core) kernel 3.10.0-862.3.2.eI7.x86\_64, SSD sdb INTEL SSDSC2BW24 SSD 223.6GB. Framework BVLC-Caffe: https://github.com/BVLC/caffe, Inference & Training measured with "caffe time" command. For "ConvNet" topologies, dummy dataset was used. For other topologies, data was stored on local storage and cached in memory before training. BVLC Caffe (http://github.com/BVLC/caffe), revision 2a1c552b66f026c7508d390b526f2495ed3be594.

# PARALLELISM IN PYTHON\* USING NUMBA\*

It Just Takes a Bit of Practice and the Right Fundamentals

David Liu, Software Technical Consulting Engineer, Intel Corporation

Obtaining parallelism in Python\* has been a challenge for many developers. In **issue 35 of** *The Parallel* **Universe**, we explored the basics of the Python language and the key ways to obtain parallelism. In this article, we'll explore how to achieve parallelism through Numba\*.

There are three key ways to efficiently achieve parallelism in Python:

- 1. Dispatch to your own native C code through Python's ctypes or cffi (wrapping C code in Python).

- 2. Rely on a library that uses advanced native runtimes, such as NumPy or SciPy.

- **3. Use a framework** that acts as an engine to generate native-speed code from Python or symbolic math expressions.

All three methods escape the global interpreter lock (GIL), and do so in a way that's accepted within the Python community. The Numba framework falls under the third method, because it uses just-in-time (JIT) and low-level virtual machine (LLVM) compilation engines to create native-speed code.

The first requirement for using Numba is that your target code for JIT or LLVM compilation optimization must be enclosed inside a function. After the initial pass of the Python interpreter, which converts to bytecode, Numba will look for the decorator that targets a function for a Numba interpreter pass. Next, it will run the Numba interpreter to generate an intermediate representation (IR). Afterwards, it will generate a context for the target hardware, and then proceed to JIT or LLVM compilation. The Numba IR is changed from a stack machine representation to a register machine representation for better optimization at runtime. From there, the range of options and parallelism directives opens up.

In the following example, we're using pure Python to give Numba the best chance to optimize without having to specify directives:

```

import array

import random

from numba import jit

a = array.array('1', [random.randint(0,10) for x in range

(0, 10000000)])

@jit(nopython=True, parallel=True)

def ssum(x):

total = 0

for items in x:

total+=items

return total

%timeit sum(a)

111 ms \pm 861 µs per loop (mean \pm std. dev. of 7 runs, 10 loops each)

%timeit ssum(a)

4.2 ms ± 108 µs per loop (mean ± std. dev. of 7 runs, 100 loops each)

# Nearly 26X faster!

```

#### < The Parallel Universe</p>

Pure CPython bytecode is easier for the Numba interpreter to deal with compared to mixed CPython and NumPy code. The @jit decorator tells Numba to create the IR, and then a compiled variant, before running the function. Note the nopython attribute on the decorator. This means that we don't want to fall back to stock interpreter behavior if Numba fails to convert the code (more on this later). We used Python arrays instead of lists because they compile better to Numba. We also created a custom summation function because Python's standard sum has special iterator properties that won't compile in Numba.

The previous example works well for general Python. But what if your code requires the use of scientific or numerical packages like NumPy or SciPy? Take, for example, the following code that calculates a resistor-capacitor (RC) time constant for a circuit:

```

import numpy as np

test_voltages = np.random.rand(1,1000)*12

test_constants = np.random.rand(1,1000)

def filter_time_constant(voltage, time_constant):

return voltage * (1-np.exp(1/time_constant))

%timeit filter_time_constant(test_voltages, test_constants)

11.2 µs ± 145 ns per loop (mean ± std. dev. of 7 runs, 100000 loops each)

```

In this case, we'll use the @vectorize decorator instead of @jit because of NumPy's implementation of ufuncs:

```

from numba import vectorize

@vectorize

def v_filter_time_constant(voltage, time_constant):

return voltage * (1-np.exp(1/time_constant))

%timeit v_filter_time_constant(test_voltages, test_constants)

4.74 µs ± 46.8 ns per loop (mean ± std. dev. of 7 runs, 100000 loops

each)

# Over 2x faster!

```

When dealing with specialized frameworks such as NumPy and SciPy, Numba is not only dealing with Python, but also with a special type of primitive in the NumPy/SciPy stack called a ufunc, which normally means one would need to create a NumPy ufunc with C code—a difficult proposition. In this case, the np.exp() is a good candidate, since it's a transcendental function and can be targeted by the Intel® Compiler's Short Vector Math Library (SVML) in conjunction with Numba. Both @vectorize and @guvectorize can use Intel's SVML library and help with NumPy ufuncs.

While Numba does have good ufunc coverage, it's also important to understand that not every NumPy or SciPy codebase will optimize well in Numba. This is because some NumPy primitives are already highly optimized. For example, numpy.dot() uses the Basic Linear Algebra Subroutines (BLAS), an optimized C API for linear algebra. If the Numba interpreter is used, it will actually produce a slower function because it can't optimize the BLAS function any further. To use the ufunc optimally in Numba, we'd need to look for a stacked NumPy call, in which many operations to an array or vector are compounded. For example:

```

%timeit np.exp(np.arcsin(np.random.rand(1000)))

19.6 µs ± 85.9 ns per loop (mean ± std. dev. of 7 runs, 100000 loops

each)

@jit(nopython=True)

def test_func(size):

np.exp(np.arcsin(np.random.rand(1000)))

%timeit test_func(1000)

16 µs ± 80.2 ns per loop (mean ± std. dev. of 7 runs, 100000 loops each)

```

The Numba @jit performance is slightly better than the straight NumPy code because this computation has not one, but three, NumPy computations. Numba can analyze the ufuncs and detect the best vectorization and alignment better than NumPy itself can.

Another area to tweak Numba's compilation directives and performance is using the advanced compilation options. The main options used are nopython, nogil, cache, and parallel. With the @jit decorator, Numba attempts to choose the best method to optimize the code given to it. However, if the nature of the code is better known, you can directly specify a compilation directive.

The first option is nopython, which prevents the compilation from falling back to Python object mode. If the code is unable to convert, it will instead throw an error to the user. The second option is

nogil, which releases the GIL when not processing non-object code. This option assumes you've thought through multithreaded considerations such as consistency and race conditions. The cache option stores the compiled function in a file-based cache to avoid unnecessary compilation the next time Numba is invoked on the same function. The parallel directive is a CPU-tailored transformation to known reliable primitives such as arrays and NumPy computations. This option is a good first choice for kernels that do symbolic math.

Stricter function signatures improve the opportunities for Numba to optimize the code. Defining the expected datatype for each parameter in the signature gives the Numba interpreter the necessary information to find the best machine representation and memory alignment of the kernel. This is similar to providing static types for a C compiler. The following examples show how to provide type information to Numba:

```

@jit(int32(int32, int32))

# Expecting int32 values when being processed

@jit([(int64[:], int64, int64[:])]

# Expecting int64 arrays values when being processed

@vectorize([float64(float64, float64)])

# Expecting float64 values when being processed

```

In general, accessing parallelism in Python with Numba is about knowing a few fundamentals and modifying your workflow to take these methods into account while you're actively coding in Python. Here are the steps in the process:

- **1. Ensure the abstraction of your core kernels is appropriate.** Numba requires the optimization target to be in a function. Unnecessarily complex code can cause the Numba compilation to fall back to object code.

- **2.** Look for places in your code where you see processing data in some form of a loop with a known datatype. Examples would be a for-loop iterating over a list of integers, or an arithmetic computation that processes an array in pure Python.

- **3. If you're using NumPy and SciPy, look at computations that can be stacked in a single statement and that are not BLAS or LAPACK functions.** These are prime candidates for using the ufunc optimization capabilities of Numba.

- Experiment with Numba's compilation options.

- Determine the intended datatype signature of the function and core code. If it's known (such as int8 or int32), then inform Numba about which input datatype parameters it should expect.

Achieving parallelism with Numba just takes a bit of practice and the right fundamentals. Getting both the performance advantages of stepping out of the GIL while having maintainable code is a testament to the Python community's hard work in the scientific computing space. Numba is one of the best tools to achieve performance and exploit parallelism so it should be in every Python developer's toolkit.

# **BLOG HIGHLIGHTS**

# Intel<sup>®</sup> Graphics Performance Analyzers 2019 R1 Release GISELLE G., INTEL CORPORATION

Say hello to some of the latest features for the Intel<sup>®</sup> Graphics Performance Analyzers (Intel<sup>®</sup> GPA) tool suite.

- Vulkan Support in Frame Analyzer Stream Capture: Capture the lifetime of an application through Multiframe Stream capture. Use keyframe functionality to create "save points" that allow for quicker playback time during profiling and can be used to signify rendering anomalies at capture.

- Edit Shaders: Quickly iterate over shader code changes, without leaving the application or recompiling code.

Read more >

# **BOOSTING THE PERFORMANCE OF GRAPH ANALYTICS WORKLOADS**

# Analyzing the Graph Benchmarks on Intel® Xeon® Processors

Stijn Eyerman, Wim Heirman, and Kristof Du Bois, Research Scientists, and Joshua B. Fryman and Ibrahim Hur, Principal Engineers, Intel Corporation

A graph is an intuitive way of representing a big data set and the relationships between its elements. Each vertex represents an element, and edges connect related elements. Representing data sets as a graph means you can build on the rich history of graph theory. And there are a variety of algorithms to extract useful information from a graph. In this article, we'll explore the implementation characteristics of basic graph analysis algorithms and how they perform on **Intel® Xeon™ processors**.

# Graphs and Graph Analytics

A graph is a structured representation of a data set with relationships between elements. Each element is represented as a vertex, and relationships between elements are shown as an edge between two vertices. Both vertices and edges can have attributes representing either the characteristics of the element or the relationship. The vertices to which a vertex is connected through edges are called its neighbors, and the number of neighbors is called the degree of a vertex.

Graph analysis applications extract characteristics from a graph (or multiple graphs) that provide useful information, e.g.:

- Vertices with specific features

- The shortest path between vertices

- Vertex clusters

- Higher-order relationships among vertices

With the growing availability of big data sets and the need to extract useful information from them, graph analytics applications are becoming an important workload, both in the data center and at the edge.

For this study, we'll use the GAP Benchmark Suite<sup>1</sup>, a set of common graph algorithms implemented in C++ and optimized by researchers at the University of California at Berkeley for performance on sharedmemory multicore processors (**Table 1**). We evaluate GAP performance on an Intel Xeon processor-based server and investigate opportunities to further improve performance.

| Algorithm                   | Abbreviation | What it Does                                                                               |

|-----------------------------|--------------|--------------------------------------------------------------------------------------------|

| PageRank*                   | pr           | Calculates the popularity of a vertex by aggregating the popularity of its neighbors       |

| Triangle counting           | tc           | Counts the number of triangles (three vertices that are fully connected)                   |

| Connected components        | сс           | Splits the graph into subgraphs with no edges between them                                 |

| Breadth-first search        | bfs          | Walks through the graph in breadth-first order                                             |

| Single-source shortest path | sssp         | Calculates the shortest path from one vertex to all others                                 |

| Betweenness centrality      | bc           | Calculates the centrality of a vertex, determined by how many shortest paths go through it |

#### Table 1. Gap Benchmark Suite overview

# **Characteristics of Graph Algorithms**

Graph algorithms pose challenging behavior for conventional processor architectures. A typical operation is to fetch the attributes of all neighbors of a vertex. The list of neighbors, determined by the topology of the graph, is usually irregular. This leads to sparse memory accesses—accessing individual elements scattered on a large data structure. Sparse memory accesses have no locality, leading to poor cache utilization.

Fetching the attributes of the neighbors means using indirect accesses. For example, if N is the array of neighbors of a vertex, and A the array containing the attributes, the attribute of neighbor i is accessed by A[N[i]]. This pattern is difficult to predict and to vectorize, which leads to an underutilization of the available compute and memory resources.

On the other hand, graph algorithms generally have a lot of parallelism. The set of algorithms in the GAP suite fall into two categories in terms of parallelism. The first category consists of algorithms that operate on all vertices concurrently (pr, tc, and cc). They have abundant parallelism and can be executed across many threads. Their parallelism is only limited by the size of the graph.

The second category is front-based algorithms where, at each iteration, a subset of vertices is analyzed (the current front) and a new front is defined to be processed in the next iteration (bfs, sssp, and bc). These algorithms usually start with a front containing a single vertex. The next front consists of its neighbors, then the neighbors of these neighbors, and so on. In the first iterations, the size of the front (and thus the parallelism that can be exploited) is limited. Also, each iteration ends with a global barrier, which creates additional synchronization overhead. These algorithms scale worse with increasing thread count, especially on smaller graphs.

# Running Graph Algorithms on Intel Xeon Processors

Despite the challenging behavior of graph algorithms, there are ways to increase the efficiency of running these applications on a multi-core Intel Xeon processor-based server.

# Vectorization

Using vector memory instructions can increase the performance of a graph algorithm by increasing the number of parallel load operations, which hides part of their latency. Specifically, you can use the vector gather instruction (AVX2\* and AVX-512\*) to perform multiple indirect loads in one instruction. However, the compiler isn't always able to detect these indirect access patterns, or it can decide to not vectorize based on its heuristics. Therefore, it might be useful to add #pragma vector always to force the compiler to vectorize and/or to rewrite the code to make the indirect access pattern more apparent to the compiler.

**Figure 1** gives an example for cc. The original code on the left did not generate vector gather instructions, while the code on the right did. This led to a speedup of 5x for cc on Intel Xeon processors.

```

for (NodeID v : g.out_neigh(u)) {

NodeID comp_v = comp[v];

if ((comp_u < comp_v) &&

(comp_v == comp[comp_v])) {

change = true;

comp[comp_v] = comp_u;

}

}</pre>

```

```

NodeID *a = g.out_neigh(u).begin();

#pragma vector always

for (int i=0; i<n; i++) {

NodeID comp_v = comp[a[i]];

if ((comp_u < comp_v) &&

(comp_v == comp[comp_v])) {

change = true;

comp[comp_v] = comp_u;

}

}</pre>

```

1 Inner loop of connected components. On the left is the original code, which didn't generate vector gather instructions. On the right is the altered code, which makes the indirect pattern clearer and forces the compiler to vectorize.

It might also be useful to look at other vectorization opportunities, and to rewrite the code so that they can be exploited (e.g., using intrinsics). For example, in tc, we need to count the number of matches between the elements of two neighbor lists. Katsov describes an algorithm to speed up the matching algorithm with SSE instructions<sup>2</sup>. We adapted this algorithm to AVX-512 and included this in the tc benchmark, leading to a performance increase of 2.5x (code not included for brevity).<sup>3</sup>

# Parallelism

The GAP benchmarks are parallelized using OpenMP\*. As discussed before, there are two categories of parallelism: vertex- and front-based. For the vertex-parallel algorithms (pr, cc, and tc), it's important to use dynamic scheduling in the OpenMP parallel for-loops because the processing time of a vertex depends on its neighbor count, which can differ significantly across vertices. With static scheduling, threads that are assigned vertices with many neighbors execute longer than other threads—leading to load imbalance. To reduce the scheduling overhead while still maintaining enough scheduling flexibility, set chunk size to 16 or 32.

The front-based algorithms (bfs, sssp, and bc) are harder to parallelize, which means they don't use the full capacity of the processor (fewer threads than cores). The current front contains many fewer vertices than the full graph, and the next front can only be processed when the current front is finished. To fully exploit the increasing core count of Intel Xeon processor-based servers, these algorithms need to be revised to increase their parallelism.

An example of this is already implemented in bfs. Instead of looking for neighbors of the current front and checking whether they've already been visited (forward algorithm), all non-visited vertices are considered, and it is checked whether they are a neighbor of a vertex in the current front (backward algorithm). Because there are more non-visited vertices than vertices in the front, there's more parallelism to exploit. The downside is that the backward algorithm sometimes does unnecessary work when most of the non-visited vertices are not neighbors of the current front.

At each step of the algorithm, we can choose between the two methods. This choice is currently done using the characteristics of the current front and the remaining vertices, but it should also include the available parallelism (core or thread count) to better exploit the capacity of the processor.

# **Caches and Input Graphs**

Graph workloads generally don't generate cache-friendly access patterns. The one exception is when the graph, or the most accessed data structure of the graph (e.g., the attributes of vertices), fits in the last-level cache (which is up to 38 MB per socket on high-end Intel Xeon processors). From our experiments, we notice that performance (expressed in GTEPS, or giga traversed edges per second) decreases with increasing graph size, since less and less of the data fits into the cache. Because of the nature of graphs and graph algorithms, methods to improve cache locality either don't work well or take too much time to reorganize the graph, often more than the algorithm itself.

# **Distributed Graph Processing**

The GAP benchmarks are designed for single-node execution only (using OpenMP parallelization). However, based on the insights from our study, we briefly discuss the impact on distributed graph processing (i.e., using multiple nodes). For high-performance multinode execution, it's crucial to minimize the communication and maximize local data and computation. This is challenging for graph applications because of the irregular and non-localized access pattern. Partitioning a graph to minimize the number of edges between partitions is an NP-complete problem in itself, and often leads to more compute time than the algorithm itself. Therefore, when you're deploying a graph analysis algorithm on multiple nodes, the nodes should be connected by a high-bandwidth, low-latency network such as Intel<sup>®</sup> Omni-Path Architecture to deal with the unavoidably high amount of communication between the nodes.

# **Boosting Performance through Analysis**

Graph applications form a challenging workload for current processors because of their memory intensiveness and irregularity. By carefully crafting their implementation and exploiting vector units and thread parallelism, we can increase performance significantly. However, more investigation is needed, including redesigning the algorithms to fully exploit the capabilities of an Intel Xeon processor-based server, especially when moving to distributed processing.

# References

1. S. Beamer, K. Asanovic, and D. A. Patterson, "The GAP Benchmark Suite," 2015. http://gap.

#### cs.berkeley.edu/benchmark.html

- 2. I. Katsov, "Fast Intersection of Sorted Lists Using SSE Instructions," 2012. https://highlyscalable. wordpress.com/2012/06/05/fast-intersection-sorted-lists-sse/

- 3. S. Eyerman et al., "Many-Core Graph Workload Analysis," 2018. https://dl.acm.org/citation. cfm?id=3291686.

# **BLOG HIGHLIGHTS**

#

The latest release of Intel<sup>®</sup> Distribution of OpenVINO<sup>™</sup> toolkit 2019 (which stands for open visual inference and neural network optimization) unveils new features that improve parallelization, extend deep learning capabilities, and provides support for macOS\*. Get a quick view of the major new enhancements. Then learn more about new parallelization capabilities that deliver optimal performance for multi-network scenarios.

#### New Features in 2019 R1

Supports 2nd generation Intel<sup>®</sup> Xeon<sup>®</sup> Processors (codenamed Cascade Lake) and provides performance speedup for inference through Intel<sup>®</sup> Deep Learning Boost (VNNI instruction set).

Read more >

# **HOW EFFECTIVE IS YOUR VECTORIZATION?**

Gain Insights into How Well Your Application is Vectorized Using Intel<sup>®</sup> Advisor

Kevin O'Leary, Technical Consulting Engineer, Intel Corporation

Determining how well your application is vectorized is crucial to getting the best performance on your system. In this article, we'll show how to pinpoint vectorization issues, see how well you're using your hardware, and optimize performance using Intel<sup>®</sup> Advisor, which is available in a free, standalone version and as part of both Intel<sup>®</sup> Parallel Studio XE and Intel<sup>®</sup> System Studio.

Intel Advisor helps you to see:

- Which loops are vectorized

- Data types, vector widths, and instruction sets (e.g., AVX-512, AVX2)

- How many floating-point and/or integer operations are executed

- How many instructions were devoted to computation and how many to memory operations

- Your register utilization

- How to improve your vectorization

- And much more

# **Getting Great Performance**

To get top performance out of your application, you need information on how well you're using all the resources of the system. Intel Advisor's new and improved summary view (**Figure 1**) gives you an indication of how well the application is performing as a whole.

| Elapsed Time<br>Vector Instruction Set<br>Number of CPU Threads                | 154.92s<br>AVX512, AVX2<br>1                                           | 2, AVX | , SSE2, SSE |                                     | <ul> <li>INT+FLOAT Giga OPS</li> <li>GFLOPS</li> <li>GINTOPS</li> </ul> | 11.89<br>10.16<br>1.72 |                       |

|--------------------------------------------------------------------------------|------------------------------------------------------------------------|--------|-------------|-------------------------------------|-------------------------------------------------------------------------|------------------------|-----------------------|

| Effective Program Ch                                                           | aracteristics                                                          |        | Utiliza     | tion                                | Hardware Peak                                                           |                        |                       |

| > GFLOPS                                                                       | 10                                                                     | ).16   | 10%         | out of                              | 100.1 (DP) FLOPS<br>201.7 (SP) FLOPS                                    |                        |                       |

| > GINTOPS                                                                      | 1.                                                                     | 723    | 3.2%        | out of                              | 53.94 (Int64) INTOPS<br>106.2 (Int32) INTOPS                            |                        |                       |

| > CPU <-> Memory [L1·                                                          | +NTS GB/s] 34                                                          | 4.71   | 1.2e+3%     | out of                              | 450.6 GB/s [bytes]                                                      |                        |                       |

| Performance ch                                                                 | aractoristics                                                          |        |             | outor                               | 430.0 00/3 [bytes]                                                      |                        |                       |

| Performance ch<br>Metrics                                                      | aracteristics                                                          |        |             | Total                               | 450.0 OD/s [bytes]                                                      |                        |                       |

| 0                                                                              | aracteristics                                                          |        |             |                                     | 450.0 OD/s [bytes]                                                      |                        | 100%                  |

| Metrics                                                                        |                                                                        |        |             | Total                               | 430.0 OD/s [bytes]                                                      |                        |                       |

| Metrics<br>Total CPU time                                                      | ed loops                                                               |        |             | T <b>otal</b><br>154.55s            |                                                                         |                        |                       |

| Metrics<br>Total CPU time<br>Time in <b>3</b> vectorize                        | ed loops<br>e                                                          |        |             | T <b>otal</b><br>154.55s<br>142.89s |                                                                         |                        | 100%<br>92.5%<br>7.5% |

| Metrics<br>Total CPU time<br>Time in <b>3</b> vectorize<br>Time in scalar code | ed loops<br>e<br><b>ain/Efficiency</b><br>Gain/Efficiency <sup>G</sup> | 1      |             | T <b>otal</b><br>154.55s<br>142.89s | 430.0 0D/s [bytes]                                                      |                        | 92.5                  |

1

Intel Advisor summary view

You can see the vectorization instruction sets used and some useful performance metrics. This view now includes a program characteristics section, which compares your relative performance to the peak performance obtainable on your system. In **Figure 1**, notice that the application is using several different instruction sets—something we should investigate. Also notice that the program is getting vectorization efficiency of just 42%. Where did we lose 58% of our efficiency? We can drill down to investigate.

# **Drilling Down**

You can get more detail in the survey and roofline tab (**Figure 2**). The survey view gives details on a loopby-loop basis. Focus on the loops where you're spending the most time, and try to get these loops to vectorize as efficiently as possible. Intel Advisor highlights whether the loop is vectorized and its efficiency. If the compiler wasn't able to vectorize the loop, Intel Advisor can tell you why. The performance issues column can give you clues as to why efficiency is poor.

| 📰 Si     | ummary 🤣 Survey & Roofline 📲 Refine   | ement Reports      |             |            |                   |                          |                  |            |

|----------|---------------------------------------|--------------------|-------------|------------|-------------------|--------------------------|------------------|------------|

| 8        | + - Function Call Sites and Loops     | @ Performance      | CPU Time 🔊  |            | Turne             | Miles No Vestosiantion2  | Vectorized Loops |            |

| ROOFLINE | + - Function Call Sites and Loops     | Issues             | Self Time 🔫 | Total Time | Туре              | Why No Vectorization?    | Vecto            | Efficiency |

| Ĩ        | 🕂 💍 [loop in matvec at Multiply.c:69] | 💡 1 Ineffective pe | 119.010s 📩  | 119.010s 🔛 | Vectorized (Body  | 1 vectorization possibl  | AVX5             | 16%        |

|          | 🗵 💆 [loop in matvec at Multiply.c:60] |                    | 29.500s     | 29.500s    | Vectorized (Body) |                          | AVX2             | ~100%      |

|          | 🕀 💆 [loop in matvec at Multiply.c:82] | @ 1 Misaligned lo  | 22.610s     | 22.610s    | Vectorized (Body) |                          | AVX2             | 71%        |

|          | 🛨 🗂 [loop in matvec at Multiply.c:49] |                    | 11.720s     | 182.840s   | Scalar Versions   | 1 inner loop was already |                  |            |

# 2 Survey and rooftop tab

# Instruction Set Analysis

Instruction set analysis (**Figure 3**) takes a deep dive into what the compiler did to vectorize your code. It shows the:

- Vectorization instruction set used

- Vector widths

- Data type being operated on

The traits column generally indicates the memory manipulation the compiler had to do to fit your data structure into a vector. These memory manipulations can be indicators of poor efficiency.

| + - Function Call Sites and Loops     | Instruction Set Analysis    |          |       |               |                             |  |

|---------------------------------------|-----------------------------|----------|-------|---------------|-----------------------------|--|

| + - Function Call Sites and Loops     | Traits                      | Data Ty  | Numb  | Vector Widths | Instruction Sets            |  |

| 🕀 🝊 [loop in matvec at Multiply.c:69] | FMA; Inserts; Unpacks       | Float32  | 12; 2 | 128/256       | AVX; AVX512F_256            |  |

| 🖻 🝊 [loop in matvec at Multiply.c:60] | FMA                         | Float32  |       | 256           | AVX; FMA                    |  |

| 🕀 🝊 [loop in matvec at Multiply.c:82] | FMA                         | Float32  |       | 256           | AVX; FMA                    |  |

| ⊕ 🖱 [loop in matvec at Multiply.c:49] | Extracts; Shuffles          | Float32; |       | 128/256       | AVX; AVX2; AVX512F_256      |  |

|                                       | Extracts; FMA; Inserts; Shu | Float32; |       | 128/256       | AVX; AVX2; AVX512F_256; FMA |  |

#### 3 Instruction set analysis

In our example application, the main loop is using **Intel® AVX-512**, but the vector widths are only 128 and 256. Also, Intel Advisor gives you a warning message if your application seems to be underperforming, and offers tuning advice (**Figure 4**).

#### Your application might be underperforming

Your application might be underperforming due to disabled zmm registers by default. To define a level of zmm registers, use the **-qopt-zmm-usage** option. Refer to <u>Compiler Guide</u> for more information.

#### 4 Warning message

Recompiling to enable the ZMM registers yields the instruction set analysis in **Figure 5**. Most of our loops now use the complete 512 bytes of the vector registers. In our example, using the ZMM registers improved performance. However, this isn't always the case. It's application-specific.

| + - Function Call Sites and Loops     | Instruction Set Analysis   |            |               |                               |  |

|---------------------------------------|----------------------------|------------|---------------|-------------------------------|--|

| + - Function Call sites and Loops     | Traits                     | Data Ty    | Vector Widths | Instruction Sets              |  |

| op in matvec at Multiply.c:69] 🖉 🖉    | FMA; Inserts; Unpacks      | Float32    | 128/256       | AVX; AVX512F_128; AVX512F_256 |  |

| ± ♂ [loop in matvec at Multiply.c:49] | Extracts; FMA; Gathers; Ma | Float32;   | 128/256/512   | AVX; AVX512F_256; AVX512F_512 |  |

| ⊇ 🖔 [loop in matvec at Multiply.c:60] | FMA                        | Float32    | 512           | AVX512F_512                   |  |

| ± 🖞 [loop in matvec at Multiply.c:82] | FMA                        | Float32; I | 512           | AVX512F_512                   |  |

| ש 🖑 [loop in main at Driver.c:155]    | Type Conversions           | Float32;   |               |                               |  |

#### 5 Instruction set analysis

# Using the Middle Part of the Intel Advisor GUI

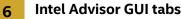

The tabs in the middle of the Intel Advisor GUI contain a wealth of program information (Figure 6).

The recommendations tab is a great way to get tips to improve performance (**Figure 7**). For instance, if a loop didn't vectorize, the vectorization tab can tell you why, along with providing code examples showing how to fix the issue.

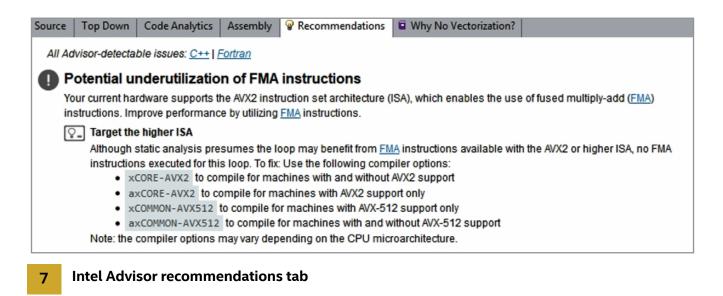

# **Code Analytics**

The code analytics tab (**Figure 8**) gives details about what's happening in a loop. You can see your performance at a high level or get statistics for all operations and an instruction mix summary.

| Source                                                                                                                  | Top Down | Code Analytics            | Assembly              | Recommendations     | Why No Vectorization?                     |                                |                             |

|-------------------------------------------------------------------------------------------------------------------------|----------|---------------------------|-----------------------|---------------------|-------------------------------------------|--------------------------------|-----------------------------|

|                                                                                                                         |          | Loop in ma                | 7                     | iply.c:69<br>1.682s | Averag                                    | e Trip Counts: <sup>®</sup> 58 |                             |

|                                                                                                                         |          | Vectorized (Bo            | dy) Total t           | time                | GFLOF                                     | PS: 4.29                       |                             |

| AVX; AVX512F_128; 101.682s<br>AVX512F_256 Self time<br>Instruction Set                                                  |          |                           |                       |                     | GINTOPS: 1.34<br>AVX-512 Mask Usage: 100% |                                |                             |

| <ul> <li>► Static Instruction Mix Summary<sup>®</sup></li> <li>► Dynamic Instruction Mix Summary<sup>®</sup></li> </ul> |          |                           |                       | Summary®            | <b>39%</b> Vec                            | ctorization Efficiency         | 3.10x<br>Vectorization Gain |

| CPU Total Time                                                                                                          |          |                           |                       |                     |                                           |                                |                             |

|                                                                                                                         | 3        | 3.73009e-09<br>Per Iterat | 9s 2.16<br>ion Per In |                     |                                           |                                |                             |

8 Intel Advisor code analytics tab

# Statistics for All Operations

You can get statistics for all operations, including floating-point (FLOPS), integer (INTOP), or mixed (INT+FLOAT) operations (**Figure 9**). This gives you a detailed view of some key performance metrics, showing how many instructions are executing per second. This view also gives you metrics on how well you're using the memory hierarchy in this loop.

| Statistics for Al             | Statistics for All Operations 🔹 📀 |               |              |  |  |  |  |  |  |

|-------------------------------|-----------------------------------|---------------|--------------|--|--|--|--|--|--|

| And Data Transfers            |                                   | Self (        | Total        |  |  |  |  |  |  |

|                               | Per loop                          | Per Iteration | Per Instance |  |  |  |  |  |  |

| GFLOP <sup>②</sup>            | 4.36e+02                          | 1.60e-08      | 9.28e-07     |  |  |  |  |  |  |

| GFLOPS <sup>®</sup>           |                                   | 4.29          |              |  |  |  |  |  |  |

| AI <sup>®</sup>               |                                   | 0.25          |              |  |  |  |  |  |  |

| Mask Utilization <sup>®</sup> |                                   | 100%          |              |  |  |  |  |  |  |

| GINTOP <sup>®</sup>           | 1.36e+02                          | 5.00e-09      | 2.90e-07     |  |  |  |  |  |  |

| GINTOPS <sup>®</sup>          |                                   | 1.34          |              |  |  |  |  |  |  |

| INT AI <sup>®</sup>           |                                   | 0.08          |              |  |  |  |  |  |  |

| Mask Utilization <sup>③</sup> |                                   | -             |              |  |  |  |  |  |  |

| INT+FLOAT OP <sup>③</sup>     | 5.72e+02                          | 2.10e-08      | 1.22e-06     |  |  |  |  |  |  |

| INT+FLOAT OPS <sup>③</sup>    |                                   | 5.63          |              |  |  |  |  |  |  |

| INT+FLOAT AI <sup>®</sup>     |                                   | 0.33          |              |  |  |  |  |  |  |

| Mask Utilization <sup>®</sup> |                                   | 100%          |              |  |  |  |  |  |  |

| L1 Gb <sup>③</sup>            | 1.74e+03                          | 6.40e-08      | 3.71e-06     |  |  |  |  |  |  |

| L1 Gb/s <sup>③</sup>          |                                   | 17.16         |              |  |  |  |  |  |  |

| Elapsed Time <sup>®</sup>     | 1.02e+02s                         | 3.73e-09s     | 2.16e-07s    |  |  |  |  |  |  |

#### 9 Statistics for all operations

# How Many Operations Are You Executing?

What are the types of instructions in your loop? Are they compute- or memory-based? Intel Advisor can answer these questions, and give you both the static and dynamic instruction count, with the static instruction mix summary (**Figure 10**). You get the percentage of each instruction you're executing, so you can see if you're really using the newest instructions where you should be.

### **10** Static instruction mix summary

# **Optimizing Vectorization**

It's crucial to optimize the vectorization of your program. Understanding how well your program is vectorized by using a tool like Intel Advisor can help you make sure you're getting the most out of your hardware.

# **Related Articles**

- Intel Advisor Roofline

- Intel Advisor Integer Roofline

- Intel Advisor Integrated Roofline

# Image: Note of the sector of

Download free Intel® Performance Libraries and start creating better, more reliable, and faster applications now.

FREE DOWNLOAD

For more complete information about compiler optimizations, see our Optimization Notice at <u>softwore intel.com/articles</u> opti-Intel and the Intel logo are trademarks of Intel Corporation or its subsidiaries in the U.S. and/or other countries. \*Other names and brands may be claimed as the property of others. © Intel Corporation

# IMPROVING PERFORMANCE BY VECTORIZING PARTICLE-IN-CELL CODES

#### **A Practical Guide**

Bei Wang, HPC Software Engineer, Princeton University; Carlos Rosales-Fernandez, Software Technical Consulting Engineer, Intel Corporation; and William Tang, Professor, Princeton Plasma Physics Laboratory

The basic particle method is a well-established approach to simulating the behavior of charged particles interacting with each other through pairwise electromagnetic forces. At each step, the particle properties are updated according to these calculated forces. For applications on powerful modern supercomputers with deep cache hierarchies, a pure particle method is efficient with respect to both locality and arithmetic intensity (compute-bound).

Unfortunately, the O(N<sup>2</sup>) complexity makes a particle method impractical for plasma simulations using millions of particles per process. Instead of calculating O(N<sup>2</sup>) forces, the particle-in-cell (PIC) method uses a grid as the medium to calculate long-range electromagnetic forces. This reduces the complexity from

O(N<sup>2</sup>) to O(N + M log M), where M is the number of grid points, generally much smaller than N. However, achieving high parallel and architectural efficiency is a significant challenge for PIC methods due to the gather/scatter nature of the algorithm.

Attaining performance becomes even more complex as HPC technology moves to the era of multi- and many-core architectures with increased thread and vector parallelism on shared memory processors. A deep understanding of how to improve the associated scalability will have a wide-ranging influence on numerous physical applications that use particle-mesh algorithms—including molecular dynamics, cosmology, accelerator physics, and plasma physics.

This article is a practical guide to improving performance by enabling vectorization for PIC codes.

#### **Optimization for PIC Codes**

The code example we use for this demonstration is the particle class in Athena++, an astrophysical magnetohydrodynamics (MHD) code written in C++ <sup>1</sup>. The particle class encapsulates basic data structures and functions in PIC methods. Particle properties are represented by phase space position—that is, physical space position (x1, x2, x3) and velocity (v1, v2, v3). The class functions implement three essential particle-based operations in PIC methods:

- 1. Deposit: Charge deposition from particles onto grid

- **2. Move:** Interpolation of grid-based fields onto particles and updating of particle properties using the fields

- **3. Shift:** Move particles among processes in the distributed environment. Usually, deposit and move take 80 to 90% of the total computational time and are the focus for optimizations.

#### Data Layout and Alignment

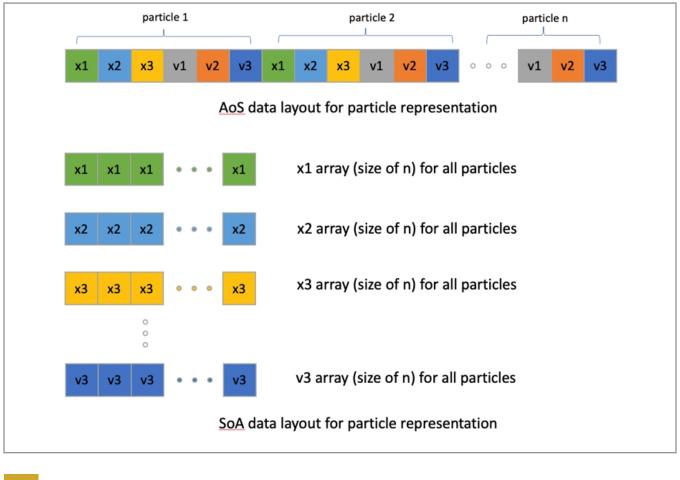

Particle properties can be stored as array-of-structures (AoS) or structure-of-arrays (SoA) data layout (**Figure 1**).

AoS helps to pack and unpack particles for shift, but doesn't help to enable vectorization for deposit and move with stride-one memory access. Since deposit and move are the hotspots of the code, we choose SoA data layout for particle representation. Specifically, we allocate the memory with alignment using the posix memalign () function (**Figure 2**).

1

2

Particle representation using AoS and SoA layout

```

posix_memalign((void **)&x1, CACHELINE_BYTES, max_prtl*sizeof(Real));

posix_memalign((void **)&x2, CACHELINE_BYTES, max_prtl*sizeof(Real));

posix_memalign((void **)&x3, CACHELINE_BYTES, max_prtl*sizeof(Real));

posix_memalign((void **)&v1, CACHELINE_BYTES, max_prtl*sizeof(Real));

posix_memalign((void **)&v2, CACHELINE_BYTES, max_prtl*sizeof(Real));

posix_memalign((void **)&v3, CACHELINE_BYTES, max_prtl*sizeof(Real));

```

#### Allocating the memory with alignment using the posix\_memalign() function

We start the optimization by checking the vectorization report of the original code for deposit.cpp and move.cpp (Figure 3).

```

67

for (long p=0; p<nparticle; p++)</pre>

68

{

69

Real x1tmp = x1p[p];

Real x2tmp = x2p[p];

70

71

Real x3tmp = x3p[p];

72

Real v1tmp = v1p[p];

73

Real v2tmp = v2p[p];

74

Real v3tmp = v3p[p];

75

Real a = (x1tmp - x1s) * dx1 + isg;

76

77

int ig = (int)(a);

78

int is = ig -1;

79

Real d = a - ig;

Real wei1[3];

80

81

weil[0] = 0.5 * (1.0 - d) * (1.0 - d);

82

wei1[1] = 0.75 - (d - 0.5) * (d - 0.5);

wei1[2] = 0.5 * d * d;

83

84

85

a = (x2tmp - x2s) * dx2 + isq;

ig = (int)(a);

86

87

int js = ig - 1;

88

d = a - ig;

89

Real wei2[3];

90

wei2[0] = 0.5 * (1.0 - d) * (1.0 - d);

91

wei2[1] = 0.75 - (d - 0.5) * (d - 0.5);

wei2[2] = 0.5 * d * d;

92

93

94

a = (x3tmp - x3s) * dx3 + ksg;

95

ig = (int)(a);

int ks = ig -1;

96

97

d = a - iq:

98

Real wei3[3]:

99

wei3[0] = 0.5 * (1.0 - d) * (1.0 - d);

100

wei3[1] = 0.75 - (d - 0.5) * (d - 0.5);

101

wei3[2] = 0.5 * d * d;

102

103

for (int k0=0; k0<=2; k0++){

104

for (int j0=0; j0<=2; j0++){

105

for (int i0=0; i0<=2; i0++){

106

107

Real w = wei3[k0] * wei2[j0] * wei1[i0];

108

//#pragma omp ordered simd

mcoup(IDN,ks+k0,js+j0,is+i0) += w;

109

110

//#pragma omp ordered simd

111

mcoup(IM1,ks+k0,js+j0,is+i0) += w * v1tmp;

112

//#pragma omp ordered simd

113

mcoup(IM2,ks+k0,js+j0,is+i0) += w * v2tmp;

114

//#pragma omp ordered simd

115

mcoup(IM3,ks+k0,js+j0,is+i0) += w * v3tmp;

116

}}}

117

}

```

```

for (long p=0; p<nparticle; p++)</pre>

76

77

{

Real x1tmp = x1p[p];

Real x2tmp = x2p[p];

78

79

80

Real x3tmp = x3p[p];

Real v1tmp = v1p[p];

82

Real v2tmp = v2p[p];

83

Real v3tmp = v3p[p];

85

Real x1n = x1tmp + v1tmp * halfdt;

Real x2n = x2tmp + v2tmp * halfdt;

Real x3n = x3tmp + v3tmp * halfdt;

87

88

89

Real a = (x1tmp - x1s) * dx1 + isg;

90

int ig = (int)(a);

int is = ig - 1;

Real d = a - ig;

91

92

93

Real wei1[3]:

wei1[0] = 0.5 * (1.0 - d) * (1.0 - d);

wei1[1] = 0.75 - (d - 0.5) * (d - 0.5);

95

wei1[2] = 0.5 * d * d;

97

98

a = (x2tmp - x2s) * dx2 + isq

99

ig = (int)(a);

100

int js = ig - 1;

101

d = a - ig;

Real wei2[3];

102

103

wei2[0] = 0.5 * (1.0 - d) * (1.0 - d);

104

wei2[1] = 0.75 - (d - 0.5) * (d - 0.5);

wei2[2] = 0.5 * d * d;

105

106

107

a = (x3tmp - x3s) * dx3 + ksg;

108

ig = (int)(a);

109

110

int ks = ig - 1;

d = a - ig;

keal wei3[3];

wei3[0] = 0.5 * (1.0 - d) * (1.0 - d);

wei3[1] = 0.75 - (d - 0.5) * (d - 0.5);

114

115

wei3[2] = 0.5 * d * d;

116

Real bfld1 = 0.0; Real bfld2 = 0.0; Real bfld3 = 0.0;

117

Real efld1 = 0.0; Real efld2 = 0.0; Real efld3 = 0.0;

118

Real totwei=0.0; Real eb=0.0;

119

120

for (int k0=0; k0<=2; k0++){

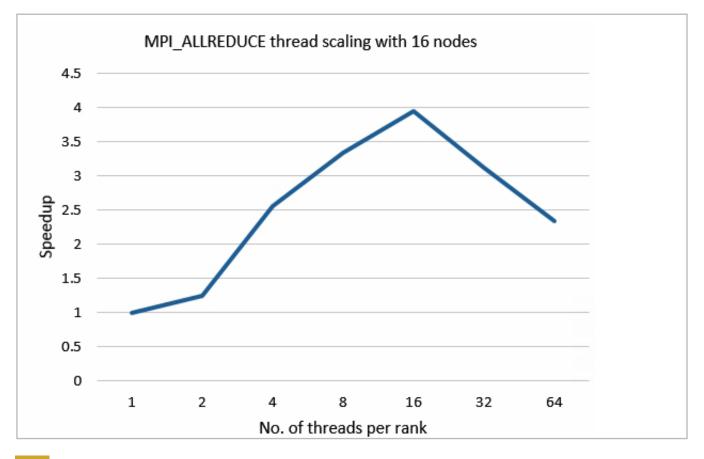

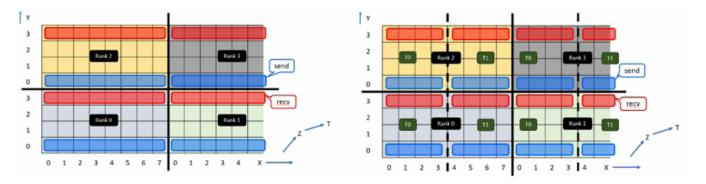

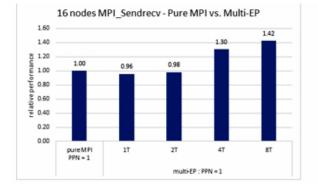

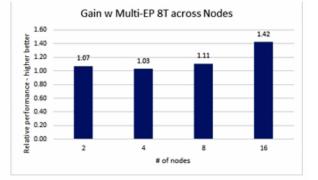

for (int j0=0; j0<=2; j0++){</pre>