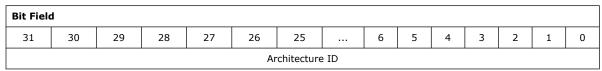

# **Nios® V Processor Reference Manual**

Updated for Quartus® Prime Design Suite: 24.3

# **Contents**

| 1. | . Overview                                        | 4  |

|----|---------------------------------------------------|----|

|    | 1.1. Quartus <sup>®</sup> Prime Software Support  | 5  |

| 2. | . Nios V/c Processor                              | 6  |

|    | 2.1. Processor Performance Benchmarks             |    |

|    | 2.2. Processor Pipeline                           |    |

|    | 2.3. Processor Architecture                       |    |

|    | 2.3.1. General-Purpose Register File              |    |

|    | 2.3.2. Arithmetic Logic Unit                      |    |

|    | 2.3.3. Reset and Debug Signals                    |    |

|    | 2.3.4. Memory and I/O Organization                |    |

|    | 2.3.5. Error Correction Code (ECC)                |    |

|    | 2.4. Programming Model                            |    |

|    | 2.4.1. Privilege Levels                           |    |

|    | 2.5. Core Implementation                          |    |

|    | 2.5.1. Instruction Set Reference                  |    |

| _  | Nios V/m Processor                                |    |

| 3. |                                                   |    |

|    | 3.1. Processor Performance Benchmarks             |    |

|    | 3.1.1. Pipelined                                  |    |

|    | 3.1.2. Non-pipelined                              |    |

|    | 3.2. Processor Pipeline                           |    |

|    | 3.2.1. Pipelined Architecture                     |    |

|    | 3.2.2. Non-pipelined Architecture                 |    |

|    | 3.3. Processor Architecture                       |    |

|    | 3.3.1. General-Purpose Register File              |    |

|    | 3.3.3. Reset and Debug Signals                    |    |

|    | 3.3.4. Control and Status Registers               |    |

|    | 3.3.5. Trap Controller                            |    |

|    | 3.3.6. Memory and I/O Organization                |    |

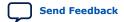

|    | 3.3.7. RISC-V based Debug Module                  |    |

|    | 3.3.8. Error Correction Code (ECC)                |    |

|    | 3.4. Programming Model                            |    |

|    | 3.4.1. Privilege Levels                           |    |

|    | 3.4.2. Control and Status Registers (CSR) Mapping |    |

|    | 3.5. Core Implementation                          |    |

|    | 3.5.1. Instruction Set Reference                  |    |

|    |                                                   |    |

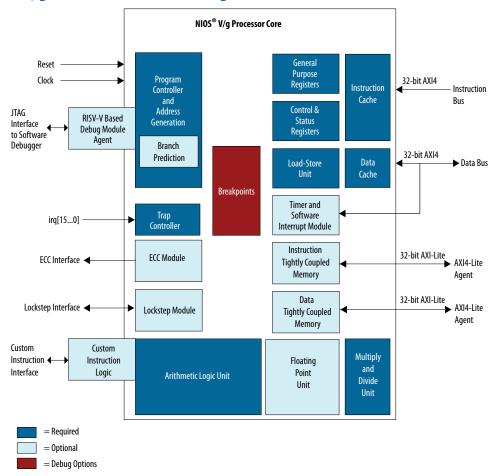

| 4. | Nios V/g Processor                                |    |

|    | 4.1. Processor Performance Benchmarks             |    |

|    | 4.2. Processor Pipeline                           |    |

|    | 4.3. Processor Architecture                       |    |

|    | 4.3.1. General-Purpose Register File              |    |

|    | 4.3.2. Arithmetic Logic Unit                      |    |

|    | 4.3.3. Multipy and Divide Units                   |    |

|    | 4.3.4. Floating-Point Unit                        |    |

|    | 4.5.5. CUSTOM INSTRUCTION                         | 50 |

#### Contents

| 6 Document Pavision History for the Nios V Processor Reference Manual | 83 |

|-----------------------------------------------------------------------|----|

| 5. Nios V Processor Reference Manual Archives                         | 82 |

| 4.5.1. Instruction Set Reference                                      | 80 |

| 4.5. Core Implementation                                              |    |

| 4.4.2. Control and Status Registers (CSR) Mapping                     |    |

| 4.4.1. Privilege Levels                                               | 73 |

| 4.4. Programming Model                                                | 73 |

| 4.3.13. Lockstep Module                                               | 73 |

| 4.3.12. Branch Prediction                                             |    |

| 4.3.11. Error Correction Code (ECC)                                   |    |

| 4.3.10. RISC-V based Debug Module                                     | 64 |

| 4.3.9. Memory and I/O Organization                                    |    |

| 4.3.8. Trap Controller                                                | 52 |

| 4.3.7. Control and Status Registers                                   | 52 |

| 4.3.6. Reset and Debug Signals                                        | 51 |

### 1. Overview

The Nios<sup>®</sup> V processor is a soft processor core with the following characteristics:

- Designed for Intel® FPGA devices and based on RISC-V\* specification

- Does not include peripherals or the connection logic to external devices

- Includes only the circuitry required to implement the Nios V processor architecture

The following table lists the available variants:

**Table 1.** Nios V Processor Variants

| Processor Core | Variant                   |

|----------------|---------------------------|

| Nios V/c       | Compact Microcontroller   |

| Nios V/m       | Microcontroller           |

| Nios V/g       | General-purpose processor |

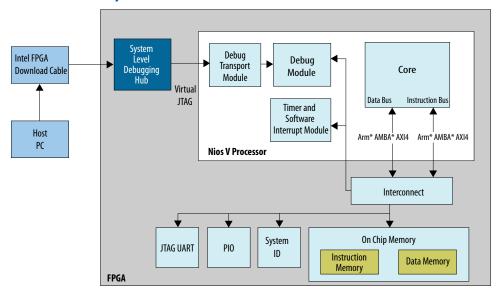

Figure 1. Nios V Processor System on Intel FPGA

#### **Related Information**

- RISC-V<sup>®</sup> Specifications

- Nios V/m Processor on page 17

More information about the Nios V/m processor (Microcontroller).

- Nios V/g Processor on page 43

More information about the Nios V/g processor (General-purpose processor).

<sup>&</sup>lt;sup>©</sup> Altera Corporation. Altera, the Altera logo, the 'a' logo, and other Altera marks are trademarks of Altera Corporation. Altera and Intel warrant performance of its FPGA and semiconductor products to current specifications in accordance with Altera's or Intel's standard warranty as applicable, but reserves the right to make changes to any products and services at any time without notice. Altera and Intel assume no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to inwriting by Altera or Intel. Altera and Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

<sup>9001:2015</sup> Registered

# 1.1. Quartus® Prime Software Support

Nios V processor build flow is different for Quartus<sup>®</sup> Prime Pro Edition software and Quartus Prime Standard Edition software. Refer to *AN 980: Nios V Processor Quartus Prime Software Support* for more information about the differences.

#### **Related Information**

AN 980: Nios V Processor Quartus Prime Software Support

## 2. Nios V/c Processor

The Nios V/c processor is a compact microcontroller core developed by Intel based on the RISC-V RV32I instruction set and supports the functional units described in this document.

#### 2.1. Processor Performance Benchmarks

Table 2. Nios V/c Processor Performance Benchmarks in Intel FPGA Devices for Quartus Prime Software

| Quartus Prime     | FPGA Used             | f <sub>MAX</sub> (MHz) | Logic Size | Architecture Performance |                       |

|-------------------|-----------------------|------------------------|------------|--------------------------|-----------------------|

| Edition           |                       |                        |            | DMIPS/MHz<br>Ratio       | CoreMark/MHz<br>Ratio |

| Quartus Prime Pro | Cyclone® 10           | 315                    | 402 ALM    | 0.227                    | 0.17                  |

| Edition           | Arria <sup>®</sup> 10 | 347                    | 405 ALM    |                          |                       |

|                   | Stratix® 10           | 361                    | 444 ALM    |                          |                       |

|                   | Agilex™ 7             | 443                    | 438 ALM    |                          |                       |

|                   | Agilex 5              | 389                    | 434 ALM    |                          |                       |

| Quartus Prime     | Cyclone IV E          | 118                    | 1022 LE    | 0.268                    | 0.201                 |

| Standard Edition  | Cyclone V             | 155                    | 423 ALM    |                          |                       |

|                   | Arria V               | 175                    | 414 ALM    |                          |                       |

|                   | Arria V GZ            | 289                    | 372 ALM    |                          |                       |

|                   | Stratix V             | 332                    | 372 ALM    |                          |                       |

|                   | Cyclone 10 LP         | 137                    | 1025 LE    |                          |                       |

|                   | Arria 10              | 325                    | 355 ALM    |                          |                       |

|                   | MAX® 10               | 137                    | 1022 LE    |                          |                       |

<sup>©</sup> Altera Corporation. Altera, the Altera logo, the 'a' logo, and other Altera marks are trademarks of Altera Corporation. Altera and Intel warrant performance of its FPGA and semiconductor products to current specifications in accordance with Altera's or Intel's standard warranty as applicable, but reserves the right to make changes to any products and services at any time without notice. Altera and Intel assume no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to inwriting by Altera or Intel. Altera and Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

<sup>9001:2015</sup> Registered

**Table 3.** Benchmark Parameters for Quartus Prime Software

| Parameter           |                        | Settings/D                                                                                                                                                                   | Description                                                                                                      |  |

|---------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|

|                     |                        | Quartus Prime Pro Edition                                                                                                                                                    | Quartus Prime Standard Edition                                                                                   |  |

|                     |                        | Maximum performance result are based on 10 seed sweep from Quartus Prime Pro Edition software version 24.3.                                                                  | Maximum performance result are based on 10 seed sweep from Quartus Prime Standard Edition software version 23.1. |  |

| Device speed g      | grade                  | Fastest speed grade from each Intel FPG                                                                                                                                      | A device family.                                                                                                 |  |

| Defined peripherals |                        | <ul> <li>Nios V/c processor core (without deb</li> <li>128 KB on-chip memory for the instributed)</li> <li>JTAG UART Intel FPGA IP.</li> <li>Interval Timer Core.</li> </ul> | ·                                                                                                                |  |

| Toolchain           | Version                | riscv32-unknown-elf-gcc (GCC) version 13.2.0     CMake Version: 3.29.3                                                                                                       | riscv32-unknown-elf-gcc (GCC) version 12.1.0     CMake Version: 3.27.1                                           |  |

|                     | Compiler configuration | Compiler flags: -03     Assembler options: -Wa -gdwarf2     Compile options: -Wall -Wformat-mabi=ilp32                                                                       | security -march=rv32i -                                                                                          |  |

Altera® uses the same Quartus Prime design example for maximum performance benchmark(fMAX) and logic size benchmarks. The compiler settings are:

- Superior Performance with Maximum Placement Effort in Quartus Prime Pro Edition software.

- **High Performance Effort** in Quartus Prime Standard Edition software.

Note:

Results may vary depending on the version of the Quartus Prime software, the version of the Nios V processor, compiler version, target device and the configuration of the processor. Additionally, any changes to the system logic design can change the performance and LE usage. All results are generated from design built with Platform Designer.

### 2.2. Processor Pipeline

The Nios V/c processor supports a non-pipelined datapath.

Table 4. Processor Non-pipelined Stages

| Stage | Denotation          | Function                                                                                                                             |

|-------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| F     | Instruction fetch   | Pre-decode for register file read                                                                                                    |

| D     | Instruction decode  | <ul> <li>Decode the instruction</li> <li>Register file read data available</li> <li>Hazard resolution and data forwarding</li> </ul> |

| E     | Instruction execute | <ul> <li>ALU operations</li> <li>Memory address calculation</li> <li>Branch resolution</li> <li>CSR read/write</li> </ul>            |

| М     | Memory              | Memory and multicycle operations     Register file write     Next PC logic     Branch redirection                                    |

The Nios V/c processor implements the general-purpose register file using the M20K memory blocks. The processor takes one clock cycle to read from an M20K location. Therefore, the F-stage initiates register file reads so general-purpose register values are available in D-stage.

One instruction is available in the processor datapath at any time. Instructions flow from F-stage to M-stages without any stalls. Instruction and associated control logic are registered during D-stage, E-stage, and M-stage.

The processor requests the next instruction during the M-stage.

- For single cycle instructions, the processor makes the request as soon as the single cycle instruction enters M-stage.

- For multicycle instructions, the processor makes the request as soon as the multicycle instruction completes.

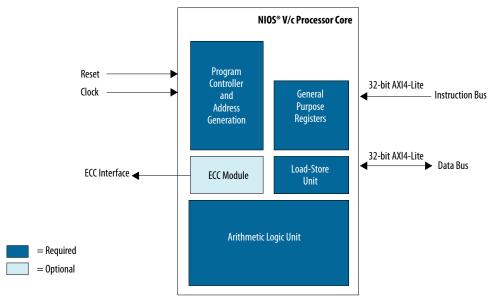

#### 2.3. Processor Architecture

The Nios V/c processor architecture describes an instruction-set architecture (ISA). The ISA in turn necessitates a set of functional units that implement the instructions.

The Nios V processor architecture defines the following functional units:

- General-purpose register file

- Arithmetic logic unit (ALU)

- Instruction bus

- Data bus

- ECC module

Figure 2. Nios V/c Processor Core Block Diagram

### 2.3.1. General-Purpose Register File

Nios V/c processor implementation supports a flat register file. The register file contains thirty-two 32-bit general-purpose integer registers. Nios V/c processor implements the general-purpose register using M20K memories, which do not support two read ports. Hence, Nios V/c processor duplicates the register files so that two different source registers for an instruction are available in a single cycle. After performing ALU operations, the processor core writes the same result to the destination register in both memories.

### 2.3.2. Arithmetic Logic Unit

The arithmetic logic unit (ALU) operates on data stored in general-purpose registers. ALU operations take one or two inputs from registers and store the result back into the register.

Table 5. Fundamental Data Operations of the ALU

| Category                                                             | Description                                                                                  |

|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Arithmetic Addition and subtraction on signed and unsigned operands. |                                                                                              |

| Relational                                                           | Equal, not-equal, greater-than-or-equal, and less-than relational operations (==, != >=, <). |

| Logical                                                              | AND, OR, NOR, and XOR logical operations.                                                    |

| Shift                                                                | Logical and arithmetic shift operations.                                                     |

For load and store instructions, the Nios V/c processor uses the ALU to calculate the memory address. For conditional control transfer instructions, Nios V/c processor uses the relational operations in the ALU to determine if the processor takes or leaves the branch.

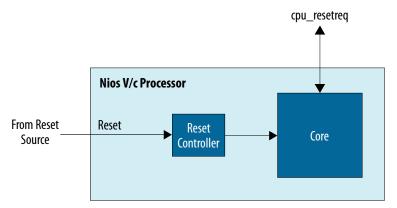

### 2.3.3. Reset and Debug Signals

| Interface    | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                       |

|--------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reset        | Reset   | A global hardware reset input signal that forces the Nios V processor to reset immediately.                                                                                                                                                                                                                                                                                       |

| cpu_resetreq | Conduit | An optional local reset ports which appear after you enable Add Reset Request Interface parameter. The signal consists of an input resetreq signal and an output ack signal that trigger the Nios V processor to reset without affecting other components in a Nios V processor system.  • You can request a reset to the Nios V processor core by asserting the resetreq signal. |

|              |         | The resetreq signal must remain asserted until the processor asserts ack signal. Failure for the signal to remain asserted can cause the processor to be in a non-deterministic state.                                                                                                                                                                                            |

|              |         | Assertion of the resetreq signal in debug mode has no effect on the processor's state.                                                                                                                                                                                                                                                                                            |

|              |         | The Nios V processor responds that the reset is successful by asserting the ack signal.                                                                                                                                                                                                                                                                                           |

|              |         | After the processor is successfully reset, the assertion of the ack signal can happen multiple times periodically until the de-assertion of the resetreg signal.                                                                                                                                                                                                                  |

Figure 3. Nios V/c Processor Reset Network

### 2.3.4. Memory and I/O Organization

You can configure the Nios V/c processor systems. Consequently, the memory and I/O organization varies from system to system. A Nios V/c processor core uses one or more of the following ports to provide access to memory and I/O:

- Instruction manager port: An Arm\* Advanced Microcontroller Bus Architecture (AMBA\*) AXI4-Lite Memory-Mapped manager port that connects to instruction memory via system interconnect fabric.

- Data manager port: An AMBA AXI4-Lite Memory-Mapped manager port that connects to data memory and peripherals via the system interconnect fabric.

Nios V/c Processor Core Memory Mapped I/O Access: Both data memory and peripherals are mapped into the address space of the data manager port. Nios V/c processor core uses little-endian byte ordering. Words and half-words are stored in

memory with the more-significant bytes at higher addresses. The Nios V/c processor core does not specify anything about the existence of memory and peripherals. The quantity, type, and connection of memory and peripherals are system dependent.

#### 2.3.4.1. Instruction and Data Buses

#### 2.3.4.1.1. Instruction Manager Port

Nios V/c processor instruction bus is implemented as a 32-bit AMBA 4 AXI-Lite manager port.

The instruction manager port:

- Performs a single function: it fetches instructions to be executed by the processor.

- Does not perform any write operations.

- Can issue successive read requests before data return from prior requests.

- Can prefetch sequential instructions.

- Always retrieves 32-bits of data. Every instruction fetch returns a full instruction word, regardless of the width of the target memory. The widths of memory in the Nios V/c processor system is not applicable to the programs. Instruction address is always aligned to a 32-bit word boundary.

- Does not require any burst adapter because it is non-bursting.

#### **Table 6. Instruction Interface Signals**

| Interface              | Signal  | Role                                     | Width  | Direction |

|------------------------|---------|------------------------------------------|--------|-----------|

| Write Address Channel  | awaddr  | Unused                                   | [31:0] | Output    |

|                        | awprot  | Unused                                   | [2:0]  | Output    |

|                        | awvalid | Unused                                   | 1      | Output    |

|                        | awready | Unused                                   | 1      | Input     |

| Write Data Channel     | wdata   | Unused                                   | [31:0] | Output    |

|                        | wstrb   | Unused                                   | [3:0]  | Output    |

|                        | wvalid  | Unused                                   | 1      | Output    |

|                        | wready  | Unused                                   | 1      | Input     |

| Write Response Channel | bresp   | Unused                                   | [1:0]  | Input     |

|                        | bvalid  | Unused                                   | 1      | Input     |

|                        | bready  | Unused                                   | 1      | Output    |

| Read Address Channel   | araddr  | Instruction Address<br>(Program Counter) | [31:0] | Output    |

|                        | arprot  | Unused                                   | [2:0]  | Output    |

|                        | arvalid | Instruction address valid                | 1      | Output    |

|                        | arready | Instruction address ready (from memory)  | 1      | Input     |

| Read Data Channel      | rdata   | Instruction                              | [31:0] | Input     |

|                        |         |                                          | con    | tinued    |

| Interface          | Signal | Role Wie                                                                        |       | Direction |

|--------------------|--------|---------------------------------------------------------------------------------|-------|-----------|

|                    |        | Instruction response: Non-zero value denotes instruction access fault exception | [1:0] | Input     |

| rvalid Instruction |        | Instruction valid                                                               | 1     | Input     |

|                    | rready | Constant 1                                                                      | 1     | Output    |

#### 2.3.4.1.2. Data Manager Port

The Nios V/c processor data bus is implemented as a 32-bit AMBA 4 AXI-Lite manager port. The data manager port:

- Performs read data from memory or a peripheral when the processor executes a load instruction.

- Performs write data to memory or a peripheral when the processor executes a store instruction.

- Does not require any burst adapter because it is non-bursting.

<code>axsize</code> signal value indicates the load/store instruction size- byte (LB/SB), halfword (LH/SH) or word (LW/SW). Address on <code>axaddr</code> signal is always aligned to size of the transfer. For store instructions, respective write strobe bits are asserted to indicate bytes being written.

Nios V/c processor core does not support speculative issue of load/store instruction. Hence, a core can issue only one load or store instruction and waits until the issued instruction is complete.

**Table 7. Data Interface Signals**

| Interface              | Signal                                                                                        | Role                              | Width  | Direction |

|------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------|--------|-----------|

| Write Address Channel  | awaddr                                                                                        | Store address                     | [31:0] | Output    |

|                        | awprot                                                                                        | Unused                            | [2:0]  | Output    |

|                        | awvalid                                                                                       | Store address valid               | 1      | Output    |

|                        | awready                                                                                       | Store address ready (from memory) | 1      | Input     |

| Write Data Channel     | wdata                                                                                         | Store data                        | [31:0] | Output    |

|                        | wstrb                                                                                         | Byte position in word             | [3:0]  | Output    |

|                        | wvalid Store data valid 1                                                                     |                                   | 1      | Output    |

|                        | wready                                                                                        | Store data ready (from memory)    | 1      | Input     |

| Write Response Channel | e Response Channel bresp Store response: Non-zero value denotes store access fault exception. |                                   | [1:0]  | Input     |

|                        | bvalid                                                                                        | Store response valid              | 1      | Input     |

|                        | bready                                                                                        | Constant 1                        | 1      | Output    |

| Read Address Channel   | Read Address Channel araddr Load address                                                      |                                   | [31:0] | Output    |

|                        | arprot                                                                                        | t Unused                          |        | Output    |

|                        | arvalid                                                                                       | Load address valid                | 1      | Output    |

|                        |                                                                                               |                                   | со     | ntinued   |

| Interface         | Signal                                                                  | Role       | Width  | Direction |

|-------------------|-------------------------------------------------------------------------|------------|--------|-----------|

|                   | arready Load address ready (from subordinates)                          |            | 1      | Input     |

| Read Data Channel | Data Channel rdata Load data [:                                         |            | [31:0] | Input     |

|                   | rresp Load response: Non-zero value denotes load access fault exception |            | [1:0]  | Input     |

|                   | rvalid Load data valid 1                                                |            | 1      | Input     |

|                   | rready                                                                  | Constant 1 | 1      | Output    |

#### 2.3.4.1.3. Choosing a Suitable Interface

The Nios V/c processor core offers an Avalon<sup>®</sup> memory-mapped and Advanced eXtensible Interface (AXI) interface for both the instruction manager port and the data manager port. You can choose one of the interfaces in Platform Designer based on your design.

For example, if most IPs in Platform Designer use Avalon memory-mapped interface, you can choose the Avalon memory-mapped interface in the Nios V/c processor core as the bridge interface. Similarly, if most IPs in Platform Designer use AXI Interface, you can choose the AXI Interface in the Nios V/c processor core as the bridge interface.

The benefits of using the appropriate interface are as follows:

- Reduces the amount of bridging logic

- · Reduces overhead bandwidth

- Provides better performance

#### 2.3.4.2. Address Map

The address map for memories and peripherals in a Nios V/c processor system is design dependent. The Reset Address is part of the processor. You can specify the Reset Address in Platform Designer during system configuration.

### 2.3.5. Error Correction Code (ECC)

The Nios V/c processor core has the option to enable error detection and ECC status reporting for the RAM block, that is the Register file. Each RAM block has its own source ID. When an ECC event occurs, the processor transmits the source ID and ECC status to the ECC interface.

- If the ECC event is a correctable error, the processor continues to operate after correcting the error. The correction made is not written back to its memory source.

- If the ECC event is an un-correctable error, the processor halts its current progress and stalls. You need to reset either the processor core alone or the entire system.

Note: To reset only the processor core, apply the **Reset Request Interface** to safely reset the Nios V processor (cleared of any outstanding operations). To reset the entire system, you can use the hard reset interface instead.

The ECC interface allows external logic to monitor ECC errors from the Nios V/c processor. The interface is a conduit, made up of the following output signals.

- cpu\_ecc\_status: Indicates the error status

- cpu\_ecc\_source : Indicates the error source.

#### Table 8. cpu ecc status

| 2-bits Encoding | Description                      | Effects on Software                   |

|-----------------|----------------------------------|---------------------------------------|

| 2′b00           | No ECC event                     | None                                  |

| 2'b01           | Reserved                         | Not Applicable                        |

| 2'b10           | Correctable single bit ECC error | None                                  |

| 2′b11           | Un-correctable ECC error         | Likely fatal and halts the processor. |

### Table 9. cpu\_ecc\_source

| 4-bits Encoding   | ECC Source                     | Available      |

|-------------------|--------------------------------|----------------|

| 4′b0000           | No ECC event                   | Always         |

| 4′b0001           | General Purpose Register (GPR) | Always         |

| 4'b0010 ~ 4'b1110 | Other RAM Blocks               | Not Available  |

| 4′b1111           | Reserved                       | Not Applicable |

Note:

Due to a limitation with embedded memory blocks, the simulation model of Nios V processor does not support ECC on Arria 10 devices.

#### **Related Information**

Embedded Memory (RAM: 1-PORT, RAM: 2-PORT, ROM: 1-PORT, and ROM: 2-PORT) User Guide

For more information about ECC on Arria 10 devices.

### 2.4. Programming Model

### 2.4.1. Privilege Levels

The privilege levels in Nios V/c processor are designed based on the RISC-V architecture specification. The Nios V/c processor only supports Machine Mode (Mmode), which provides low-level access to the machine implementation.

#### **Related Information**

RISC-V® Specifications

### 2.5. Core Implementation

#### 2.5.1. Instruction Set Reference

The Nios V/c processor is based on the RISC-V RV32I specification. RV32I is a base integer instruction set. RV321 supports 6 types of instruction format. They are R-type, I-type, S-type, B-type, U-type, and J-type.

### **Table 10.** Instruction Formats (R-type)

| Bit Fiel | ld (R-ty      | rpe) |    |    |    |    |     |    |    |    |    |        |    |    |    |  |

|----------|---------------|------|----|----|----|----|-----|----|----|----|----|--------|----|----|----|--|

| 31       | 30            | 29   | 28 | 27 | 26 | 25 | 24  | 23 | 22 | 21 | 20 | 19     | 18 | 17 | 16 |  |

|          | funct7        |      |    |    |    |    | rs2 |    |    |    |    | rs1    |    |    |    |  |

| 15       | 14            | 13   | 12 | 11 | 10 | 9  | 8   | 7  | 6  | 5  | 4  | 3      | 2  | 1  | 0  |  |

| rs1      | rs1 funct3 rd |      |    |    |    |    |     |    |    |    |    | opcode | •  |    |    |  |

### **Table 11.** Instruction Formats (I-type)

| Bit Fiel           | Bit Field (I-type) |    |    |    |    |    |    |    |        |    |     |    |    |    |    |

|--------------------|--------------------|----|----|----|----|----|----|----|--------|----|-----|----|----|----|----|

| 31                 | 30                 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22     | 21 | 20  | 19 | 18 | 17 | 16 |

|                    | imm[11:0]          |    |    |    |    |    |    |    |        |    | rs1 |    |    |    |    |

| 15                 | 14                 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6      | 5  | 4   | 3  | 2  | 1  | 0  |

| rs1 funct3 rd opco |                    |    |    |    |    |    |    |    | opcode |    |     |    |    |    |    |

### **Table 12.** Instruction Formats (S-type)

| Bit Fiel | Bit Field (S-type) |    |    |    |    |    |     |    |    |    |    |        |    |    |    |  |

|----------|--------------------|----|----|----|----|----|-----|----|----|----|----|--------|----|----|----|--|

| 31       | 30                 | 29 | 28 | 27 | 26 | 25 | 24  | 23 | 22 | 21 | 20 | 19     | 18 | 17 | 16 |  |

|          | imm[11:5]          |    |    |    |    |    | rs2 |    |    |    |    | rs1    |    |    |    |  |

| 15       | 14                 | 13 | 12 | 11 | 10 | 9  | 8   | 7  | 6  | 5  | 4  | 3      | 2  | 1  | 0  |  |

| rs1      | rs1 funct3 imm[4   |    |    |    |    |    | ]   |    |    |    |    | opcode |    |    |    |  |

### **Table 13.** Instruction Formats (B-type)

| Bit Field (B-t | Bit Field (B-type) |    |      |       |    |    |    |         |    |     |    |        |    |    |    |

|----------------|--------------------|----|------|-------|----|----|----|---------|----|-----|----|--------|----|----|----|

| 31             | 30                 | 29 | 28   | 27    | 26 | 25 | 24 | 23      | 22 | 21  | 20 | 19     | 18 | 17 | 16 |

| imm[12]        |                    |    | imm[ | 10:5] |    |    |    | rs2     |    | rs1 |    |        |    |    |    |

| 15             | 14                 | 13 | 12   | 11    | 10 | 9  | 8  | 7       | 6  | 5   | 4  | 3      | 2  | 1  | 0  |

| rs1            | funct3 imm[4:1     |    |      |       |    |    |    | imm[11] |    |     |    | opcode |    |    |    |

### **Table 14.** Instruction Formats (U-type)

| Bit Fie | Bit Field (U-type)   |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

|---------|----------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| 31      | 30                   | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|         | imm[31:16]           |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

| 15      | 14                   | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|         | imm[15:12] rd opcode |    |    |    |    |    |    |    |    |    |    |    |    |    |    |

### **Table 15.** Instruction Formats (J-type)

| Bit Field (J-ty | Bit Field (J-type)   |    |    |    |      |       |    |    |    |    |         |    |       |       |    |

|-----------------|----------------------|----|----|----|------|-------|----|----|----|----|---------|----|-------|-------|----|

| 31              | 30                   | 29 | 28 | 27 | 26   | 25    | 24 | 23 | 22 | 21 | 20      | 19 | 18    | 17    | 16 |

| imm[20]         |                      |    |    |    | imm[ | 10:1] |    |    |    |    | imm[11] |    | imm[1 | 9:16] |    |

| 15              | 14                   | 13 | 12 | 11 | 10   | 9     | 8  | 7  | 6  | 5  | 4       | 3  | 2     | 1     | 0  |

| imn             | imm[15:12] rd opcode |    |    |    |      |       |    |    |    |    |         |    |       |       |    |

### **Related Information**

RISC-V<sup>®</sup> Specifications

More information about the instruction set of the RV32I Base Integer.

### 3. Nios V/m Processor

The Nios V/m processor is a microcontroller core developed by Intel based on the RISC-V instruction set and supports the functional units described in this document.

The Nios V/m processor supports two distinct configurations:

- Pipelined

- Implements RV32IZicsr instruction set.

- Supports five-stages pipelined datapath.

- · Non-pipelined

- Implements RV32IZicsr instruction set.

- Supports non-pipelined datapath.

#### **Related Information**

Overview on page 4

#### 3.1. Processor Performance Benchmarks

### 3.1.1. Pipelined

Table 16. Nios V/m Processor Performance Benchmarks in Intel FPGA Devices for Quartus Prime Software

| Quartus Prime Edition          | FPGA Used    | fMAX (MHz)                                     | Logic Size | Architectur     | e Performance      |

|--------------------------------|--------------|------------------------------------------------|------------|-----------------|--------------------|

|                                |              |                                                |            | DMIPS/MHz Ratio | CoreMark/MHz Ratio |

| Quartus Prime Pro Edition      | Cyclone 10   | 276                                            | 1064 ALM   | 0.63            | 0.49               |

|                                | Arria 10     | 281                                            | 1038 ALM   |                 |                    |

|                                | Stratix 10   | 324                                            | 1341 ALM   |                 |                    |

|                                | Agilex 7     | 410                                            | 1252 ALM   |                 |                    |

|                                | Agilex 5     | 311                                            | 1288 ALM   |                 |                    |

| Quartus Prime Standard Edition | Cyclone IV E | 107                                            | 2831 LE    | 0.650           | 0.441              |

|                                | Cyclone V    | 145                                            | 1253 ALM   |                 |                    |

|                                | Arria V      | 146                                            | 1222 ALM   |                 |                    |

|                                | Arria V GZ   | 264                                            | 1215 ALM   |                 |                    |

|                                | Stratix V    | 304                                            | 1199 ALM   |                 |                    |

|                                |              | <u>.                                      </u> | •          | •               | continued          |

<sup>©</sup> Altera Corporation. Altera, the Altera logo, the 'a' logo, and other Altera marks are trademarks of Altera Corporation. Altera and Intel warrant performance of its FPGA and semiconductor products to current specifications in accordance with Altera's or Intel's standard warranty as applicable, but reserves the right to make changes to any products and services at any time without notice. Altera and Intel assume no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to inwriting by Altera or Intel. Altera and Intel customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

<sup>9001:2015</sup> Registered

| Quartus Prime Edition | FPGA Used     | fMAX (MHz) | Logic Size | Architecture    | e Performance      |

|-----------------------|---------------|------------|------------|-----------------|--------------------|

|                       |               |            |            | DMIPS/MHz Ratio | CoreMark/MHz Ratio |

|                       | Cyclone 10 LP | 135        | 2848 LE    |                 |                    |

|                       | Arria 10      | 290        | 1132 ALM   |                 |                    |

|                       | MAX 10        | 123        | 2864 LE    |                 |                    |

#### **Table 17.** Benchmark Parameters for Quartus Prime Software

| Pa               | rameter                | Settings/D                                                                                                             | Description                                                                                                      |

|------------------|------------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

|                  |                        | Quartus Prime Pro Edition                                                                                              | Quartus Prime Standard Edition                                                                                   |

| Quartus Prime se | eed                    | Maximum performance result are based on 10 seed sweep from Quartus Prime Pro Edition software version 24.3.            | Maximum performance result are based on 10 seed sweep from Quartus Prime Standard Edition software version 23.1. |

| Device speed gra | ade                    | Fastest speed grade from each Intel FPG                                                                                | A device family.                                                                                                 |

| Defined peripher | als                    | Nios V/m processor core (without<br>debug module and internal timer).                                                  | Nios V/m processor core (without debug module).                                                                  |

|                  |                        | <ul><li>128 KB on-chip memory for the instrict</li><li>JTAG UART Intel FPGA IP.</li><li>Interval Timer Core.</li></ul> | uction and data bus.                                                                                             |

| Toolchain        | Version                | riscv32-unknown-elf-gcc (GCC) version 13.2.0     CMake Version: 3.29.3                                                 | riscv32-unknown-elf-gcc (GCC) version 12.1.0     CMake Version: 3.27.1                                           |

|                  | Compiler configuration | Compiler flags: -03     Assembler options: -Wa -gdwarf2     Compile options: -Wall -Wformat-mabi=ilp32                 | security -march=rv32i -                                                                                          |

Intel uses the same Quartus Prime design example for maximum performance benchmark(fMAX) and logic size benchmarks. The compiler settings are:

- Superior Performance with Maximum Placement Effort in Quartus Prime Pro Edition software.

- **High Performance Effort** in Quartus Prime Standard Edition software.

Note:

Results may vary depending on the version of the Quartus Prime software, the version of the Nios V processor, compiler version, target device and the configuration of the processor. Additionally, any changes to the system logic design might change the performance and LE usage. All results are generated from design built with Platform Designer.

### 3.1.2. Non-pipelined

Table 18. Nios V/m Processor Performance Benchmarks in Intel FPGA Devices for Quartus Prime Software

| Quartus Prime     | FPGA Used     | f <sub>MAX</sub> (MHz) | Logic Size | Architecture       | Performance           |

|-------------------|---------------|------------------------|------------|--------------------|-----------------------|

| Edition           |               |                        |            | DMIPS/MHz<br>Ratio | CoreMark/MHz<br>Ratio |

| Quartus Prime Pro | Cyclone 10    | 311                    | 724 ALM    | 0.227              | 0.170                 |

| Edition           | Arria 10      | 337                    | 742 ALM    |                    |                       |

|                   | Stratix 10    | 354                    | 794 ALM    |                    |                       |

|                   | Agilex 7      | 436                    | 826 ALM    |                    |                       |

|                   | Agilex 5      | 336                    | 769 ALM    |                    |                       |

| Quartus Prime     | Cyclone IV E  | 117                    | 1598 LE    | 0.268              | 0.201                 |

| Standard Edition  | Cyclone V     | 144                    | 705 ALM    |                    |                       |

|                   | Arria V       | 159                    | 708 ALM    |                    |                       |

|                   | Arria V GZ    | 281                    | 658 ALM    |                    |                       |

|                   | Stratix V     | 330                    | 641 ALM    |                    |                       |

|                   | Cyclone 10 LP | 135                    | 1604 LE    |                    |                       |

|                   | Arria 10      | 316                    | 559 ALM    |                    |                       |

|                   | MAX 10        | 127                    | 1619 LE    |                    |                       |

**Table 19.** Benchmark Parameters for Quartus Prime Software

| Parameter           |                        | Settings/Description                                                                                                                                                                                                   |                                                                                                                  |  |  |

|---------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|

|                     |                        | Quartus Prime Pro Edition                                                                                                                                                                                              | Quartus Prime Standard Edition                                                                                   |  |  |

| Quartus Prime seed  |                        | Maximum performance result are based on 10 seed sweep from Quartus Prime Pro Edition software version 24.3.                                                                                                            | Maximum performance result are based on 10 seed sweep from Quartus Prime Standard Edition software version 23.1. |  |  |

| Device speed        | grade                  | Fastest speed grade from each Intel FPG                                                                                                                                                                                | Fastest speed grade from each Intel FPGA device family.                                                          |  |  |

| Defined peripherals |                        | <ul> <li>Nios V/m processor core (without debug module and internal timer).</li> <li>128 KB on-chip memory for the instruction and data bus.</li> <li>JTAG UART Intel FPGA IP.</li> <li>Interval Timer Core</li> </ul> |                                                                                                                  |  |  |

| Toolchain Version   |                        | <ul><li>riscv32-unknown-elf-gcc (GCC) version 13.2.0</li><li>CMake Version: 3.29.3</li></ul>                                                                                                                           | <ul><li>riscv32-unknown-elf-gcc (GCC)<br/>version 12.1.0</li><li>CMake Version: 3.27.1</li></ul>                 |  |  |

|                     | Compiler configuration | Compiler flags: -03     Assembler options: -Wa -gdwarf2     Compile options: -Wall -Wformatmabi=ilp32                                                                                                                  | -security -march=rv32i -                                                                                         |  |  |

Intel uses the same Quartus Prime design example for maximum performance benchmark(fMAX) and logic size benchmarks. However, the compiler settings are different for each benchmarks:

- Superior Performance with Maximum Placement Effort in Quartus Prime Pro Edition software.

- High Performance Effort in Quartus Prime Standard Edition software.

Note:

Results may vary depending on the version of the Quartus Prime software, the version of the Nios V processor, compiler version, target device and the configuration of the processor. Additionally, any changes to the system logic design might change the performance and LE usage. All results are generated from design built with Platform Designer.

### 3.2. Processor Pipeline

### 3.2.1. Pipelined Architecture

The Nios V/m processor employs a five-stage datapath.

**Table 20.** Processor Pipeline Stages

| Stage | Denotation          | Function                                                                                                        |

|-------|---------------------|-----------------------------------------------------------------------------------------------------------------|

| F     | Instruction fetch   | <ul> <li>PC+4 calculation</li> <li>Next instruction fetch</li> <li>Pre-decode for register file read</li> </ul> |

| D     | Instruction decode  | Decode the instruction     Register file read data available     Hazard resolution and data forwarding          |

| E     | Instruction execute | ALU operations     Memory address calculation     Branch resolution     CSR read/write                          |

| М     | Memory              | Memory and multicycle operations     Register file write     Branch redirection                                 |

| W     | Write back          | Facilitates data dependency resolution by providing general-<br>purpose register value.                         |

The Nios V/m processor implements the general-purpose register file using the M20K memory blocks. The processor takes one cycle to read from an M20K location. Therefore, the F-stage initiates register file reads so general-purpose register values are available in D-stage.

Writing to the M20K location takes two cycles. Therefore, the M-stage initiates writes to a general-purpose register. If there is a dependency to resolve, the M-stage carries forward the value to the W-stage.

The core resolves data dependencies in the D-stage. Operands can move from register file read or E-stage, M-stage, or W-stage.

Reasons for the pipeline stalling:

- Data dependency—if the source operand is not available in the D-stage, instruction in the D-stage and F-stage stalls until the operand becomes available. This happens when the destination general-purpose register of a load or multicycle instruction in the E-stage or M-stage is the source for the instruction in the Dstage.

- Resource stall—if a memory operation or multicycle is pending in the M-stage, the instructions in the preceding stages stall until M-stage completes the instruction.

### 3.2.2. Non-pipelined Architecture

The Nios V/m processor supports a non-pipelined datapath.

**Table 21. Processor Non-pipelined Stages**

| Stage | Denotation          | Function                                                                                               |

|-------|---------------------|--------------------------------------------------------------------------------------------------------|

| F     | Instruction fetch   | Pre-decode for register file read                                                                      |

| D     | Instruction decode  | Decode the instruction     Register file read data available     Hazard resolution and data forwarding |

| Е     | Instruction execute | ALU operations     Memory address calculation     Branch resolution     CSR read/write                 |

| М     | Memory              | Memory and multicycle operations     Register file write     Next PC logic     Branch redirection      |

The Nios V/m processor implements the general-purpose register file using the M20K memory blocks. The processor takes one clock cycle to read from an M20K location. Therefore, the F-stage initiates register file reads so general-purpose register values are available in D-stage.

One instruction is available in the processor datapath at any time. Instructions flow from F-stage to M-stages without any stalls. Instruction and associated control logic are registered during D-stage, E-stage, and M-stage.

The processor requests the next instruction during the M-stage.

- For single cycle instructions, the processor makes the request as soon as the single cycle instruction enters M-stage.

- For multicycle instructions, the processor makes the request as soon as the multicycle instruction completes.

#### 3.3. Processor Architecture

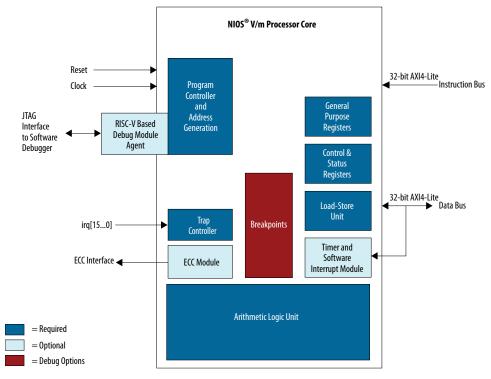

The Nios V/m processor architecture describes an instruction-set architecture (ISA). The ISA in turn necessitates a set of functional units that implement the instructions.

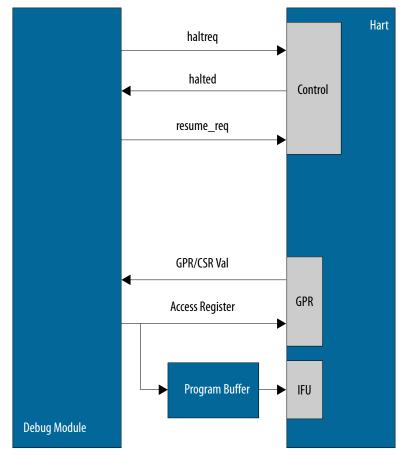

The Nios V/m processor architecture defines the following functional units:

- · General-purpose register file

- Arithmetic logic unit (ALU)

- Control and status registers (CSR)

- Trap controller

- Instruction bus

- Data bus

- RISC-V based debug module

- · ECC module

Figure 4. Nios V/m Processor Core Block Diagram

### 3.3.1. General-Purpose Register File

Nios V/m processor implementation supports a flat register file. The register file contains thirty-two 32-bit general-purpose integer registers. Nios V/m processor implements the general-purpose register using M20K memories, which do not support two read ports. Hence, Nios V/m processor duplicates the register files so that two different source registers for an instruction are available in a single cycle. After performing ALU operations, the processor core writes the same result to the destination register in both memories.

### 3.3.2. Arithmetic Logic Unit

The arithmetic logic unit (ALU) operates on data stored in general-purpose registers. ALU operations take one or two inputs from registers and store the result back into the register.

Table 22. Fundamental Data Operations of the ALU

| Category   | Description                                                                                  |

|------------|----------------------------------------------------------------------------------------------|

| Arithmetic | Addition and subtraction on signed and unsigned operands.                                    |

| Relational | Equal, not-equal, greater-than-or-equal, and less-than relational operations (==, != >=, <). |

| Logical    | AND, OR, NOR, and XOR logical operations.                                                    |

| Shift      | Logical and arithmetic shift operations.                                                     |

For load and store instructions, the Nios V/m processor uses the ALU to calculate the memory address. For conditional control transfer instructions, Nios V/m processor uses the relational operations in the ALU to determine if the processor takes or leaves the branch.

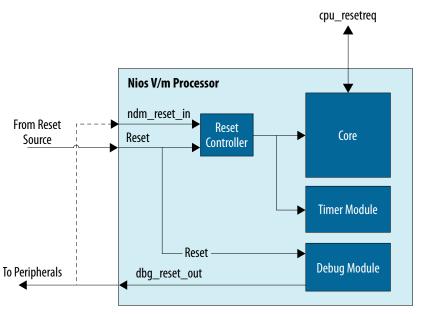

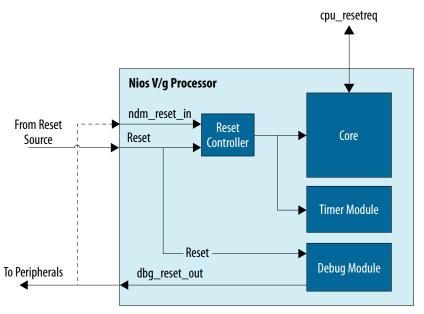

### 3.3.3. Reset and Debug Signals

Table 23. Reset and Debug Signals

| Interface     | Туре    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reset         | Reset   | A global hardware reset input signal that forces the Nios V processor to reset immediately.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| dbg_reset_out | Reset   | An optional reset output signal which appear after you enable both  Enable Debug and Enable Reset from Debug Module parameters.  This reset output signal is triggered by the JTAG debugger or niosvdownload -r command.  You can connect this reset output signal to the following input signals:  To the ndm_reset_in input to reset the core and the timer module.  To the reset input signal of other components as needed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| ndm_reset_in  | Reset   | An optional reset input signal which appear after you enable both  Enable Debug and Enable Reset from Debug Module parameters.  You can use this signal to trigger reset controller to reset the core and the timer module.  The reset controller synchronizes the reset (hard reset) and ndm_reset_in signals.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| cpu_resetreq  | Conduit | An optional local reset ports which appear after you enable Add Reset Request Interface parameter. The signal consists of an input resetreq signal and an output ack signal that trigger the Nios V processor to reset without affecting other components in a Nios V processor system.  • You can request a reset to the Nios V processor core by asserting the resetreq signal.  • The resetreq signal must remain asserted until the processor asserts ack signal. Failure for the signal to remain asserted can cause the processor to be in a non-deterministic state.  • Assertion of the resetreq signal in debug mode has no effect on the processor's state.  • The Nios V processor responds that the reset is successful by asserting the ack signal.  • After the processor is successfully reset, the assertion of the ack signal can happen multiple times periodically until the de-assertion of the resetreq signal. |

Figure 5. Nios V/m Processor Reset Network

### 3.3.4. Control and Status Registers

Nios V/m processor's Control and Status Registers (CSR) is both readable and writable. Nios V/m updates the CSR during the E-stage of the pipeline.

During the execution of a Nios V processor application, you may observe the following behaviors:

- CSR write instruction (in E-stage) is stalled due to the pending memory or multicycle instructions (in M-stage).

- CSR write instruction (in E-stage) continues after the pending instructions (in Mstage) are complete.

- If the processor generates an exception during the M-stage, the processor flushes the pending instructions in the pipeline (including the CSR write instruction in the E-stage) and initiates the trap handler to service the exception.

### 3.3.5. Trap Controller

In the Nios V processor, trap refers to the transfer of control to a trap handler caused by either an exception or an interrupt.

- Exceptions are synchronous events that originate inside the processor. They are commonly caused by an unusual condition occurring at run time associated with an instruction.

- Interrupts are asynchronous events that originate outside of the processor. They are commonly caused by service requests from system peripherals.

#### 3.3.5.1. Exception Handling

The Nios V/m processor architecture provides a simple exception controller to handle all exception types. Each exception, including internal hardware interrupts, causes the processor to transfer execution to an exception address. An exception handler at this address determines the cause of the exception and executes an appropriate exception routine.

You can set the exception address in the **Nios V Processor Board Support Package Editor ➤ BSP Linker Script**. Nios V/m processor stores the address in machine trap vector (mtvec) CSR register.

All exceptions are precise. The processor completes all instructions that precede the faulting instruction and does not start the execution of instructions that follow after the faulting instruction.

#### Table 24. Exceptions

| Exception                      | Description                                                                                                                                                                                                                                                                                                     |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Instruction Address Misaligned | The core pipeline logic in F-stage detects the exception. This exception is flagged if the core fetched a program counter that is not aligned to a 32-bit word boundary.                                                                                                                                        |  |

| Instruction Access Fault       | The instruction read response signal detects this exception.                                                                                                                                                                                                                                                    |  |

| Illegal Instruction            | The instruction decoder in the D-stage flags this exception if an instruction word contains encoding for an unimplemented or undefined instruction.  The control logic for the CSR read and write flags this exception in the E-stage if a CSR instruction accesses a CSR that is not implemented or undefined. |  |

| Breakpoint                     | The instruction decoder flags the software breakpoint exception EBREAK in the D-stage.                                                                                                                                                                                                                          |  |

| Load Address Misaligned        | The core for the load/store unit in the M-stage detects the misalignment. This exception                                                                                                                                                                                                                        |  |

| Store Address Misaligned       | is flagged if the data address is not aligned to the size of the data access.                                                                                                                                                                                                                                   |  |

| Load Access Fault              | The core for the data read and write response signal detects the exception.                                                                                                                                                                                                                                     |  |

| Store Access Fault             |                                                                                                                                                                                                                                                                                                                 |  |

| Env call from M-mode           | The instruction decoder in the D-stage detects the instruction.                                                                                                                                                                                                                                                 |  |

#### 3.3.5.2. Interrupt Handling

The Nios V/m processor implementation supports the following interrupts:

- Platform interrupts with 16 level-sensitive interrupt request (IRO) inputs.

- Internally-generated Timer and Software interrupt. You can access the timer interrupt register using the Timer and Software interrupt module interface by connecting to the data bus.

During an interrupt, the core writes the program counter of the attached instruction into the machine exception program counter (mepc) register. An interrupt is usually attached to the instruction in E-stage or in the preceding F-stage or D-stage pipeline. The core is not capable of retracting a memory instruction in the M-stage. If an instruction in M-stage flags an exception while an interrupt is pending and ready to be serviced, the core fetches and executes the exception instruction. If a memory or multicycle instruction is pending in the M-stage, for example, the core is waiting for the response, the core does not flag an interrupt until it receives a response for that instruction. Pending interrupts are flagged by their corresponding bits in Machine Interrupt-Pending (mip) register.

An interrupt is taken only when Machine Status Register (mstatus) bit 3 is asserted and bits corresponding to its pending interrupt in Machine Interrupt-pending (mip) register is asserted.

**Table 25.** Interrupt Control and Status Registers/Bits

| Register | Status Registers/Bits                                  | Description                                               |

|----------|--------------------------------------------------------|-----------------------------------------------------------|

| mstatus  | mstatus[3]/Machine Interrupt-Enable (MIE) field        | Global interrupt-enable bit for machine mode              |

| mie      | mie[31:16]/Platform interrupt-enable field             | Platform interrupt-enable bit for 16 hardware interrupts  |

|          | mie[7]/Machine Timer Interrupt-Enable (MTIE) field     | Timer interrupt-enable bit for machine mode               |

|          | mie[3]/Machine Software Interrupt-enable (MSIE) field  | Software interrupt-enable bit for machine mode            |

| mip      | mip[31:16]/Platform interrupt-pending field            | Platform interrupt-pending bit for 16 hardware interrupts |

|          | mip[7]/Machine Timer Interrupt-Pending (MTIP) field    | Timer interrupt-pending bit for machine mode              |

|          | mip[3]/Machine Software Interrupt-Pending (MSIP) field | Software interrupt-pending bit for machine mode           |

### 3.3.5.2.1. Timer and Software Interrupt Module

The timer and software interrupt hosts the following registers:

- Machine Time (mtime) and Machine Time Compare (mtimecmp) registers for timer interrupt.

- Machine Software Interrupt-pending (msip) field for the software interrupt.

The value of mtime increments after every clock cycle. When the value of mtime is greater or equal to the value of mtimecmp, the timer posts the interrupt.

#### 3.3.6. Memory and I/O Organization

You can configure the Nios V/m processor systems. Consequently, the memory and I/O organization varies from system to system. A Nios V/m processor core uses one or more of the following ports to provide access to memory and I/O:

- Instruction manager port: An Arm Advanced Microcontroller Bus Architecture (AMBA) AXI4-Lite Memory-Mapped manager port that connects to instruction memory via system interconnect fabric.

- Data manager port: An AMBA AXI4-Lite Memory-Mapped manager port that connects to data memory and peripherals via the system interconnect fabric.

Nios V/m Processor Core Memory Mapped I/O Access: Both data memory and peripherals are mapped into the address space of the data manager port. Nios V/m processor core uses little-endian byte ordering. Words and half-words are stored in memory with the more-significant bytes at higher addresses. The Nios V/m processor core does not specify anything about the existence of memory and peripherals. The quantity, type, and connection of memory and peripherals are system dependent.

#### 3.3.6.1. Instruction and Data Buses

### 3.3.6.1.1. Instruction Manager Port

Nios V/m processor instruction bus is implemented as a 32-bit AMBA 4 AXI-Lite manager port.

The instruction manager port:

- Performs a single function: it fetches instructions to be executed by the processor.

- Does not perform any write operations.

- Can issue successive read requests before data return from prior requests.

- Can prefetch sequential instructions.

- Always retrieves 32-bit of data. Every instruction fetch returns a full instruction word, regardless of the width of the target memory. The widths of memory in the Nios V/m processor system is not applicable to the programs. Instruction address is always aligned to a 32-bit word boundary.

- Does not require any burst adapter because it is non-bursting.

**Table 26. Instruction Interface Signals**

| Interface              | Signal  | Role                                                                            | Width  | Direction |

|------------------------|---------|---------------------------------------------------------------------------------|--------|-----------|

| Write Address Channel  | awaddr  | Unused                                                                          | [31:0] | Output    |

|                        | awprot  | Unused                                                                          | [2:0]  | Output    |

|                        | awvalid | Unused                                                                          | 1      | Output    |

|                        | awready | Unused                                                                          | 1      | Input     |

| Write Data Channel     | wdata   | Unused                                                                          | [31:0] | Output    |

|                        | wstrb   | Unused                                                                          | [3:0]  | Output    |