Intel Newsroom Archive 2021

December 31, 2021

Published

List of Intel Newsroom articles and news from 2021

In this article:

-

- January 6, 2021: Introducing Intel RealSense ID Facial Authentication

- January 7, 2021: Intel Unveils New Partner Alliance to Unify the Channel

- January 7, 2021: Turn a Touch Interface Touchless with Intel RealSense TCS

- January 11, 2021: CES 2021 Intel Announces Four New Processor Families

- January 11, 2021: CES 2021 Intel News Conference – Amnon Shashua It’s Time to Go (Replay)

- January 11, 2021: CES 2021 Intel News Conference – Gregory Bryant Do More with the Power of Computing (Replay & Live Blog)

- January 11, 2021: CES 2021 Intel Starts Production of 10nm Xeon Scalable Processors

- January 11, 2021: CES 2021 Mobileye Innovation Will Bring AVs to Everyone, Everywhere

- January 12, 2021: CES 2021 Under the Hood with Prof. Amnon Shashua (Replay & Live Blog)

- January 12, 2021: Red Hat and Intel Blaze a More Flexible Path to 5G Services

- January 13, 2021: CES 2021 Thomas Friedman and Prof. Amnon Shashua (Replay)

- January 13, 2021: Intel Appoints Tech Industry Leader Pat Gelsinger as New CEO

- January 13, 2021: Intel at CES 2021

- January 13, 2021: Note from Pat Gelsinger to Intel

- January 21, 2021: Intel Reports Fourth-Quarter and Full-Year 2020 Financial Results

- January 26, 2021: Intel Invests Additional $475 Million in Vietnam

- January 26, 2021: Intel Releases Iris Xe Desktop Graphics Cards

- January 26, 2021: Moovit Releases Its 2020 Global Public Transport Report

- January 27, 2021: Intel Appoints Sunil Shenoy as Senior Vice President of Design Engineering Group

- January 28, 2021: Intel Recognized for Workplace Equality and Inclusion

- February 2, 2021: Intel and Google Cloud Team with All of Us Research Program

- February 2, 2021: Intel Embree Wins Academy Scientific and Technical Award

- February 3, 2021: Industry Collaboration Drives Tech Innovations in Agriculture

- February 4, 2021: 11th Gen H35 Processors Fastest Single-Threaded Laptop Performance

- February 9, 2021: oneAPI DPC Features Included in SYCL 2020 Final Spec

- February 11, 2021: Demetics Protects AI-Based Medical Innovation with Intel SGX

- February 15, 2021: Pat Gelsinger Becomes CEO of Intel

- February 16, 2021: Pat Gelsinger’s Note to Intel Employees

- February 17, 2021: Intel Pledges $5M to Develop HBCU Tech Law and Policy Center

- February 18, 2021: People, Processes, Products Define Intel’s Security Strategy

- February 23, 2021: Intel IT Accelerating Intel’s Future

- February 23, 2021: Intel, Google Cloud Aim to Advance 5G Networks, Edge Innovations

- February 24, 2021: Intel’s Thunderbolt Tech Turns 10

- February 24, 2021: Intel’s Thunderbolt Tech Turns 10

- February 24, 2021: Intel’s Thunderbolt Tech Turns 10

- February 25, 2021: Mobileye, Transdev ATS and Lohr Group to Develop AV Shuttles

- March 1, 2021: Intel Achieves AWS High Performance Computing Competency Status

- March 1, 2021: Intel Launches SSD for Everyday Computing, Mainstream Gaming

- March 1, 2021: OEMs and Intel Create New PC Category Ultraportable Gaming

- March 3, 2021: Intel Helps IntellectEU Fight Insurance Fraud with ClaimShare

- March 3, 2021: Intel Security Initiatives

- March 4, 2021: Intel, EXOS Pilot 3D Athlete Tracking with Pro Football Hopefuls

- March 8, 2021: Intel to Collaborate with Microsoft on DARPA Program

- March 8, 2021: Media Alert Intel at SecurityWeek Supply Chain Security Summit

- March 9, 2021: Intel Celebrates 10 Years of Chromebooks

- March 10, 2021: Intel-Powered AI Solution Helps Reduce Diabetic Vision Loss

- March 11, 2021: Intel Declares Quarterly Cash Dividend

- March 12, 2021: Intel Sports

- March 15, 2021: Intel Study Transparency and Security Assurance Drive Preference

- March 15, 2021: Intel’s Cryoprober for Quantum Research is Unlike Any Other Tool

- March 16, 2021: 11th Gen Intel Core Desktop

- March 16, 2021: 11th Gen Intel Core Unmatched Overclocking, Game Performance

- March 16, 2021: Samsung Medison and Intel Help Improve Anesthesia Delivery

- March 17, 2021: Media Alert – Intel Unleashed Engineering the Future

- March 18, 2021: Intel, DARPA Develop Secure Structured ASIC Chips Made in the US

- March 22, 2021: Media Alert Intel to Launch 3rd Gen Intel Xeon Scalable Portfolio

- March 23, 2021: Engineering the Future

- March 23, 2021: Intel CEO Pat Gelsinger Announces IDM 2.0’ Strategy for Manufacturing, Innovation and Product Leadership

- March 23, 2021: Intel Unleashed Engineering the Future (Replay)

- March 24, 2021: Intel AI-Powered Backpack Helps Visually Impaired Navigate World

- March 25, 2021: Intel Announces oneAPI Challenge Winners

- March 26, 2021: Kisaco Research SigOpt is a Leader in AI Software

- March 30, 2021: Intel 2020 Supplier Continuous Quality Improvement Awards

- March 30, 2021: Saudi Arabia Opens Full 6 GHz Band for Wi-Fi

- April 1, 2021: At John Deere, Hard Iron Meets Artificial Intelligence’

- April 6, 2021: 3rd Gen Intel Xeon Scalable Launch (Replay)

- April 6, 2021: 3rd Gen Intel Xeon Scalable Launch

- April 6, 2021: Intel Launches Its Most Advanced Performance Data Center Platform

- April 6, 2021: Intel Teams with Leidos, Fortanix to Accelerate Clinical Trials

- April 6, 2021: Intel Xeon Advances Nasdaq’s Homomorphic Encryption R&D

- April 6, 2021: New Intel Processors Accelerate 5G Network Transformation

- April 7, 2021: Leveraging Technology to Provide Global Pandemic Relief

- April 7, 2021: Media Alert April Intel Partner Connect 2021 (Virtual)

- April 8, 2021: SD Supercomputer Center Selects Habana, Intel for Efficient AI

- April 12, 2021: Mobileye and Udelv Ink Deal for Autonomous Delivery

- April 14, 2021: Intel Names Dawn Jones CDIO and VP of Social Impact

- April 19, 2021: Intel Releases US Economic Impact Study

- April 20, 2021: Ushering in a New Open Standard to Securely Onboard IoT Devices

- April 21, 2021: Intel Unveils Its Largest Solar Farm Outside US

- April 22, 2021: Earth Day at Intel Repair, Reuse, Recycle

- April 22, 2021: Intel Recognizes 2021 US Partners of the Year for Accelerating Innovation

- April 22, 2021: Intel Recognizes Its Partners in Canada during Intel Partner Connect 2021

- April 22, 2021: Intel Reports First-Quarter 2021 Financial Results

- April 26, 2021: Intel Collaborates with Microsoft against Cryptojacking

- April 26, 2021: New Views of Mars Thanks to Intel Tech

- April 27, 2021: Intel SGX Protects German Electronic Patient Records

- April 28, 2021: ESL and Intel Celebrate 20 years of Collaboration

- April 28, 2021: Intel on LinkedIn’s 2021 Top Companies’ List

- April 28, 2021: PCs are Central to Delivering on Our Purpose

- April 29, 2021: Alliance Develops Shared Diversity and Inclusion Goals

- April 30, 2021: New Edge-Native Platform to Deploy Private Networks

- May 2, 2021: Media Alert Intel to Announce New Mexico Investment

- May 3, 2021: Intel Announces New Mexico Investment (Replay)

- May 3, 2021: Intel to Invest $3.5 Billion to Expand New Mexico Manufacturing Operations

- May 5, 2021: Intel World Open Path to Tokyo Kicks off in May

- May 6, 2021: Government Officials Tour Intel’s Oregon and Arizona Manufacturing Sites

- May 10, 2021: Autonomous Robot with Intel Tech Triages COVID-19 Patients

- May 10, 2021: Intel Study Diversity and Inclusion in Gaming

- May 11, 2021: Intel Launches New 11th Gen Core for Mobile

- May 12, 2021: Intel AI Helps Speed Papermaking Process in Europe

- May 12, 2021: Intel and QuTech Demonstrate Advances in Solving Quantum Interconnect Bottlenecks

- May 13, 2021: Corporate Responsibility Report A Letter from Our CEO

- May 17, 2021: Intel Delivers Next-Gen Optane Memory for Laptops

- May 17, 2021: Security is Critical Ingredient to Innovation

- May 18, 2021: Intel on 3BL’s 100 Best Corporate Citizens List

- May 18, 2021: Media Alert Intel COMPUTEX Keynote Innovation Unleashed

- May 18, 2021: ZF and Mobileye Safety Technology Chosen by Toyota

- May 19, 2021: Intel Earns Spot on Gartner Supply Chain Top 25

- May 19, 2021: PING Drives Innovation with Intel, Altair and Dell

- May 20, 2021: Conversational AI Powers Drive-Thru

- May 25, 2021: Intel’s PC Reference Design Program Helps Partners Think Ahead

- May 25, 2021: Media Alert Intel Event at Mobile World Congress

- May 25, 2021: Report Edge Computing Drives Business Innovation

- May 26, 2021: Reinventing Chip Design from the Outside In

- May 28, 2021: Intel Announces Hardware Security Award Winners

- May 30, 2021: World’s Best Processor for Thin-and-Light Windows Laptops Just Got Better

- June 2, 2021: Intel Processors Accelerate Deployment of Functional Safety-Compliant Applications

- June 3, 2021: Intel Security Initiatives

- June 3, 2021: The Long Game Product and Security Assurance

- June 8, 2021: Protecting Against Speculation Vulnerabilities

- June 8, 2021: Technology Collaboration to Close the Digital Divide

- June 9, 2021: Intel’s IDM 2.0’ Strategy Defined in 60 Seconds

- June 11, 2021: 2021 Inventor of the Year There is No Limit'

- June 14, 2021: Intel Unveils Infrastructure Processing Unit

- June 15, 2021: Glassdoor Names Pat Gelsinger a Top CEO

- June 15, 2021: Intel Recommends Stockholders Reject Mini-Tender Offer’ by Tutanota LLC

- June 16, 2021: Drone Video Shows Progress at Four Intel Factories

- June 16, 2021: Intel Forms Government Affairs Advisory Committee

- June 18, 2021: Paving the Way for Smart Factories

- June 21, 2021: Intel is Foundational to Unleashing the Possibilities of 5G

- June 21, 2021: Intel’s Silicon, Software Accelerate 5G, Edge

- June 21, 2021: Intel’s Virtual MWC 2021 Event (Replay)

- June 22, 2021: Ericsson Expands Cloud RAN with Intel Tech

- June 22, 2021: Intel at Mobile World Congress 2021

- June 22, 2021: Intel Makes Changes to Strengthen Execution, Innovation in Critical Business Areas

- June 23, 2021: Intel and Red Hat Showcase New 5G Offerings

- June 24, 2021: Intel Core Processors and Intel Bridge Technology Unleash Windows 11 Experience

- June 28, 2021: New Intel XPU Innovations Target HPC and AI

- June 29, 2021: Updates on Intel’s Next-Gen Data Center Platform, Sapphire Rapids

- June 30, 2021: The Revolutions that Led to Chips Made Like Quilts

- July 12, 2021: Media Alert 'Intel Accelerated' Webcast on July 26

- July 15, 2021: Intel Declares Quarterly Cash Dividend

- July 19, 2021: Intel Elects Andrea Goldsmith to Board of Directors

- July 20, 2021: Mobileye Now Testing AVs in New York City

- July 21, 2021: A Zero Trust Approach to Architecting Silicon

- July 21, 2021: Intel and Airtel Collaborate to Accelerate 5G

- July 22, 2021: Intel Reports Second-Quarter 2021 Financial Results

- July 26, 2021: Intel Accelerated’ Webcast (Replay)

- July 26, 2021: Intel Accelerates Process and Packaging Innovations

- July 26, 2021: Process & Packaging Innovations

- July 28, 2021: Media Alert Intel at Black Hat 2021 and DEF CON 29

- July 29, 2021: Intel Announces New Xeon W-3300 Processors

- July 29, 2021: Intel launches AI For All’ initiative in collaboration with CBSE, Ministry of Education

- July 29, 2021: Intel NUC 11 Extreme Kit Delivers High-End Gaming Experience

- August 2, 2021: Olympic Games Tokyo 2020

- August 2, 2021: Study Intel Evo vPro Answer Legacy PC Barriers

- August 2, 2021: Tokyo 2020 Technologies Fact Sheet

- August 3, 2021: Intel Launches AI for Workforce Program for Students in 18 Community Colleges

- August 3, 2021: Modern Computing Alliance Releases Future is Flexible’ Report

- August 3, 2021: Zero Trust’s Role in Compute Lifecycle Assurance

- August 4, 2021: Esports Programs Help Students Transition to College and Gaming -Related Careers

- August 5, 2021: Advancing Chipmaking, 4,000 Steps at a Time

- August 9, 2021: Intel Oregon Fab Expansion Milestone First Chipmaking Tool Rolls In

- August 10, 2021: Intel, ConsenSys Health Advance Pandemic Research

- August 11, 2021: Intel Appoints Christy Pambianchi as Executive Vice President and Chief People Officer

- August 11, 2021: The Technology Solution to the Power Grid’s Battle with Climate Change

- August 16, 2021: Intel Introduces New High-Performance Graphics Brand Intel Arc

- August 16, 2021: Intel Powers Latest Amazon EC2 General Purpose Instances

- August 19, 2021: Expanding Intel’s Foundry Partnerships A Critical Piece of IDM 2.0

- August 19, 2021: Intel Advances Architecture for Data Center, HPC-AI and Client Computing

- August 19, 2021: Intel Architecture Day 2021

- August 23, 2021: Intel Wins US Government Project to Develop Leading-Edge Foundry Ecosystem

- August 24, 2021: Intel and Submer Advance Data Center Cooling Tech

- August 24, 2021: Media Alert Intel to Keynote at IAA Mobility

- August 25, 2021: Wind River and Intel Collaborate on Leading 5G vRAN Solution for FlexRAN

- August 26, 2021: Intel Appoints Bruce H. Andrews as Corporate VP and Chief Government Affairs Officer

- August 27, 2021: Mobileye and ZEEKR Expand Partnership to Enable Future of Cars

- August 31, 2021: Intel, Leidos Advance COVID-19 Healthcare Initiatives

- September 1, 2021: Intel, Juniper Networks Accelerate Time to Market for Service Provider Future Deployments

- September 2, 2021: Intel, CDW and Chance the Rapper Help Students

- September 7, 2021: Intel and Mobileye at IAA Mobility

- September 7, 2021: Intel CEO Keynotes at IAA Mobility (Event Replay)

- September 7, 2021: Intel CEO Predicts Chips Will Be More than 20% of Premium Vehicle BOM by 2030

- September 7, 2021: Mobileye and SIXT Plan New Robotaxi Service

- September 7, 2021: Mobileye Moves from the Garage to the Streets

- September 8, 2021: Media Alert Intel Innovation Oct. 27-28

- September 13, 2021: Floating School-Bus Sized Tools and More Tour Two Intel Factories

- September 13, 2021: Powered by Intel Technology, Robot Helps Retail Customers Find the Right Computer

- September 16, 2021: Directing Traffic to Maximize the Use of Hybrid Chips

- September 17, 2021: Intel Declares Quarterly Cash Dividend

- September 20, 2021: Intel to Break Ground on Two New Leading-Edge Chip Factories in Arizona

- September 21, 2021: Intel Processors Selected to Power Next-Gen DOE Supercomputers

- September 22, 2021: Surface Lineup Features Four Intel Core Designs, Including Intel Evo and Thunderbolt 4

- September 24, 2021: Intel Breaks Ground on Arizona Fabs (Replay)

- September 24, 2021: Intel Breaks Ground on Two New Leading-Edge Chip Factories in Arizona

- September 24, 2021: It’s Time to Build a More Geographically Diverse Supply Chain

- September 29, 2021: Intel Collaborates with Google Cloud to Accelerate Newest VMs

- September 30, 2021: Intel Advances Neuromorphic with Loihi 2, New Lava Software Framework and New Partners

- September 30, 2021: Maximize the Intel Evo Laptop Experience with Thunderbolt Accessories this Holiday

- October 1, 2021: Intel Celebrates Manufacturing Day

- October 1, 2021: US Competitiveness is at Stake for Chip Manufacturing

- October 5, 2021: Intel, Nokia Accelerate Journey to Industry 4.0

- October 5, 2021: Intel, VMware Join vPro Platform and Workspace ONE

- October 12, 2021: Broad Institute, Intel, Google Advance Biomedical Research

- October 13, 2021: Intel, Decentriq and Swiss Re Improve Data Privacy

- October 18, 2021: Intel AI Mentors Seek to Improve Astronaut Health

- October 20, 2021: Intel Launches Intel Unnati Program to Advance Emerging Technology Skills in India

- October 21, 2021: Intel Reports Third-Quarter 2021 Financial Results

- October 26, 2021: Habana Labs’ Gaudi AI Accelerators Power Amazon EC2 DL1 Instances

- October 26, 2021: Intel, Juniper Networks and Rakuten Symphony Collaborate to Develop Symware

- October 27, 2021: Intel Innovation 2021

- October 27, 2021: Intel Innovation Artificial Intelligence News

- October 27, 2021: Intel Innovation Cloud-Edge Infrastructure News

- October 27, 2021: Intel Innovation DeveloperoneAPI News

- October 27, 2021: Intel Innovation Pervasive Connectivity News

- October 27, 2021: Intel Innovation Spotlights New Products, Technology and Tools for Developers

- October 27, 2021: Intel Innovation Ubiquitous Computing News

- October 27, 2021: Intel Innovation’ Keynote Webcast (Replay)

- October 27, 2021: Intel Unveils 12th Gen Intel Core, Launches World’s Best Gaming Processor, i9-12900K

- October 29, 2021: Intel Powers New Amazon EC2 C6i Instances

- November 1, 2021: Confidential Computing Consortium Announces Gramine 1.0, New Research from Everest Group

- November 2, 2021: Intel Powers New Azure Confidential Computing VMs

- November 2, 2021: Intel, Red Hat Advance Industry 4.0 Ecosystem

- November 3, 2021: Creating a Hybrid-First’ Company

- November 15, 2021: Intel 4004

- November 15, 2021: Intel Marks 50th Anniversary of the Intel 4004

- November 15, 2021: Supercomputing for All is Closer than You Think

- November 15, 2021: The Chip that Changed the World

- November 16, 2021: 12th Gen Intel Core Processors Defined in 60 Seconds

- November 16, 2021: Intel’s Habana Labs Announces Turnkey AI Training Solution

- November 16, 2021: Mall of America Teams with WaitTime, Intel, Cisco

- November 22, 2021: Intel Powers New Amazon EC2 Instance

- November 22, 2021: Intel Teams with Snowflake

- November 29, 2021: Introducing Intel’s Long-Term Retention Lab

- November 29, 2021: Media Alert Intel at AWS reInvent 2021

- November 30, 2021: Intel Denoiser Brings The Addams Family 2 to Life

- November 30, 2021: Looking Ahead to 2022 Top Security Predictions

- December 2, 2021: Turning Power into Intelligence for 12th Gen Chips

- December 6, 2021: Inspur, Ruijie, Silicom Expand Intel IPU Ecosystem

- December 6, 2021: Intel Announces Intent to Take Mobileye Public

- December 7, 2021: Intel Helps Facilitate AI Language Recognition

- December 7, 2021: Media Alert Powering the Metaverses

- December 8, 2021: Intel Launches Integrated Photonics Research Center

- December 9, 2021: Media Alert Intel at IEEE HOST Summit 2021

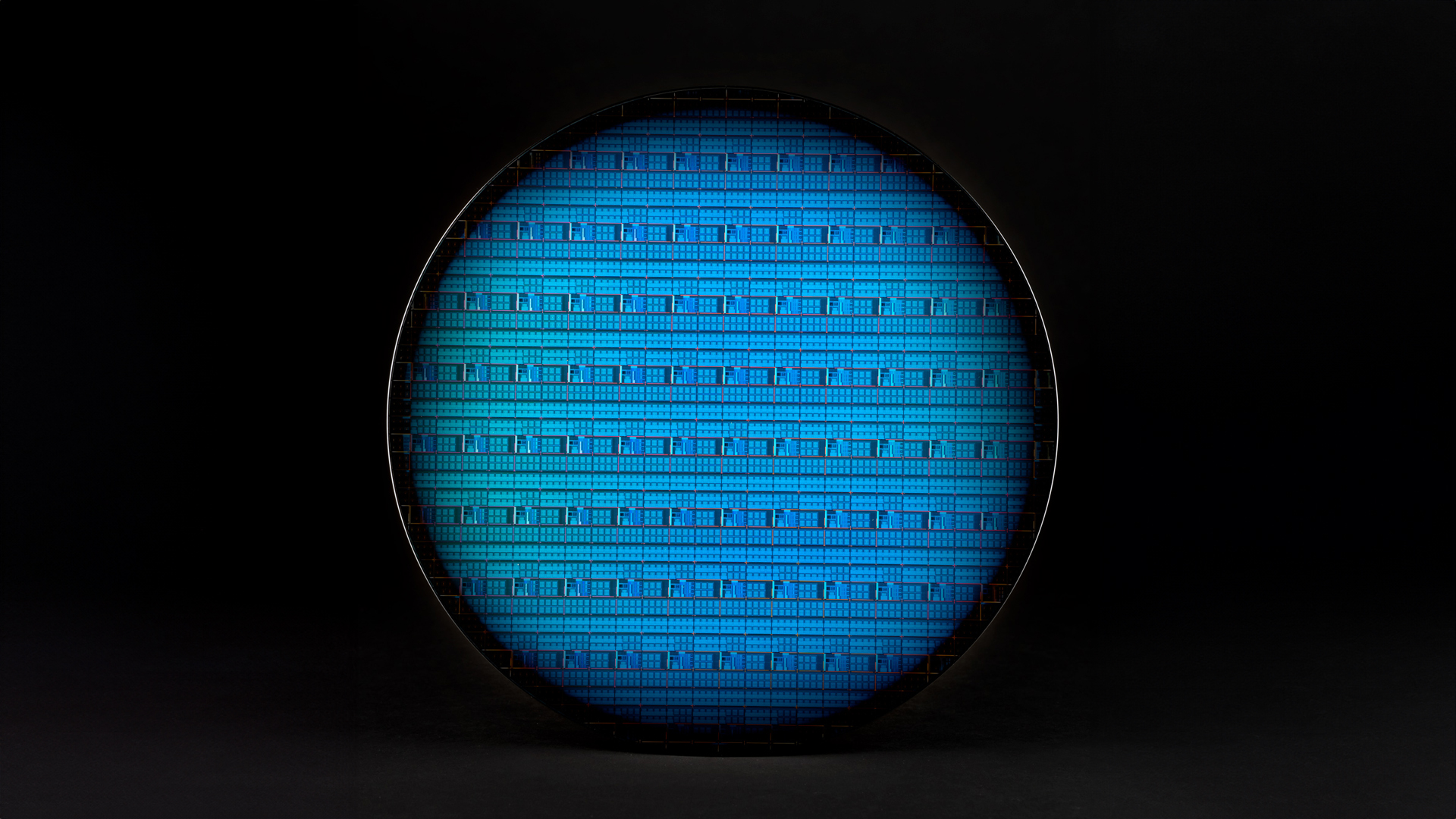

- December 11, 2021: Intel Breakthroughs Propel Moore’s Law Beyond 2025

- December 13, 2021: Mobileye Celebrates 100 Million EyeQ Chips Shipped

- December 14, 2021: Powering the Metaverse

- December 16, 2021: Mobileye Autonomous Cars Piloting in Paris

- December 21, 2021: EUV The Most Precise, Complex Machine at Intel

- December 22, 2021: Intel Empowers Developers with oneAPI 2022 Toolkits

- December 23, 2021: Update Media Alert Intel, Mobileye at CES 2022

- December 27, 2021: Intel, GoodMaps Work on Safe Indoor Navigation

- December 27, 2021: Making the Magic Film’ that Traps Photons for DNA-Sized Features in Silicon

- December 29, 2021: Intel Sells SSD Business and Dalian Facility to SK hynix