Visible to Intel only — GUID: pwk1702492908254

Ixiasoft

Visible to Intel only — GUID: pwk1702492908254

Ixiasoft

4.3.5. Compiling the Design

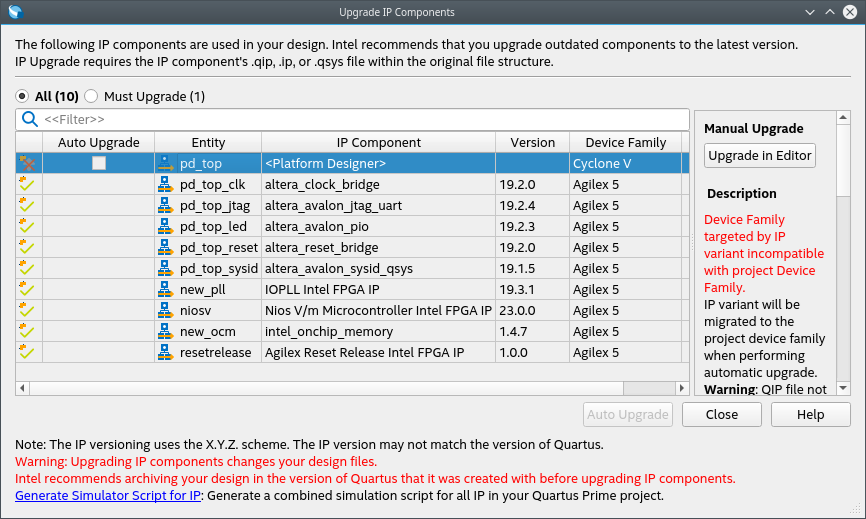

As you can observe, the IP cores have been automatically upgraded to target Agilex™ 5. The Cyclone® V-targeted pd_top entity cannot be removed as it is a Platform Designer file. You continue to see it because the QIP file is still included in the project.

To remove the pd_top file, perform the following steps:

- Click Project > Add/Remove Files in Project.

- Remove the pd_top.qip file in the Files dialog.

Figure 33. Files Dialog

- Click Apply.

- Click OK. The IP Upgrade Required sign disappears.

- Compile the design by clicking Processing > Start Compilation. Compilation might take about 10 minutes to complete. Once the compilation ends, you have successfully completed the design migration from Cyclone® V to the Agilex™ 5 device.