Visible to Intel only — GUID: skf1662727661479

Ixiasoft

Visible to Intel only — GUID: skf1662727661479

Ixiasoft

3.2. E-Tile Port Enablement Guidelines and Restrictions

| Subsystem Port | E-tileTransceiver Channel | EHIP Core |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 1 | 0 |

| 2 | 2 | 0 |

| 3 | 3 | 0 |

| - | PTP Channel (4) | 0 |

| - | PTP Channel (5) | 0 |

| - | PTP Channel (6) | 1 |

| - | PTP Channel (7) | 1 |

| 4 | 8 | 1 |

| 5 | 9 | 1 |

| 6 | 10 | 1 |

| 7 | 11 | 1 |

| 8 | 12 | 2 |

| 9 | 13 | 2 |

| 10 | 14 | 2 |

| 11 | 15 | 2 |

| - | PTP Channel (16) | 2 |

| - | PTP Channel (17) | 2 |

| - | PTP Channel (18) | 3 |

| - | PTP Channel (19) | 3 |

| 12 | 20 | 3 |

| 13 | 21 | 3 |

| 14 | 22 | 3 |

| 15 | 23 | 3 |

General guidelines of Subsystem port configurations:

- Enable the same number of port(s) as specified in NUM_ENABLED_PORTS parameter.

- Click File > Refresh System whenever you modify port configurations to ensure parameter options are displayed correctly.

- 100G CAUI-4 is considered as a single port configuration and can only be enabled on port 0/4/8/12. When any of the four ports are configured as 100G CAUI-4 profile, the remaining three ports in the same EHIP Core is hidden in the IP GUI.

- When configuration of a port matches the configuration of the previous port in the same EHIP Core, this message is displayed at the bottom of the port configuration:

hssi_ss:PORT <n> configuration matches with PORT <n-1> configuration

In the IP configuration tab, the parameters are only available to be configured for the first port. Parameters of subsequent matching port(s) are hidden and would match the settings of the first port.

- Like E-tile Hard IP for Ethernet channel placement, the E-tile transceiver requires RS-FEC to be enabled on contiguous ports only.

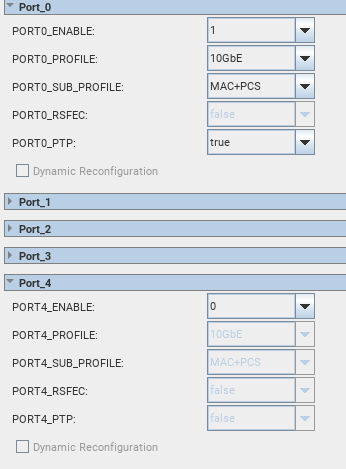

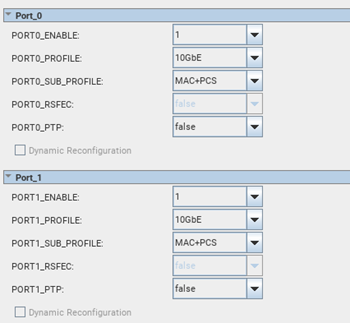

- For EHIP Core 1 (Port 4/5/6/7) and EHIP Core 3 (Port 12/13/14/15), PTP-enabled multi-port design must be configured in sequence, starting from the first port of the EHIP Core. For example, enable PTP starting from Port 4, followed by Port 5, 6 and 7 for 4-port PTP design on EHIP Core 1.

- For EHIP Core 0 (Port 0/1/2/3) and EHIP Core 2 (Port 8/9/10/11), PTP- enabled multi-port design must be configured in reverse sequence, starting from the last port of the EHIP Core. For example, enable PTP starting from Port 3, followed by Port 2, 1 and 0 for 4-port PTP design on EHIP Core 0.

If the expected sequence is not observed for EHIP Core 0 and 2, the IP Core automatically enables the subsequent PTP port(s) to align with E-tile channel placement rules. For example, if Port 0 is enabled with PTP before Ports 3,2,1 is configured, the IP Core automatically enables the Ports 3,2,1 with PTP.