Visible to Intel only — GUID: dfe1693324304116

Ixiasoft

Visible to Intel only — GUID: dfe1693324304116

Ixiasoft

8.5.7.2. Routing Guidelines for LPDDR5 Memory Down Topology

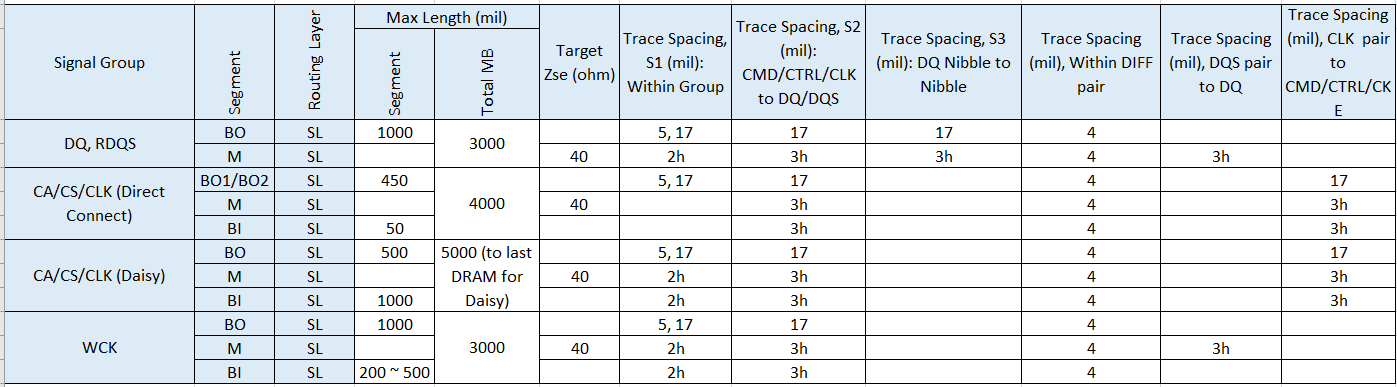

The following table provides comprehensive routing guidelines (recommended trace impedance and length) for each LPDDR5 signal, based on a memory down topology. For example, the maximum length of the main trace routing can be derived from total trace length by subtracting the break-out and break-in trace segment lengths.

The following table shows physical trace segment routing guidelines, including the target impedance of routing for each signal and the minimum space between signal traces on the same layer. The PCB designer must meet the impedance target criteria. The h in the table indicates the minimum substrate height from signal layer to reference layer. Ensure that you follow the trace-to-trace-edge gap/space criteria in the guideline, based on h in various stackups.

|

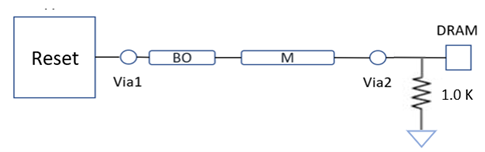

Reset signal routing design also follows the CMD/ADD/CTRL routing design. Maintain at least 3x h edge-to-edge spacing from the Reset signal to other signals on the same layer. There is no requirement to have skew matching between Reset signal and CLK signal. Altera recommends using a 1K-ohm pull-down resistor for Reset termination as shown in the figure below.

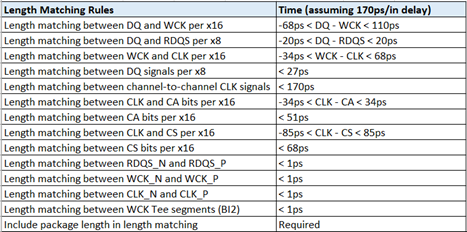

Skew matching for the LPDDR5 interface consists of both package routing skew and PCB physical routing skew. You must maintain skew matching of CA and CTRL with respect to the clock signals to ensure signals at the receiver are correctly sampled. In addition, there are skew matching requirements for DQ and DQS within a byte group, DQS and CLK.

The following table provides a detailed skew matching guideline to facilitate PCB trace routing efforts. The length matching criteria in the table below represents a default PCB on an Altera platform board design. Skew matching criteria must be always followed in any other stackup.

|

LPDDR5 eye margin is sensitive to crosstalk, especially when the signals are routed on deep layers in the stackup. The deep-layer vertical transition induces more vertical coupling between signals and hence more crosstalk. You can perform simulation to determine the maximum stub length, trace length, routing layer, and so forth.

| Memory | LPDDR5 | |

|---|---|---|

| Signal; Group | DQ | |

| Board Thickness (mil) | 65mil or 120mil (Routing must be on upper layers, max via transition depth <=50mil) | 65mil or 120mil (Routing must be on upper layers, max via transition depth <=50mil) |

| Maximum Z-transition height (mil) | 50 | 50 |

| PCB Stripline Trace Impedance (Ohms) | 40 | 40 |

| Memory Configuration | Memory Down | Memory Down |

| # of Rank | 1 (x16 bit or x32 bit Double Die) | 2 (x 16 or x 32 bit) |

| Maximum Length Total (Inch) | 3.0 | 3.0 |

| Notes | Maximum package length in FPGA design is shorter than 34mm. | |