Visible to Intel only — GUID: kor1638953694587

Ixiasoft

Visible to Intel only — GUID: kor1638953694587

Ixiasoft

4.7.3.1.2. Software Design Flow

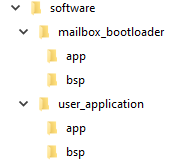

This section provides the software design flow to generate and build the Nios® V processor software project for the Bootloader via SDM and Nios® V application. To ensure a streamlined build flow, you are encouraged to create a similar directory tree in your design project. The following software design flow is based on the following directory tree.

- In your design project folder, create a folder named software.

- In the software folder, create two folders named mailbox_bootloader and user_application.

- In the mailbox_bootloader folder, create two folders named app and bsp.

- In the user_application folder, create two folders named app and bsp.