Visible to Intel only — GUID: qvu1701121056974

Ixiasoft

Answers to Top FAQs

1. FPGA Simulation Basics

2. Siemens EDA QuestaSim* Simulator Support

3. Synopsys VCS* Support

4. Aldec Active-HDL and Riviera-PRO Support

5. Cadence Xcelium* Parallel Simulator Support

6. Quartus® Prime Pro Edition User Guide Third-party Simulation Archive

A. Quartus® Prime Pro Edition User Guides

1.1. FPGA Simulation Essential Elements

1.2. Overview of Simulation Tool Flow

1.3. Simulation Tool Flow

1.4. Supported Simulation Flows

1.5. Supported Hardware Description Languages

1.6. Supported Simulation Types

1.7. Supported Simulators

1.8. Post-Fit Simulation Support by FPGA Family

1.9. Automating Simulation with the Run Simulation Feature

1.10. Using Precompiled Simulation Libraries

1.11. FPGA Simulation Basics Revision History

1.9.3.1. Specifying Required Simulation Settings for Run Simulation (Batch Mode)

1.9.3.2. Optional Simulation Settings for Run Simulation (Batch Mode)

1.9.3.3. Launching Simulation with the Run Simulation Feature

1.9.3.4. Running RTL Simulation using Run Simulation

1.9.3.5. Output Directories and Files for Run Simulation

Visible to Intel only — GUID: qvu1701121056974

Ixiasoft

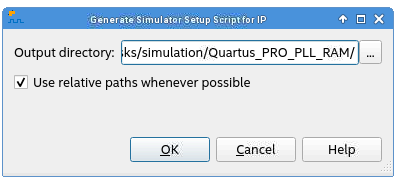

5.2. Generating Simulator Setup Script Templates

You can use simulator setup scripts to help you readily simulate IP cores in your design.

Follow these steps to generate the vendor-specific simulator setup script templates for the IP modules in your design. You can then customize these templates for your specific simulation goals.

- To compile your design, click Processing > Start Compilation. The Messages window indicates when compilation is complete.

- Click Tools > Generate Simulator Setup Script for IP.

- Retain the default settings for the Output directory and also the Use relative paths whenever possible option.

- To generate the setup script templates and vendor-specific sub-folders, including xcelium/ and common/ in the specified output directory, click OK.

Figure 19. Generate Simulator Setup Script for IP Dialog Box