Visible to Intel only — GUID: rsi1586991930914

Ixiasoft

Visible to Intel only — GUID: rsi1586991930914

Ixiasoft

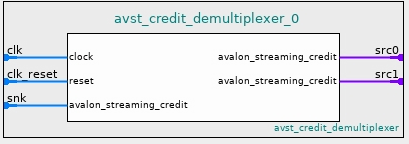

5.3.4. Avalon® Streaming Credit Demultiplexer

The Avalon® Streaming Credit Demultiplexer allows one source to access multiple sinks.

The Avalon® Streaming Credit Demultiplexer:

- Must have a channel signal from the source as an input.

- The channel input from the source must be at least ceil(log2 (NUM_SINKS)) wide, where NUM_SINKS is the number of sinks.

For example, if the source connects to 6 sinks, the channel signal from the source must be at least 3 bits. The least significant ceil(log2(NUM_SINKS)) bits route data from the source to the appropriate sink. For example, if the demultiplexer connects to 5 sinks (sink0, sink1, sink2, sink3, sink4), and the channel signal is 8 bits wide, with a value on the channel bus of 00010010, data routes to sink2.

- The source is responsible for maintaining packet integrity to any sink.

- During a packet transmission, the source must not change the lower order channel bits. Otherwise, the sinks may receive incomplete or invalid packets.

- Is available as the Avalon Streaming Credit Demultiplexer Intel FPGA IP from the Platform Designer IP Catalog.