Visible to Intel only — GUID: pad1526350748341

Ixiasoft

1.1. Comparison of the EPE and the Intel® Quartus® Prime Power Analyzer

1.2. Power Estimations and Design Requirements

1.3. Power Analyzer Walkthrough

1.4. Inputs for the Power Analyzer

1.5. Power Analysis in Modular Design Flows

1.6. Power Analyzer Compilation Report

1.7. Scripting Support

1.8. Power Analysis Revision History

1.4.2.1. Waveforms from Supported Simulators

1.4.2.2. .vcd Files from Third-Party Simulation Tools

1.4.2.3. Signal Activities from RTL (Functional) Simulation, Supplemented by Vectorless Estimation

1.4.2.4. Signal Activities from Vectorless Estimation and User-Supplied Input Pin Activities

1.4.2.5. Signal Activities from User Defaults Only

1.5.1. Complete Design Simulation

1.5.2. Modular Design Simulation

1.5.3. Multiple Simulations on the Same Entity

1.5.4. Overlapping Simulations

1.5.5. Partial Simulations

1.5.6. Node Name Matching Considerations

1.5.7. Glitch Filtering

1.5.8. Node and Entity Assignments

1.5.9. Default Toggle Rate Assignment

1.5.10. Vectorless Estimation

2.5.1. Clock Power Management

2.5.2. Pipelining and Retiming

2.5.3. Architectural Optimization

2.5.4. I/O Power Guidelines

2.5.5. Memory Optimization (M20K/MLAB)

2.5.6. DDR Memory Controller Settings

2.5.7. DSP Implementation

2.5.8. Reducing High-Speed Tile (HST) Usage

2.5.9. Unused Transceiver Channels

2.5.10. Periphery Power reduction XCVR Settings

Visible to Intel only — GUID: pad1526350748341

Ixiasoft

2.6.9. Pipeline Logic to Reduce Glitching

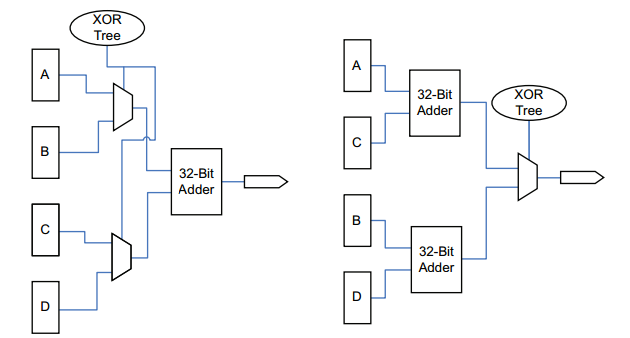

Long chains of cascaded logic blocks can create glitches due to path delay differences between the input signals. Inserting Flip-Flops to cut these long chains terminates the propagation of glitches to consecutive logic cells.

Circuits that heavily use of XIO functions (for example, Cyclic redundancy check) tend to glitch significantly when cascaded. Add pipeline registers or re-architect to reduce signal toggling

Glitch Prone Design

Related Information