1.3. Generating the Synthesizable EMIF Design Example

For the Intel® Stratix® 10 development kit, it is sufficient to leave most of the Intel® Stratix® 10 EMIF IP settings at their default values. To generate the synthesizable design example, follow these steps:

- On the Diagnostics tab, enable the EMIF Debug Toolkit/On-Chip Debug Port and In-System-Sources-and-Probes to provide access to the available debugging features.

- On the Example Designs tab, ensure that the Synthesis box is checked.

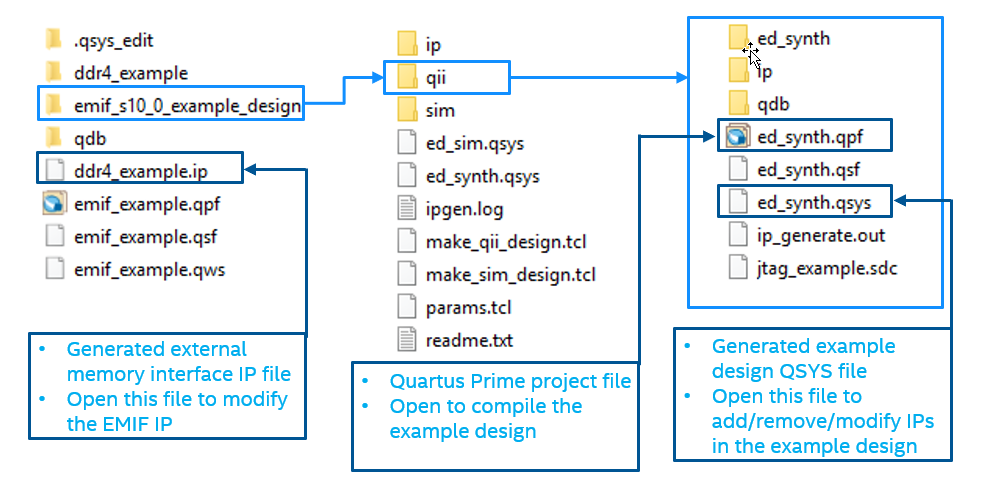

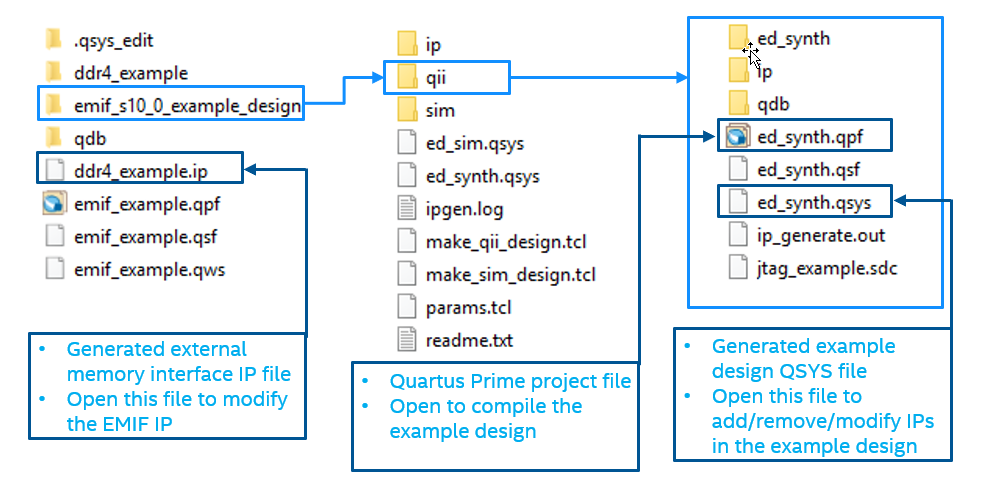

Figure 3. Generated Synthesizable Design Example File Structure

Note:

If you don't select the Simulation or Synthesis checkbox, the destination directory will contain Platform Designer design files, which are not compilable by the Intel® Quartus® Prime software directly, but can be viewed or edited under the Platform Designer. In this situation you can run the following commands to generate synthesis and simulation file sets.

- To create a compilable project, you must run the quartus_sh -t make_qii_design.tcl script in the destination directory.

- To create a simulation project, you must run the quartus_sh -t make_sim_design.tcl script in the destination directory.