Visible to Intel only — GUID: wze1693389994640

Ixiasoft

Visible to Intel only — GUID: wze1693389994640

Ixiasoft

14.6.6.1. Adding a Finite State Machine Block to your DSP Builder Design

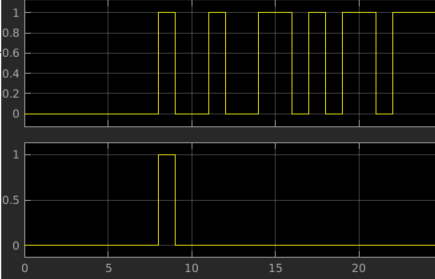

The first state is always the initial state. The word after the state keyword is just a label. You can use any alphanumeric string instead of the word Start. It remains in this state while producing logic low (0) at the output if the x-input is logic low. When the x-input goes high, the Finite State Machine block goes logic high (1) and transitions to the next state. In all subsequent cycles the Finite State Machine ignores the x-input and remains in the second state always setting the output to low (0)

Procedure

- Create a text file simple.fsm containing the following text:

# A simple finite state machine require version 23.3 inputs x netlist transitions Simple : q state Start if (x) Next 1 state Next default Next 0 end - In the Simulink Library Browser, find the Finite State Machine block in DSP Builder for Intel FPGAs - Advanced Blockset > Primitives > Primitive Design Elements

Figure 137. Simulink Library Browser

- Insert this block into a scheduled primitive subsystem in your design. The block initially has no ports for connecting wires.

- Double click on it to open its masked parameter dialog. Type the name of the text file you created earlier.

Figure 138. Specify Model Description File Name

Ports appear on the Finite State Machine block. One input port is x as you specify on the second line of the simple.fsm file. The name of the output port is derived from the names specified after the transitions keyword. The Finite State Machine block always has a go port. It remains in the starting state waiting for a logic high for one cycle on the go input. This port:

Ports appear on the Finite State Machine block. One input port is x as you specify on the second line of the simple.fsm file. The name of the output port is derived from the names specified after the transitions keyword. The Finite State Machine block always has a go port. It remains in the starting state waiting for a logic high for one cycle on the go input. This port:- Should connect to the valid input signal. Because Simulink treats Boolean and ufix1 fixed-point types as distinct, you might have to use a Convert block with output set to Inherit via back-propagation. If your design has no equivalent to the valid signal, connect the go port to a Constant-1 block.

- Allows connecting multiple Finite State Machine blocks in a chain so that when one Finite State Machine completes it passes a token (i.e. a logic high pulse) to the go port of the next Finite State Machine.

Figure 139. Finite State Machine Block Ports