Visible to Intel only — GUID: mwh1410383674324

Ixiasoft

Visible to Intel only — GUID: mwh1410383674324

Ixiasoft

2.6.3. Collection Commands

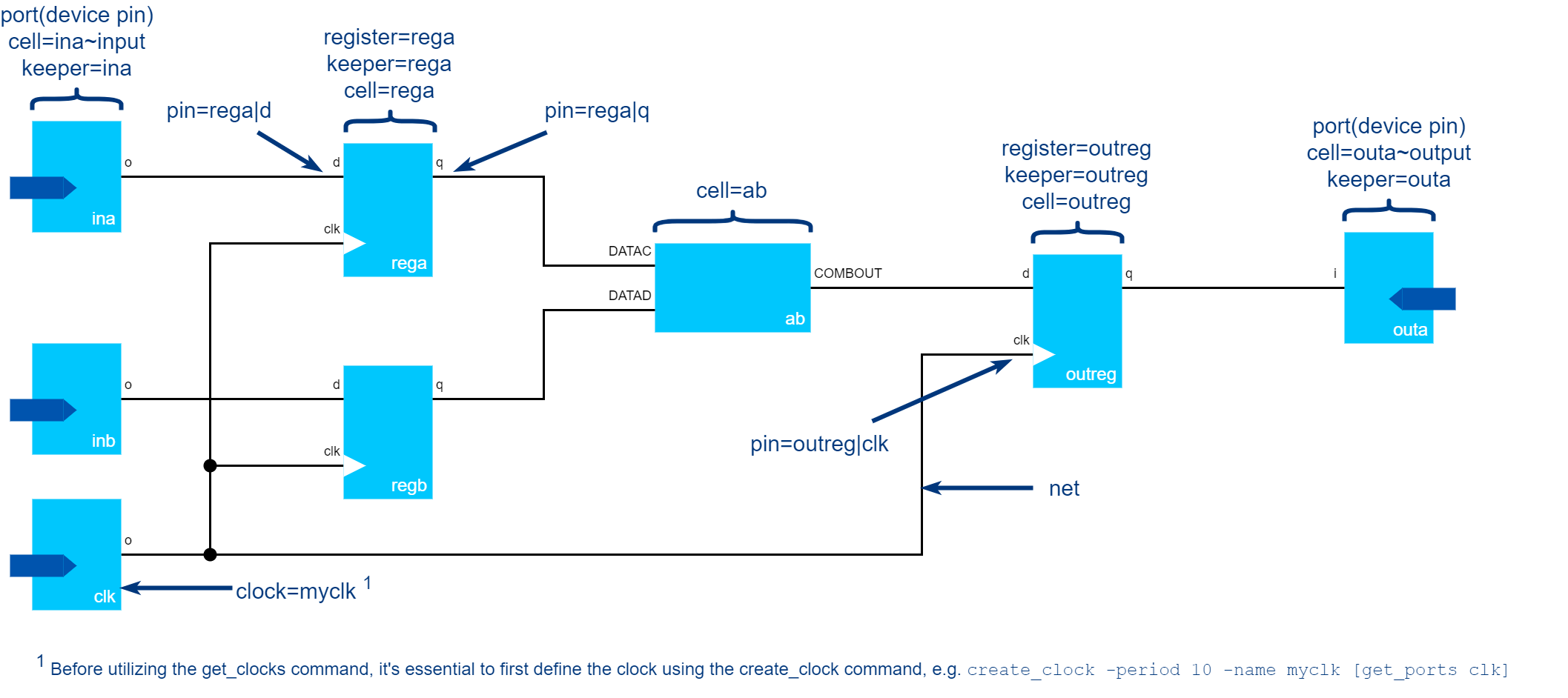

The Timing Analyzer supports functions that return data sets similar to Tcl lists. These data structures, called collections, provide easy access to ports, pins, cells, or nodes from the timing netlist. You can use collection commands with any valid constraints or Tcl commands supported by the Timing Analyzer. Table 1 describes the collection commands that the Timing Analyzer supports. Figure 1 illustrates the elements retrieved by collection commands in a flat design.

Using collection commands instead of raw strings is advisable to ensure precise targeting and minimize ambiguity. Employing the correct collection commands helps ensure that constraints function as intended, and are compatible across different tools. For more information on collections that access the timing netlist, refer to the Using the Quartus Prime Timing Analyzer and the TCL Commands and Packages section in the Quartus Prime Pro Edition User Guide: Scripting.

| Command | Collection Returned |

|---|---|

| all_clocks | Returns a collection of all previously defined clocks in the design. |

| all_inputs | Returns a collection of all input ports in the design. |

| all_outputs | Returns a collection of all output ports in the design. |

| all_registers | Returns a collection of all registers in the design. |

| get_cells | Returns a collection of cells in the design. All cell names in the collection match the specified pattern. Use wildcards to select multiple cells at once. |

| get_clocks | Returns a collection of clocks currently defined in the design. All clock names in the collection match the specified pattern. Use wildcards to select multiple clocks at once. |

| get_nets | Returns a collection of nets in the design. All net names in the collection match the specified pattern. Use wildcards to select multiple nets at once. |

| get_pins | Returns a collection of pins in the design. All pin names in the collection match the specified pattern. Use wildcards to select multiple pins at once. |

| get_ports | Returns a collection of ports (design inputs and outputs) in the design. All ports in the collection match the specified pattern. |

| get_keepers | Returns a collection of non-combinational or "keeper" nodes in the design. Keepers are I/O ports, registers, or clock targets. All keepers in the collection match the specified pattern. |

| get_nodes | Returns a collection of nodes in the design. All nodes in the collection match the specified pattern. |

| get_registers | Returns a collection of registers in the design. All registers in the collection match the specified pattern. |

The following example shows various uses of some Tcl commands with collection commands:

# Create a simple ten ns clock with a 60 % duty cycle targeting the clk port(device pin)

create_clock -period 10 -waveform {0 6} -name clk [get_ports clk]

# The following multicycle applies to all paths ending at registers clocked by clk

set_multicycle_path -to [get_clocks clk] 2

# Create a false path the between clk pin of rega register and the d pin of the regb register

set_false_path -from [get_pins rega|clk] -to [get_pins regb|d]