Visible to Intel only — GUID: uoi1707171878956

Ixiasoft

Visible to Intel only — GUID: uoi1707171878956

Ixiasoft

2.3.5.1.3. Automatic Scope Example for SDC-on-RTL

- Apply global SDC-on-RTL constraints to the design:

# sdc_on_rtl_global.rtlsdc create_clock -period 100MHz [get_ports clk_100] create_clock -period 75MHz [get_ports clk_75]

- Use the File Properties dialog to assign this .rtlsdc file as the SDC File Targeting RTL names or use the following .qsf assignment:

set_global_assignment -name RTL_SDC_FILE <filename>

Figure 63. File Properties Dialog

- Define the following contents of the first entity based .rtlsdc file that is confined to the clk_div modules. In this case, the inner content of the module is unknown, but you can describe the known multiplexed clock behavior of the output in the .rtlsdc:

# clk_dic.rtlsdc set current_instance [get_entity_current_instance]; create_generated_clock -name ${current_instance}_clk_mux_2 -source [get_ports clk_in] -divide_by 2 [get_ports clk_out] create_generated_clock -name ${current_instance}_clk_mux_1 -source [get_ports clk_in] [get_ports clk_out] -addIn contrast, you can still define constraints using the following entity-bound approach for the fifo module that for which inner logic is already known. This approach can be advantageous, especially when multiple instances of the same module share identical constraints.

Figure 64. FIFO Module

set_false_path -from [get_pins wptr_full|wptr[*]|clk] -to [get_pins sync_w2r|rq1_wptr[*]|d] set_false_path -from [get_pins rptr_empty|rbin[4]|clk] -to [get_pins sync_r2w|wq1_rptr[4]|d] set_false_path -from [get_pins rptr_empty|rptr[*]|clk] -to [get_pins sync_r2w|wq1_rptr[*]|d] set_false_path -from [get_pins wptr_full|wbin[4]|clk] -to [get_pins sync_w2r|rq1_wptr[4]|d]

The following .qsf assignments add the clk_div.rtlsdc and fifo.rtlsdc files to the project, and define the file behavior as entity-based SDC-on-RTL:

set_global_assignment -name RTL_SDC_FILE clk_dic.rtlsdc -entity clk_div_wrapper -library clk_div_wrapper set_global_assignment -name RTL_SDC_FILE fifo.rtlsdc -entity fifo -library fifo

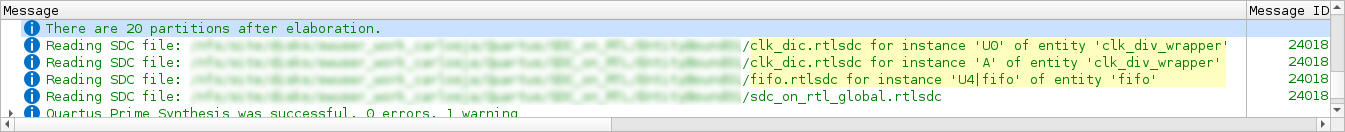

This assignment reduces the scope of each .rtlsdc file to the entities that match the assigned name. During Analysis & Elaboration, messages confirm that the Compiler appropriately applies each .rtlsdc file according to its assigned module.

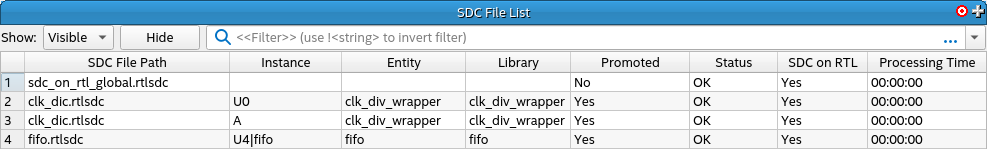

You can further validate the correct application of each .rtlsdc file in the SDC File List report. The SDC File List report contains a comprehensive list, delineating each SDC file read, the file's assigned instance, and the file uses the SDC-on-RTL approach.

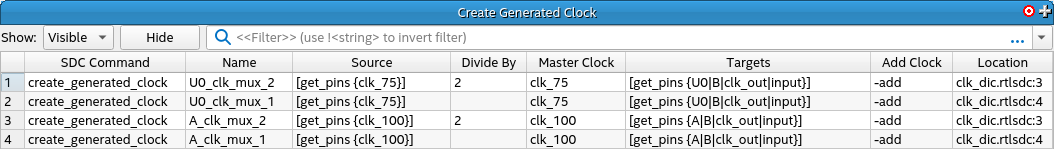

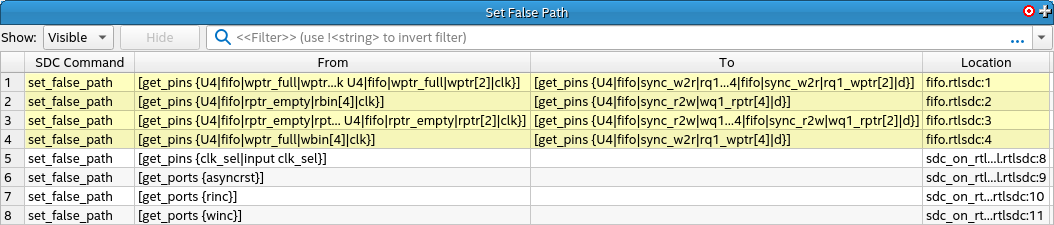

You can further confirm the correct application of constraints according to the constraint target and purpose in the Create Generated Clocks and Set False Paths reports.