2.2. Analog Parameters Settings

For Intel® Quartus® Prime Pro Edition Software version 23.2 and earlier versions, F-tile transceiver analog parameters are set through Intel Quartus Prime software settings file (.qsf).

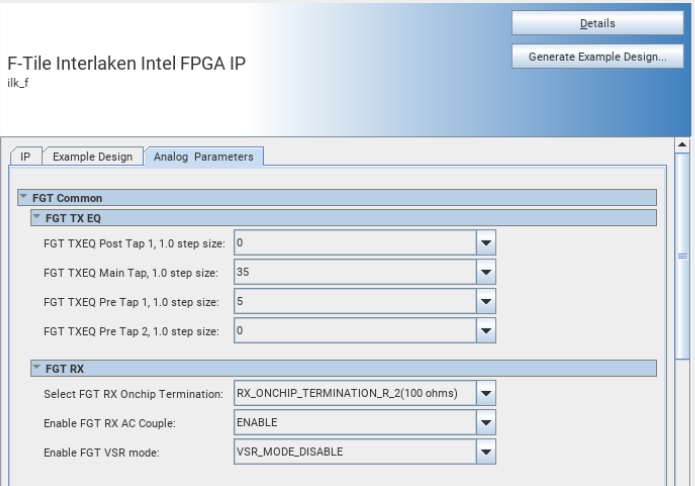

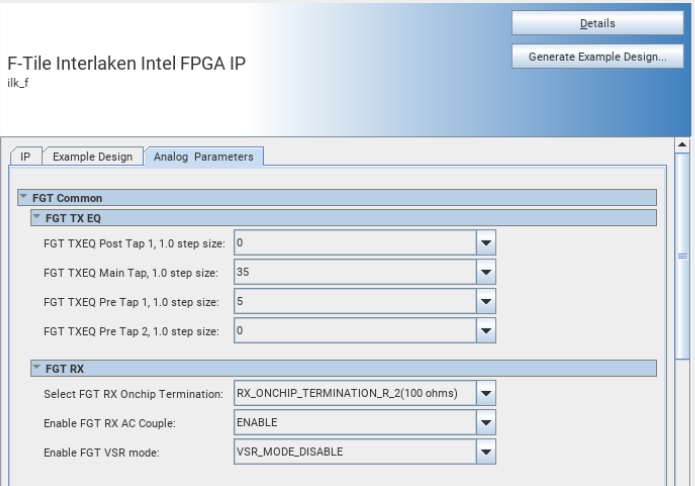

From Intel® Quartus® Prime Pro Edition Software version 23.3 onwards, a GUI based mechanism is implemented to set the analog parameters of F-tile transceivers. The figures below show the FGT and FHT Analog Parameters Tab.

Figure 7. Analog Parameters Tab for FGT

Figure 8. Analog Parameters Tab for FHT

When you are using the development kit, the default analog value may not match your hardware setup. It is recommended that you use the following settings when generating example design for Intel Agilex 7 FPGA I-Series Transceiver-SoC Development Kit.

| Parameter | Value |

|---|---|

| FGT TXEQ Post Tap 1, 1.0 step size | 0 |

| FGT TXEQ Main Tap, 1.0 step size | 35 |

| FGT TXEQ Pre Tap 1, 1.0 step size | 5 |

| FGT TXEQ Pre Tap 2, 1.0 step size | 0 |

| Select FGT RX Onchip Termination | RX_ONCHIP_TERMINATION_R_2 (100ohms) |

| Enable FGT RX AC Couple | ENABLE |

| Enable FGT VSR mode |

|

| Simulator | Instructions |

|---|---|

| Enable FHT TX P&N Invert | Enabled |

| Enable FHT TXOUT Tristate | Disabled |

| Select FHT TX Termination | TXTERM_OFFSET_P0 (90ohms) |

| Enable FHT RX P&N Invert | Enabled |

| Select FHT RX Termination | RXTERM_OFFSET_P0 (90ohms) |

| Select FHT external AC Cap | EXTERNAL_AC_CAP_ENABLE |

| Post-Cursor 4, 0.25 step size | 0.0 |

| Post-Cursor 3, 0.25 step size | 0.0 |

| Post-Cursor 2, 0.25 step size | 0.0 |

| Post-Cursor 1, 0.5 step size | -2 |

| Main-Cursor, 0.5 step size | 18 |

| Pre-Cursor 1, 0.5 step size | -4 |

| Post-Cursor 2, 0.25 step size | -2 |

| Post-Cursor 3, 0.25 step size | 0.0 |