RISC-V, a free and open source instruction-set architecture (ISA), has gained significant traction from both industry giants and emerging startups. A simple, scalable design, coupled with the ability to customize the architecture for specific applications has fueled its popularity in the tech community as a potential disruptor to established proprietary ISAs.

Interest in this technology is so high that the RISC-V Foundation recently merged three events into the RISC-V Summit Europe. A team from Intel traveled to Barcelona for this first-ever conference, where at least 500 attendees took part in a smart mix of technical reports and coffee breaks with demo/poster sessions that encouraged networking while keeping jet lag and meeting fatigue in check.

From startup founders to university researchers, the RISC-V International-organized summit brought together multiple generations of professionals in the semiconductor and other related industries, confirming RISC-V as a high-impact global phenomenon.

Here are first-hand impressions from three of our attendees:

Joachim Aertebjerg SMG EMEA lead on design projects and works to insert Intel into EU investments, such as RISC-V.

Sovereignty and open hardware and software are important to the European Union. The European Commission is investing, via EuroHPC, about $300 million in RISC-V development. Most of the investment will go into development of accelerators based on RISC-V while a smaller portion will support development of software tools and applications. Intel has a lot to offer on the latter and should engage to secure adoption of Intel tools and any real chip development could be an Intel Foundry Services (IFS) customer in the future. This is a long-term business development where Intel has the most to offer with software in the near term.

Charles Macfarlane Chief Business Officer, Codeplay Software*. Codeplay, acquired by Intel in 2022, is now part of the Software and Advanced Technology Group (SATG). He’s responsible for Codeplay's sales, marketing and business development, growing the adoption and momentum of Intel® oneAPI and the SYCL software standard.

The main summit is in California at the end of year, so the European events are often much smaller, typically 100-200 people. That this event attracted around 650 people over three days resulted in a highly credible event for our calendar. At the event, Codeplay announced the oneAPI* Construction Kit to enable specialized processors with lower-level software giving access with SYCL to the extensive oneAPI ecosystem. This was an excellent venue to discuss the many processor solutions being exhibited/presented, especially since the reference version is based on RISC-V. Codeplay is also chair of RISC-V Datacenter/Cloud Computing special interest group (SIG) giving another level of interest for us.

Esperanto Technologies*, Ventana Micro Systems* and Rivos* are creating substantial RISC-V systems for cloud compute, all bringing large number of RISC-V cores as accelerators. The usual programmability issues always appear with them enabling PyTorch* and TensorFlow* but none offering programmable systems. oneAPI would be perfect for this use case, but they’re well entrenched with their own software architecture. MIPS and SemiDynamics* also aiming at vector accelerators using RISC-V, with SiFive* and Andes* continuing to present solutions. Imagination*, Think Silicon* and Huawei* came to present their implementations. The effect was a clutter of suppliers with no one creating sales with accelerators.

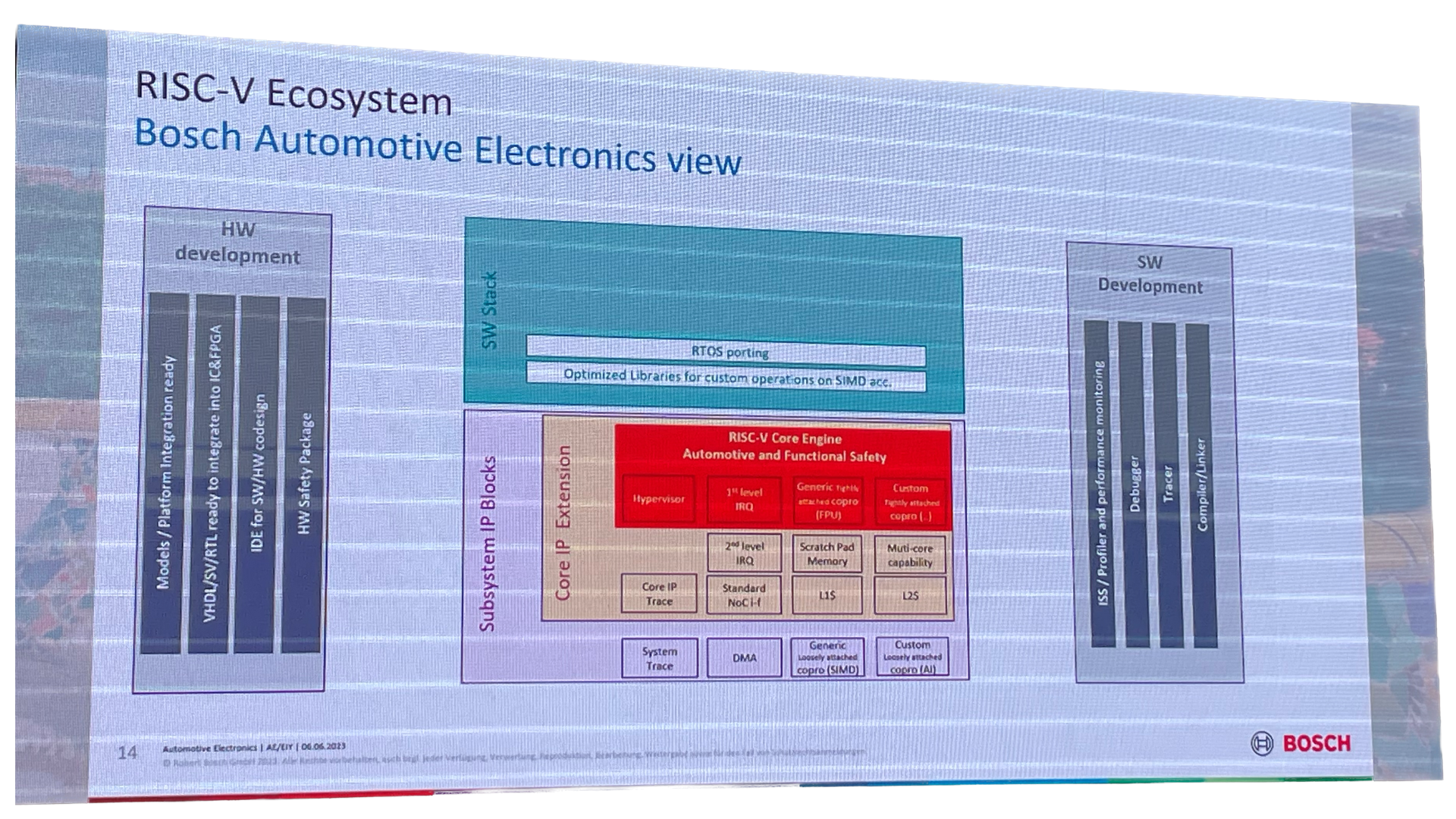

Interestingly, Bosch* came to present an RFI for a system they’ve specified, clearly aiming for companies to propose solutions to fit their functional needs. This felt a little off-piste from the norm: Stating their requirements, then asking for others to propose solutions. It was still good to see them pitch at the Summit, clearly indicating the support of the technology in automotive.

Photo: Joachim Aertebjerg

Finally, Calista Redmond, RISC-V Foundation CEO, emphasized two points in her keynote:

- RISE (Software Ecosystem), which is starting off with basic Linux* enablement (kernel, libraries, toolchains), is expected in time to align its efforts along various long-term development tracks, such as exposing accelerators via SYCL and oneAPI.

- The projected accumulated volume of RISC-V system-on-a-chip (SoCs) reaching 62bn. General networking discussions focused on the types of design wins to achieve high volumes, which are typically microcontrollers and other CPU implementations, giving very little momentum/volumes to major systems e.g. mobile phones, artificial intelligence cloud compute. RISC-V needs to grasp a market segment to show success. Another general observation is that given the high number of companies providing solutions or parts of solutions based on RISC-V there will be some consolidation.

Andrei Warkentin, Senior Principal Engineer in the Software and Advanced Technology Group (SATG), focusing on RISC-V systems software and standards. He’s also the current chair of the Project RISE Technical Steering Committee (TSC).

This was my first RISC-V Summit. My main interests are in software ecosystem readiness and hardware/software interoperability standards, which are basically two of the biggest challenges to serious adoption of RISC-V for products. As a systems engineer, I also wanted to gauge the overall state of the hardware ecosystem and hopefully see some neat demos.

The Summit landed a week after the official launch of the RISE Project, a collaborative effort aiming at speeding up commercial readiness of open source software for RISC-V architecture, and it was exciting to see this new effort called out from the very first keynotes by Calista Redmond and Mark Himelstein, CTO at RISC-V International. I got questions and had interesting discussions with good feedback on RISE - some of which have already shaped the way the RISE Project operates. Lars Bergstrom, Director of Engineering, Android Platform Programming Languages at Google and RISE Board members, gave a short overview of the RISE Project as part of the Android on RISC-V keynote.

I presented Intel's own contributions to a future interoperable RISC-V ecosystem by discussing the challenges in supporting existing off-the-shelf PCIe RAID, network and graphics adapters in RISC-V PCs and servers. I talked about MultiArchUefiPkg, an open source solution developed by Intel that enables reuse of 64-bit x86 UEFI drivers present in such PCIe adapter ROMs with native RISC-V environments and presented possible choices in a long-term solution to the problem of ISA-agnostic firmware drivers for pluggable hardware (to be covered in detail in a separate blog post).

Interest in interoperability was implicit in talks covering the opportunities in automotive electronics, yet unfortunately interoperability standards were not a direct focus in this year's conference. No updates were presented on any of the ongoing work to define what RISC-V PCs, servers or laptops would look like. While much work remains to be done on the BRS (Boot and Runtime Services, i.e. firmware) specification and the newly spun-up server SoC specification, it would have been helpful to have seen the overall RISC-V International-defined vision, sense of direction and immediate goals for the ongoing specs to build-up the appropriate level of industry alignment, support, engagement and excitement for a future of bog-standard RISC-V infrastructure consistent with market-leading Intel Architecture and Arm SystemReady*-compliant solutions.

Computer design and architecture remains a key topic for the Summit, with many talks, demoes and poster presentations focusing on new extensions, microarchitecture, opensource implementations of RISC-V IP and various research explorations. It was great to see independent validation of the AIA and I OMMU specifications and industry excitement over the ratified RISC-V Vector Extension spec with announcements from Semidynamics, Andes Technologies and Esperanto Technologies. Semidynamics had a cool demo of the classic first-person shooter Doom being accelerated with vector instructions, although I wish there were more silicon / hardware demos, especially around proof-of-concept devices.

The open nature of the ISA and surrounding IP is a distinguishing characteristic of RISC-V that enables industry and community participation at an unprecedented scale in evolving the hardware ecosystem in multiple product market directions all at the same time. It was truly humbling to have heard about multiple university student projects going from HDL to fully functional silicon on a used car budget, and I think we're witnessing a paradigm shift in the accessibility of custom silicon technology - from HDL tooling all the way to the fab.

You can catch up with summit videos expected to go live soon on RISC -V International’s YouTube channel.

See you at the upcoming RISC-V Summit in Santa Clara!