Introduction

| IP Core | IP Core Category |

|---|---|

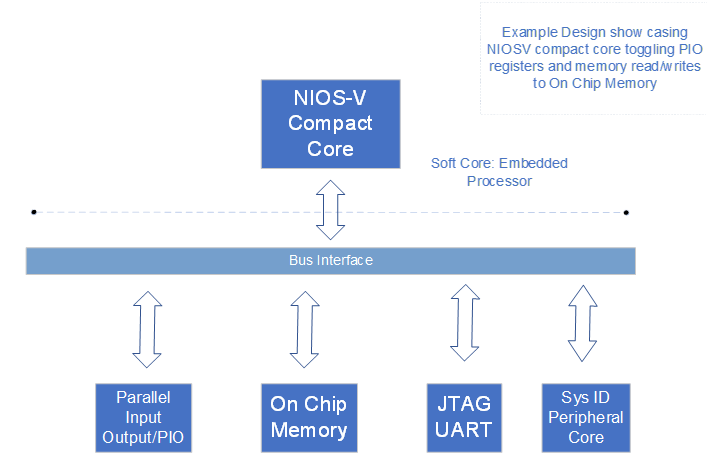

| Nios V/c Compact Microcontroller Intel FPGA IP | Embedded Processor |

| On Chip RAM-II | other |

| JTAG UART | other |

| System ID Peripheral Core | other |

| Parallel Input Output | Peripherals |

Detailed Description

The objective of the design is to accomplish :

1. Toggle the PIO registers which in turn toggles the LED connected on dev kit and readback the registers

2. Write/Read to and from the On Chip memory connected to the embedded processor

3. Readback and print the System Peripheral core register to check of the value written in the IP during configuration

Please refer to the document for details about the design.

Prepare the design template in the Quartus Prime software GUI

Note: After downloading the design example, you must prepare the design template. The file you downloaded is of the form of a <project>.par file which contains a compressed version of your design files (similar to a .qar file) and metadata describing the project. The combination of this information is what constitutes a <project>.par file. You can simply double click on the <project>.par file and Quartus will launch that project.