# Wireless Host Controller Interface Specification for Certified Wireless Universal Serial Bus

**Date:** June 16, 2006

**Revision:** 0.95

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NON-INFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE. Information in this specification is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein, except that a license is hereby granted to copy and reproduce this specification for internal use only.

#### Contact Intel for information on further licensing agreements and requirements.

Intel disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to documents, specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Intel sales office or your distributor to obtain the latest documents and/or specifications, and before placing any product order.

Copies of documents which have an ordering number and are referenced in this specification, or other Intel literature, may be obtained from:

Intel Corporation http://www.intel.com or, call 1-800-548-4725

Copyright © Intel Corporation 1999 – 2006

\* Third-party brands and names are the property of their respective owners.

| Revision | Issue Date | Comments                                                                                                                     |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------|

| 0.84     | 8/8/2005   | Initial Revision                                                                                                             |

| 0.91     | 2/3/2006   | Addressed multiple issues from the initial revision                                                                          |

| 0.92     | 2/23/2006  | Added support to correctly reactivate an inactive Queue Set                                                                  |

| 0.94     | 4/24/2006  | Modified the DRP Notification                                                                                                |

|          |            | Send Command Frame command modified to accept data to be sent in a command frame as opposed to the raw command frame itself. |

|          |            | Minor editorial changes                                                                                                      |

|          |            | Added an a new Event that is returned for Unknown Commands for<br>Command Types sent to the URC                              |

|          |            | Added a Channel Change Notification                                                                                          |

|          |            | Added the ability to selectively receive notifications when an ASIE is sent by a peer device.                                |

|          |            | Removed "Unsecure Control Transfer" from the list of Transfer Types                                                          |

#### **Revision History**

| Revision | Issue Date | Comments                                                                                                                                                         |

|----------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.94a    | 5/7/2006   | Added the URC Scan State when the Start and Stop Beaconing commands can be sent to the URC.                                                                      |

|          |            | Clarified that the only command that may be sent to the URC when its state is transitioning is the Reset Command                                                 |

|          |            | Clarified the Set ASIE notification command in the case multiple<br>Sets are received with the same ASIE Identifier but with different<br>addresses.             |

| 0.95RC   | 6/2/2006   | The URCD must preserve any bits it does not want to modify when making changes to URCCMD register.                                                               |

|          |            | The WHCD must preserve any bits it does not want to modify when making changes to WUSBCMD register.                                                              |

|          |            | Added 2 control bits in the WUSBCMD register to indicate that a QSet was removed from the schedule.                                                              |

|          |            | The URC must have internal storage for the results of commands<br>for any command that it accepts if the command completes when<br>event processing is disabled. |

|          |            | The WHC must deactivate a QHead when the I-Bit is set by the WHCD regardless of whether it is at the burst boundary or not.                                      |

|          |            | The WHC must update DWords 5 and when it retires a qTd/iTD.                                                                                                      |

|          |            | Editorial changes to Chapter 4.                                                                                                                                  |

Please send comments via electronic mail to: whci@Intel.com

This page intentionally left blank.

# TABLE OF CONTENTS

| 1. INT | RODUCTION                                                           | 1  |

|--------|---------------------------------------------------------------------|----|

| 1.1 A  | rchitectural Overview                                               | 2  |

| 1.1.1  | Interface Architecture                                              |    |

| 1.1.2  | WHCI Schedule Data Structures                                       |    |

|        |                                                                     |    |

| 2. RE  | GISTER INTERFACE                                                    | 5  |

| 2.1 P  | CI Configuration Registers                                          | 6  |

| 2.1.1  | CLASSC — CLASS CODE REGISTER                                        |    |

| 2.1.1  | UWBBASE — Register Space Base Address Register                      |    |

| 2.1.2  | PWRMGT — PCI Power Management Interface                             |    |

| 2.1.5  | MSI Capability                                                      |    |

| 2.1.4  | MSI Capaoliity                                                      | /  |

| 2.2 U  | WB Interface Capability Registers                                   | 9  |

| 2.2.1  | UWBCAPINFO — UWB Interface Capability Information Register          |    |

| 2.2.2  | UWBCAPDATA — UWB Interface Capability Data Register                 |    |

|        |                                                                     |    |

|        | WB Radio Controller Registers                                       |    |

| 2.3.1  | URCCMD — URC Command Register                                       |    |

| 2.3.2  | URCSTS — URC Status Register                                        |    |

| 2.3.3  | URCINTR — URC Interrupt Enable Register                             |    |

| 2.3.4  | URCCMDADDR—URC Command Address Register                             | 14 |

| 2.3.5  | URCEVTADDR — URC Event Address Register                             | 15 |

| 2.4 W  | Vireless USB Host Controller Capability and Operational Registers   | 15 |

| 2.4 v  | WHCIVERSION — WUSB Host Controller Interface Version Number         |    |

| 2.4.1  | WHCIVERSION — WUSB Host Controller Interface Version Number         |    |

|        |                                                                     |    |

| 2.4.3  | WUSBCMD — WUSB Command Register                                     |    |

| 2.4.4  | WUSBSTS — WUSB Status Register                                      |    |

| 2.4.5  | WUSBINTR — WUSB Interrupt Enable Register                           |    |

| 2.4.6  | WUSBGENCMDSTS — WUSB Generic Command Status Register                |    |

| 2.4.7  | WUSBGENCMDPARAMS — WUSB Generic Command Parameters Register         |    |

| 2.4.8  | WUSBGENADDR — WUSB Generic Address Register                         |    |

| 2.4.9  | WUSBASYNCLISTADDR — WUSB Current Asynchronous List Address Register |    |

| 2.4.10 | WUSBDNTSBUFADDR — WUSB DNTS Buffer Address Register                 |    |

| 2.4.11 | WUSBDEVICEINFOADDR — WUSB Device Info Address Register              |    |

| 2.4.12 | WUSBSETSECKEYCMD — WUSB Set Security Key Command Register           |    |

| 2.4.13 | WUSBTKID – WUSB Temporal Key ID                                     | 28 |

| 2.4.14 | WUSBSECKEY — WUSB Security Key                                      | 28 |

| 2.4.15 | WUSBPERIODICLISTBASE — WUSB Periodic List Base Register             | 29 |

| 2.4.16 | WUSBMASINDEX — WUSB MAS Index Register                              | 29 |

| 2.4.17 | WUSBDNTSCTRL — WUSB DNTS Control Register                           | 30 |

| 2.4.18 | WUSBTIME — WUSB Channel Time Register                               |    |

| 2.4.19 | WUSBBPST — WUSB Beacon Period Start Time Register                   |    |

| 2.4.20 | WUSBDIBUPDATED — WUSB Device Information Buffer Updated Register    |    |

|        |                                                                     |    |

| 3. | DATA STRUCTURES | 33 |

|----|-----------------|----|

|----|-----------------|----|

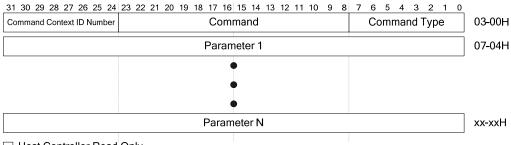

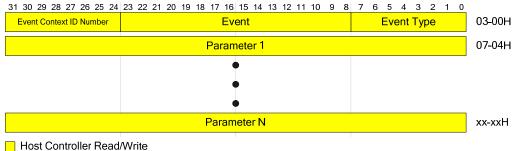

| 3.1 U                                                                                                                                                                                                                                                                                                                          | WB Radio Controller Commands and Events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1.1                                                                                                                                                                                                                                                                                                                          | UWB Radio Controller Command Block (RCCB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                     |

| 3.1.2                                                                                                                                                                                                                                                                                                                          | UWB Radio Controller Event Block (RCEB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                     |

| 3.1.3                                                                                                                                                                                                                                                                                                                          | UWB Radio Controller Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                     |

| 3.1.4                                                                                                                                                                                                                                                                                                                          | Radio Control Notifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                | HC Data Structures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                     |

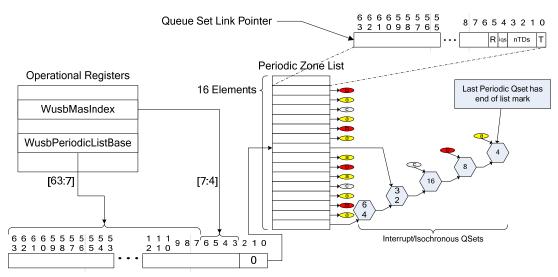

| 3.2.1                                                                                                                                                                                                                                                                                                                          | Periodic Zone List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                     |

| 3.2.2                                                                                                                                                                                                                                                                                                                          | Asynchronous List QHead Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                     |

| 3.2.3                                                                                                                                                                                                                                                                                                                          | Interface Data Structure Model Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                     |

| 3.2.4                                                                                                                                                                                                                                                                                                                          | Queue Element Transfer Descriptor (qTD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                     |

| 3.2.5                                                                                                                                                                                                                                                                                                                          | Isochronous Queue Element Transfer Descriptor (iTD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                     |

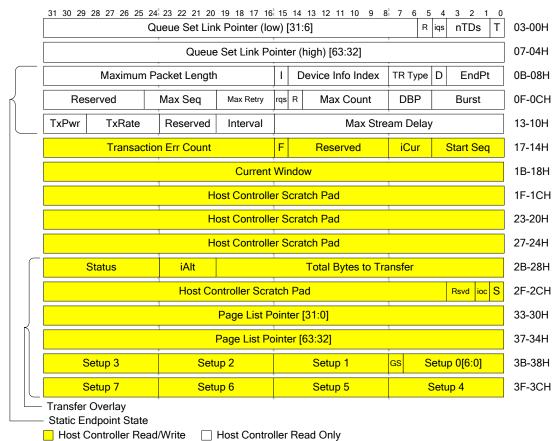

| 3.2.6                                                                                                                                                                                                                                                                                                                          | Queue Head (QHead) with qTD overlay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                     |

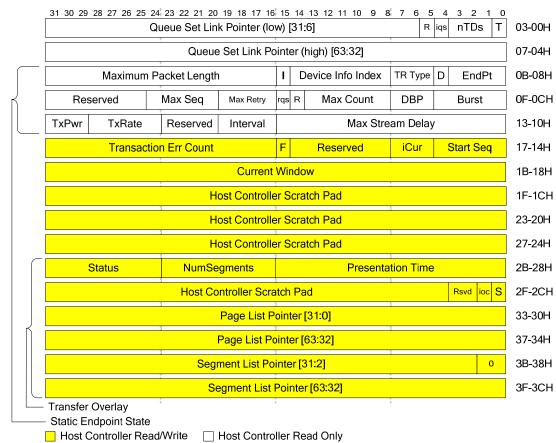

| 3.2.7                                                                                                                                                                                                                                                                                                                          | Queue Head (QHead) with iTD overlay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                     |

| 3.2.8                                                                                                                                                                                                                                                                                                                          | Device Information Buffer Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                     |

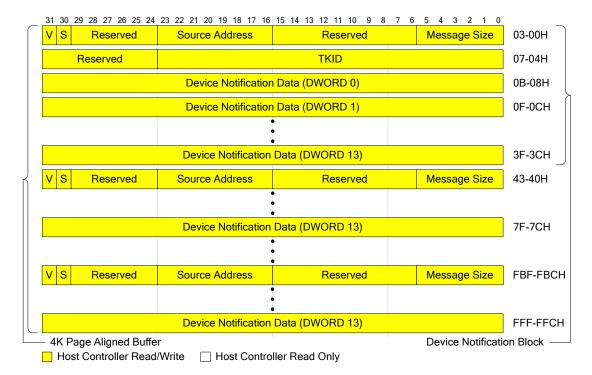

| 3.2.9                                                                                                                                                                                                                                                                                                                          | Device Notification Buffer Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                     |

| 4. OP                                                                                                                                                                                                                                                                                                                          | ERATIONAL MODEL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 79                                                                                                                                                                                                                                                  |

| 4.1 U                                                                                                                                                                                                                                                                                                                          | MC Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 79                                                                                                                                                                                                                                                  |

| 4.1.1                                                                                                                                                                                                                                                                                                                          | URC Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                     |

| 4.1.2                                                                                                                                                                                                                                                                                                                          | WHC Initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                     |

| 4.1.2                                                                                                                                                                                                                                                                                                                          | wric initialization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                     |

| 4.2 W                                                                                                                                                                                                                                                                                                                          | USB Channel Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 82                                                                                                                                                                                                                                                  |

| 4.3 So                                                                                                                                                                                                                                                                                                                         | hedule Traversal Rules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 82                                                                                                                                                                                                                                                  |

| <b></b> .5 D                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                     |

| 4.4 P                                                                                                                                                                                                                                                                                                                          | eriodic Schedule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                     |

| 4.5 A                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                | synchronous Schedule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 85                                                                                                                                                                                                                                                  |

| 4.6 U                                                                                                                                                                                                                                                                                                                          | synchronous Schedule                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 85                                                                                                                                                                                                                                                  |

| 4.6 U<br>4.7 M                                                                                                                                                                                                                                                                                                                 | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>anaging Transfers via Queue Sets                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                     |

| <b>4.6</b> U<br><b>4.7</b> M<br>4.7.1                                                                                                                                                                                                                                                                                          | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>anaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                     |

| <b>4.6</b> U<br><b>4.7</b> M<br>4.7.1<br>4.7.2                                                                                                                                                                                                                                                                                 | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>anaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                     |

| <b>4.6</b> U<br><b>4.7</b> M<br>4.7.1<br>4.7.2<br>4.7.3                                                                                                                                                                                                                                                                        | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>[anaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                     |

| <b>4.6</b> U<br><b>4.7</b> M<br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.4                                                                                                                                                                                                                                                               | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>fanaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                     |

| <b>4.6</b> U<br><b>4.7</b> M<br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.3<br>4.7.4<br>4.7.5                                                                                                                                                                                                                                             | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>lanaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads<br>Blank Transaction for IN Transfers                                                                                                                                                                                                                                                                 | <b></b>                                                                                                                                                                                                                                             |

| <b>4.6</b> U<br><b>4.7</b> M<br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.4<br>4.7.5<br>4.7.6                                                                                                                                                                                                                                             | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>lanaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads<br>Blank Transaction for IN Transfers<br>Inactivate on Next Transaction                                                                                                                                                                                                                               | <b></b>                                                                                                                                                                                                                                             |

| <b>4.6</b> U<br><b>4.7</b> M<br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.3<br>4.7.4<br>4.7.5                                                                                                                                                                                                                                             | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>lanaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads<br>Blank Transaction for IN Transfers<br>Inactivate on Next Transaction<br>Modifying QHead Static Endpoint State                                                                                                                                                                                      | <b></b>                                                                                                                                                                                                                                             |

| <b>4.6</b> U<br><b>4.7</b> M<br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.4<br>4.7.5<br>4.7.6                                                                                                                                                                                                                                             | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>lanaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads<br>Blank Transaction for IN Transfers<br>Inactivate on Next Transaction<br>Modifying QHead Static Endpoint State<br>Reactivating a Queue Set                                                                                                                                                          | <b></b>                                                                                                                                                                                                                                             |

| <b>4.6</b> U<br><b>4.7</b> M<br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.4<br>4.7.5<br>4.7.6<br>4.7.7                                                                                                                                                                                                                                    | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>[anaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads<br>Blank Transaction for IN Transfers<br>Inactivate on Next Transaction<br>Modifying QHead Static Endpoint State<br>Reactivating a Queue Set<br>Control Transfers                                                                                                                                     | <b></b>                                                                                                                                                                                                                                             |

| <b>4.6</b> U<br><b>4.7</b> M<br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.3<br>4.7.4<br>4.7.5<br>4.7.6<br>4.7.7<br>4.7.8                                                                                                                                                                                                                  | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>lanaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads<br>Blank Transaction for IN Transfers<br>Inactivate on Next Transaction<br>Modifying QHead Static Endpoint State<br>Reactivating a Queue Set                                                                                                                                                          | <b></b>                                                                                                                                                                                                                                             |

| <b>4.6</b> U<br><b>4.7</b> M<br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.4<br>4.7.5<br>4.7.6<br>4.7.7<br>4.7.8<br>4.7.9                                                                                                                                                                                                                  | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>[anaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads<br>Blank Transaction for IN Transfers<br>Inactivate on Next Transaction<br>Modifying QHead Static Endpoint State<br>Reactivating a Queue Set<br>Control Transfers                                                                                                                                     | <b></b>                                                                                                                                                                                                                                             |

| <b>4.6</b> U<br><b>4.7</b> M<br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.3<br>4.7.4<br>4.7.5<br>4.7.6<br>4.7.7<br>4.7.8<br>4.7.9<br>4.7.10<br>4.7.11                                                                                                                                                                                     | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>Ianaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads<br>Blank Transaction for IN Transfers<br>Inactivate on Next Transaction<br>Modifying QHead Static Endpoint State<br>Reactivating a Queue Set<br>Control Transfers<br>Interrupt Transfers<br>Isochronous Transfers                                                                                     | <b>85</b><br><b>86</b><br><b>87</b><br><b>88</b><br><b>93</b><br><b>93</b><br><b>94</b><br><b>95</b><br><b>95</b><br><b>95</b><br><b>95</b><br><b>95</b><br><b>96</b><br><b>96</b><br><b>96</b><br><b>96</b><br><b>97</b><br><b>97</b><br><b>98</b> |

| <ul> <li>4.6 U</li> <li>4.7 M</li> <li>4.7.1</li> <li>4.7.2</li> <li>4.7.3</li> <li>4.7.4</li> <li>4.7.5</li> <li>4.7.6</li> <li>4.7.7</li> <li>4.7.8</li> <li>4.7.9</li> <li>4.7.10</li> <li>4.7.11</li> <li>4.8 W</li> </ul>                                                                                                 | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>Ianaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads<br>Blank Transaction for IN Transfers.<br>Inactivate on Next Transaction<br>Modifying QHead Static Endpoint State<br>Reactivating a Queue Set<br>Control Transfers<br>Interrupt Transfers<br>Isochronous Transfers<br>Isochronous Transfers                                                           | <b></b>                                                                                                                                                                                                                                             |

| <ul> <li>4.6 U</li> <li>4.7 M</li> <li>4.7.1</li> <li>4.7.2</li> <li>4.7.3</li> <li>4.7.4</li> <li>4.7.5</li> <li>4.7.6</li> <li>4.7.7</li> <li>4.7.8</li> <li>4.7.9</li> <li>4.7.10</li> <li>4.7.11</li> <li>4.8 W</li> <li>4.8.1</li> </ul>                                                                                  | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>fanaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads<br>Blank Transaction for IN Transfers<br>Inactivate on Next Transaction<br>Modifying QHead Static Endpoint State<br>Reactivating a Queue Set<br>Control Transfers<br>Interrupt Transfers<br>Isochronous Transfers<br>Isochronous Transfers<br>Yireless USB Generic Commands                           | <b></b>                                                                                                                                                                                                                                             |

| 4.6 U<br>4.7 M<br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.4<br>4.7.5<br>4.7.6<br>4.7.7<br>4.7.8<br>4.7.9<br>4.7.10<br>4.7.11<br>4.8 M<br>4.8.1<br>4.8.2                                                                                                                                                                                 | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>[anaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads<br>Blank Transaction for IN Transfers<br>Inactivate on Next Transaction<br>Modifying QHead Static Endpoint State<br>Reactivating a Queue Set<br>Control Transfers<br>Interrupt Transfers<br>Isochronous Transfers<br>Isochronous Transfers<br>Add/Remove MMC IE                                       | <b></b>                                                                                                                                                                                                                                             |

| <ul> <li>4.6 U</li> <li>4.7 M</li> <li>4.7.1</li> <li>4.7.2</li> <li>4.7.3</li> <li>4.7.4</li> <li>4.7.5</li> <li>4.7.6</li> <li>4.7.7</li> <li>4.7.8</li> <li>4.7.9</li> <li>4.7.10</li> <li>4.7.11</li> <li>4.8 W</li> <li>4.8.1</li> </ul>                                                                                  | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>fanaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads<br>Blank Transaction for IN Transfers<br>Inactivate on Next Transaction<br>Modifying QHead Static Endpoint State<br>Reactivating a Queue Set<br>Control Transfers<br>Interrupt Transfers<br>Isochronous Transfers<br>Isochronous Transfers<br>Yireless USB Generic Commands                           | <b></b>                                                                                                                                                                                                                                             |

| <ul> <li>4.6 U</li> <li>4.7 M</li> <li>4.7.1</li> <li>4.7.2</li> <li>4.7.3</li> <li>4.7.4</li> <li>4.7.5</li> <li>4.7.6</li> <li>4.7.7</li> <li>4.7.8</li> <li>4.7.9</li> <li>4.7.10</li> <li>4.7.11</li> <li>4.8 W</li> <li>4.8.1</li> <li>4.8.2</li> <li>4.8.3</li> <li>4.8.4</li> </ul>                                     | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>[anaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads<br>Blank Transaction for IN Transfers<br>Inactivate on Next Transaction<br>Modifying QHead Static Endpoint State<br>Reactivating a Queue Set<br>Control Transfers<br>Interrupt Transfers<br>Isochronous Transfers<br>Isochronous Transfers<br>Set WUSB MAS<br>Channel Stop<br>Remote Wake Poll Enable | <b></b>                                                                                                                                                                                                                                             |

| <ul> <li>4.6 U</li> <li>4.7 M</li> <li>4.7.1</li> <li>4.7.2</li> <li>4.7.3</li> <li>4.7.3</li> <li>4.7.4</li> <li>4.7.5</li> <li>4.7.6</li> <li>4.7.7</li> <li>4.7.8</li> <li>4.7.9</li> <li>4.7.10</li> <li>4.7.11</li> <li>4.8 W</li> <li>4.8.1</li> <li>4.8.2</li> <li>4.8.3</li> <li>4.8.4</li> <li>4.9 Set 100</li> </ul> | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>[anaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads<br>Blank Transaction for IN Transfers<br>Inactivate on Next Transaction<br>Modifying QHead Static Endpoint State<br>Reactivating a Queue Set<br>Control Transfers<br>Interrupt Transfers<br>Isochronous Transfers<br>Isochronous Transfers<br>Set WUSB MAS<br>Channel Stop<br>Remote Wake Poll Enable | <b></b>                                                                                                                                                                                                                                             |

| 4.6 U<br>4.7 M<br>4.7.1<br>4.7.2<br>4.7.3<br>4.7.3<br>4.7.4<br>4.7.5<br>4.7.6<br>4.7.7<br>4.7.8<br>4.7.9<br>4.7.10<br>4.7.11<br>4.8 W<br>4.8.1<br>4.8.2<br>4.8.3<br>4.8.4                                                                                                                                                      | synchronous Schedule<br>pdating Asynchronous and Periodic Schedules<br>[anaging Transfers via Queue Sets<br>Example Queue Set Traversal State Machine<br>Page List Usage for Data Transfer<br>Device Information<br>Managing Transfer Complete Interrupts from QHeads<br>Blank Transaction for IN Transfers<br>Inactivate on Next Transaction<br>Modifying QHead Static Endpoint State<br>Reactivating a Queue Set<br>Control Transfers<br>Interrupt Transfers<br>Isochronous Transfers<br>Isochronous Transfers<br>Set WUSB MAS<br>Channel Stop<br>Remote Wake Poll Enable | <b></b>                                                                                                                                                                                                                                             |

| 4.9.3    | GTK Management                                    |     |

|----------|---------------------------------------------------|-----|

| 4.10 Dev | vice Notification                                 |     |

| 4.11 Pov | ver Management                                    |     |

| 4.11.1   | Transitioning To a Dx State                       |     |

| 4.11.2   | WHC Power Management                              |     |

| 4.11.3   | WHC Resource Requirements for Remote Wake Polling |     |

| 4.11.4   | URC Resource Requirements for Sleep Mode          |     |

| 4.12 WH  | IC Interrupts                                     |     |

| 4.12.1   | Transfer/Transaction Based Interrupt              |     |

| 4.12.2   | WHC Event Interrupts                              |     |

| 4.13 UR  | C Command/Event Processing                        |     |

| 4.13.1   | URC States                                        |     |

| 4.13.2   | Superframe Time Counter                           |     |

| 4.13.3   | Reset                                             |     |

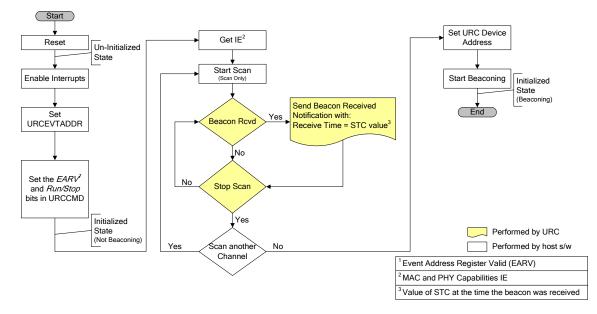

| 4.13.4   | Scan                                              |     |

| 4.13.5   | Beaconing                                         |     |

| 4.13.6   | IE Management                                     |     |

| 4.13.7   | Device Address Management                         |     |

| 4.13.8   | DRP Management                                    |     |

| 4.13.9   | Command Frames                                    |     |

| 4.13.10  | Other Commands                                    |     |

| 4.13.11  | Notifications                                     |     |

| 4.14 UR  | C Interrupts                                      | 141 |

| 4.14.1   | Ready for Command Interrupt                       |     |

| 4.14.2   | Event Ready                                       |     |

| 4.14.3   | Host System Error                                 |     |

| 4.14.4   | Interrupt from Other Interface Functions          | 140 |

| A.1  | PCI Pow | er Management Register Interface1 | 143 |

|------|---------|-----------------------------------|-----|

|      |         | er State Transitions              |     |

| A.1. | 2 Powe  | er State Definitions1             | 144 |

| A.1. | 3 PCI   | PME# Signal1                      | 145 |

|      |         |                                   |     |

This page intentionally left blank.

# 1. Introduction

The Wireless Host Controller Interface (WHCI) specification describes the register-level hardware/software interface between system software and the UWB Multi-Interface Controller (UMC) for the Wireless Universal Serial Bus (Wireless USB) host system. The UMC is a hardware functional component for the WiMedia UWB radio platform and may provide one or more Protocol Adaptation Layer (PAL) functions such as Wireless USB and WiNET.

This specification is intended for hardware component designers, system builders and device driver (software) developers. The reader is expected to be familiar with the *Wireless Universal Serial Bus Specification*, *Revision 1.0.* In spite of due diligence, there may exist conflicts between this specification and the *Wireless Universal Serial Bus Specification*. The *Wireless Universal Serial Bus Specification* takes precedence on all issues of conflict.

This specification also defines an interface for control and management of the WiMedia UWB radio, i.e. the UWB Radio Controller Interface (URCI). The reader is expected to be familiar with the WiMedia MAC layer protocol defined in the *WiMedia MAC Specification (Distributed Medium Access Control (MAC) for Wireless Networks, Release 1.0*). If there are conflicts between this specification and the *WiMedia MAC Specification*, then the *WiMedia MAC Specification* takes precedence on all issues of conflict.

Some key features of the WHCI specification are:

- **Full, Robust Support for all Wireless USB Features.** This specification describes the Wireless USB Host Controller function that correctly supports all compliant Wireless USB devices.

- **Provides a Generic Mechanism to expose Multiple PAL Interfaces.** The UMC can provide one or more PAL functions for the UWB radio platform. This specification defines a mechanism how the hardware exposes multiple PAL interfaces which allows system software to load an appropriate device driver for each interface.

- Common Control and Management Interface of the UWB Radio. The UMC exposes a common interface to control the UWB radio. System software can request the hardware to scan UWB channels, transmit beacons, make bandwidth reservation, etc. This interface also provides a mechanism for the hardware to send asynchronous event notifications to system software. This interface can be commonly used for Wireless USB and all the other PALs exposed by the UMC hardware.

- **System Power Management**. Current PC architectures are providing ubiquitous support for aggressive power management. Wireless USB is a critical component in delivering a consistent, coherent and robust user experience. If the implementation includes PCI configuration registers, then the UMC is required to implement a PCI Power Management Interface.

- **Support for 64-bit Addressing.** Over the implementation lifetime of this specification, it is expected that UMC hardware will be used increasingly in architectures that support more than 32-bits of addressable memory space. For this reason this specification defines all data structures with 64-bits of addressing.

This specification presents two chapters of pure structural definitions of the register space, commands, notifications and schedule interface data structures. These definition chapters contain little or no operational requirements or usage models. The definition chapters are followed by a detailed description of the operational model requirements of the UMC, using the previously defined registers, commands, notifications and schedule interface data structures. The following list summarizes the organization of this specification:

- Section 1.1 provides an overview of the architecture of the UMC.

- Chapter 2 defines the register spaces of the UMC.

- Chapter 3 defines the schedule data structures, command and notification structures used to communicate with the UMC.

- Chapter 4 defines the details of the operational model for the UMC. It uses example behavioral abstractions to describe the operational requirements.

• Appendix A defines the details of the PCI Power Management Interface for the UMC.

#### 1.1 Architectural Overview

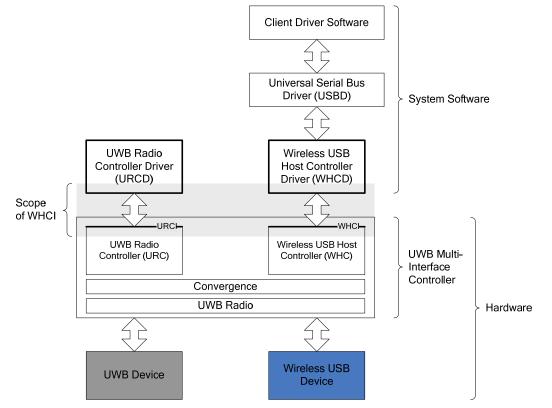

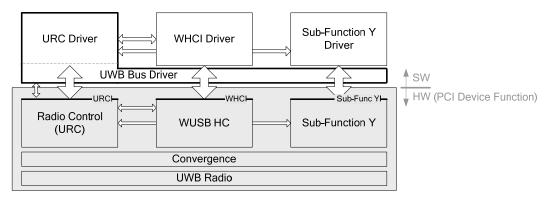

A Wireless USB Host System is composed of a number of hardware and software layers. Figure 1-1 illustrates a conceptual block diagram of the building block layers in a host system that work in concert to support Wireless USB.

#### Figure 1-1. Wireless Universal Serial Bus, System Block Diagram

The component layers are:

- **Client Driver Software.** This software executes on the host PC corresponding to a particular Wireless USB device. Client software is typically part of the operating system or provided with the Wireless USB device.

- **USB Driver (USBD).** The USBD is a system software component that abstracts the details of the particular host controller driver for a particular operating system.

- Wireless USB Host Controller Driver (WHCD). The WHCD provides the software layer between a specific Host Controller hardware and the USBD.

- **UWB Radio Controller Driver (URCD).** The URCD is a system software component that provides control functions of the UWB Radio. It is required in every implementation of a UMC.

- Wireless USB Host Controller (WHC). This is the specific hardware implementation of the Wireless USB host controller.

- **UWB Radio Controller (URC).** This is the standard UWB radio control function that is required in every implementation of a UMC.

- Wireless USB Device. This is a hardware device that performs a useful end-user function. Interactions with Wireless USB devices flow from the applications through the software and hardware layers to the Wireless USB devices.

- **UWB Device.** This is another external hardware device with a UWB radio interface. This device may have one or more PAL functions, e.g. WiNET.

#### 1.1.1 Interface Architecture

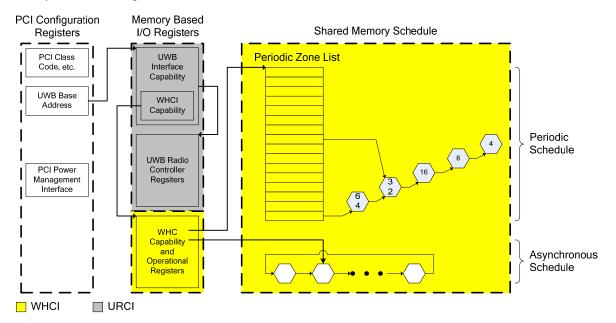

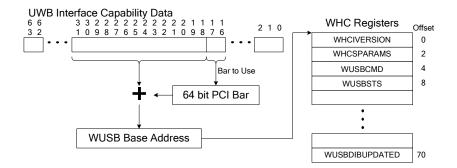

The UMC exposes three interface spaces (see Figure 1-2):

- **PCI Configuration Space**. If the implementation includes PCI registers, they are used for system component enumeration and PCI power management.

- **Register Space.** Implementation-specific parameters and capabilities, plus operational control and status registers. This space, normally referred to as I/O space, must be implemented as memory-mapped I/O space.

- Schedule Interface Space. This is typically memory allocated and managed by the WHCD for asynchronous and periodic schedules.

#### Figure 1-2. General Architecture of UWB Radio Controller and Wireless USB Host Controller Interface

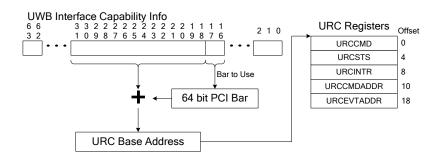

The UMC is a PCI device function that exposes several functional interfaces. The interfaces supported are exposed via capability structures (similar to the standard PCI Capability structure) at the beginning of memory-mapped I/O register space. The UWB Interface Capability Register space identifies the type of each interface and is also used to determine the register space for each interface.

The first interface exposed by the UMC is the UWB Radio Controller Interface (URCI) which is used for the control and operation of the UWB Radio and is mandatory for all hardware implementations. This interface provides a mechanism to exchange message-based commands and notifications between system software and the URC. The location of the UWB Radio Controller Registers is determined from the information in the UWB Interface Capability Register space.

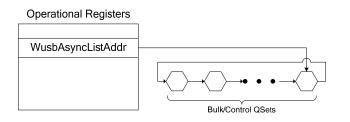

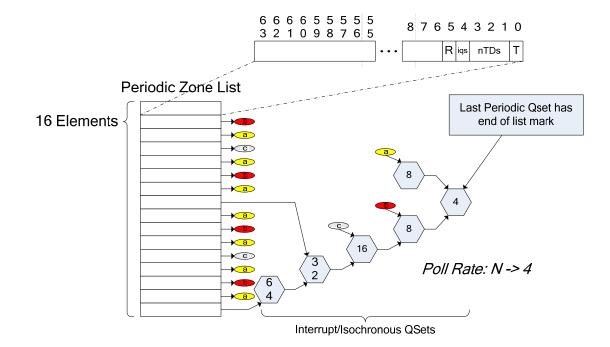

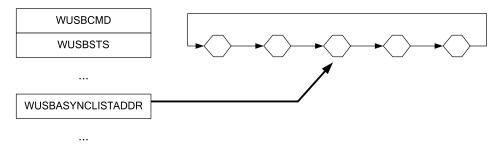

The UMC may also expose one or more PAL interfaces. This specification defines one of these PAL interfaces used to control the Wireless USB Host Controller. The Wireless USB Host Controller Interface (WHCI) provides support for two categories of transfer types: asynchronous and periodic. Periodic transfer types include both isochronous and interrupt. Asynchronous transfer types include control and bulk. Figure 1-2 illustrates that the WHCI schedule interface for Asynchronous and Periodic transfer types.

The asynchronous schedule is a circular list of schedule work items that provides a round-robin service opportunity for all asynchronous transfers. The periodic schedule is based on a time-oriented Periodic Zone<sup>1</sup> List that represents a sliding *window* of time of host controller work items. Software links schedule data structures to the periodic zone list to produce a graph of data structures. The graph represents an appropriate sequence of transactions on Wireless USB.

The WHCI allows software to enable or disable each schedule as well as provides the ability for software to inform the WHC when it has modified either schedule.

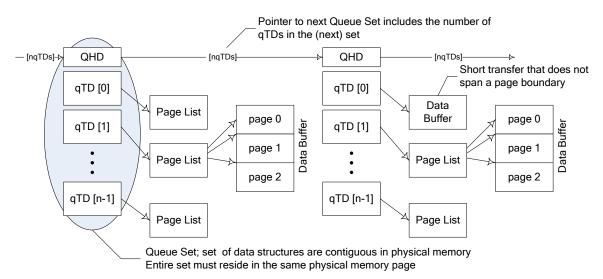

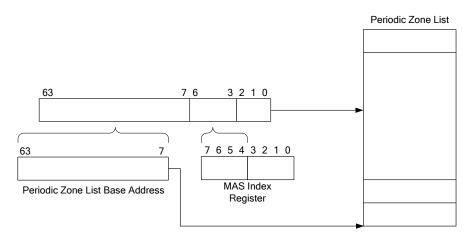

## 1.1.2 WHCI Schedule Data Structures

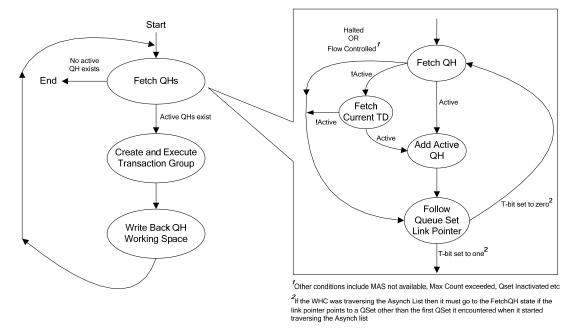

The WHCI manages all transfer types using a buffer queuing data structure. The queuing data structure provides automatic, in-order streaming of data transfers. Software can asynchronously add data buffers to a queue and maintain streaming. Wireless USB-defined short packet semantics are fully supported on all processing boundary conditions without software intervention.

<sup>&</sup>lt;sup>1</sup> A Zone refers to 16 continuous Media Access Slots in a superframe. The first Zone starts at MAS 0 and ends at MAS 15, the second Zone starts at MAS 16 and ends at MAS 31 and so on so forth with the last Zone starting at MAS 242 and ending at MAS 255

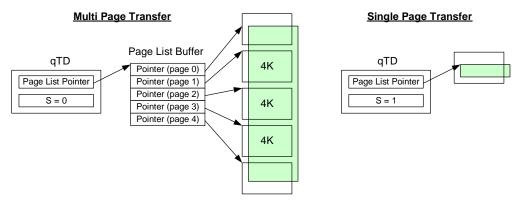

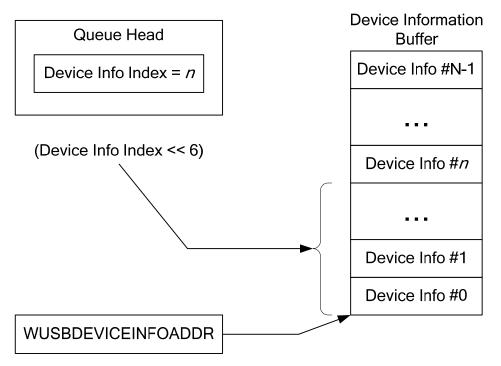

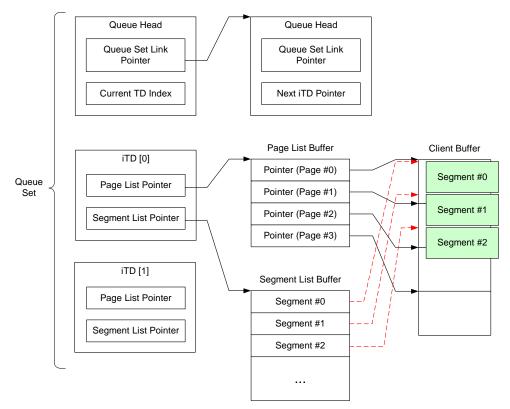

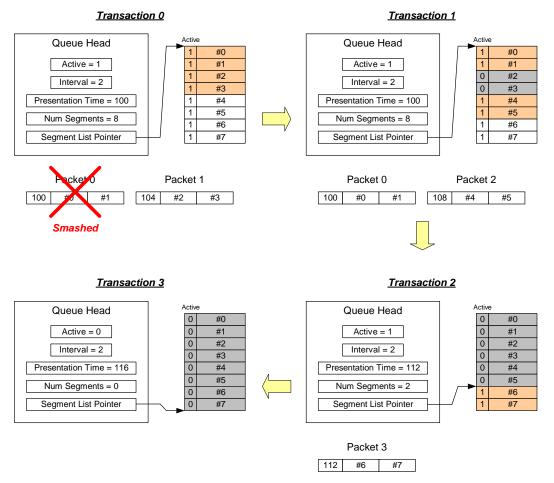

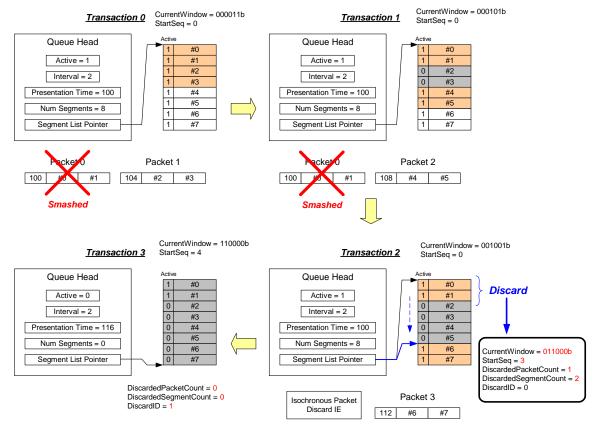

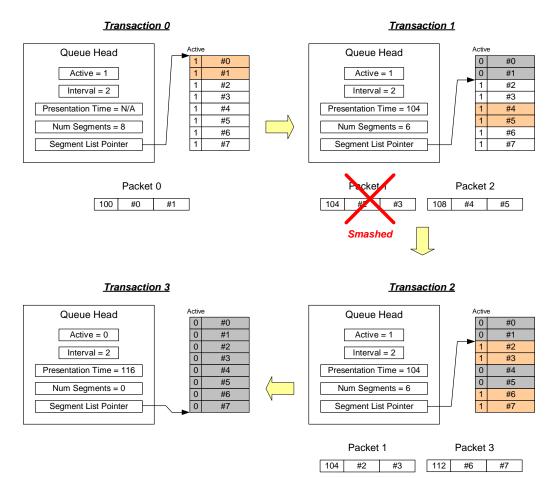

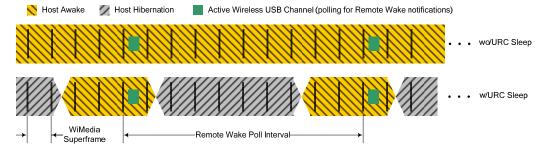

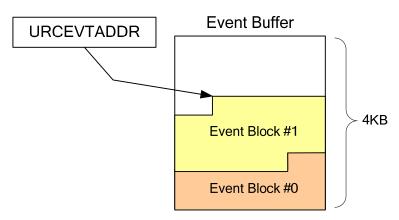

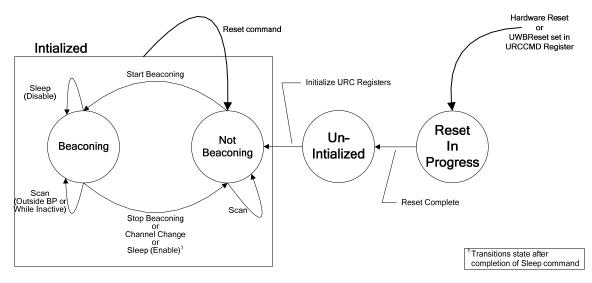

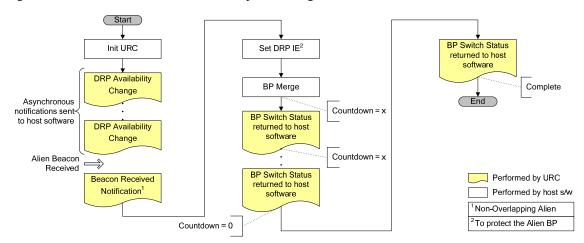

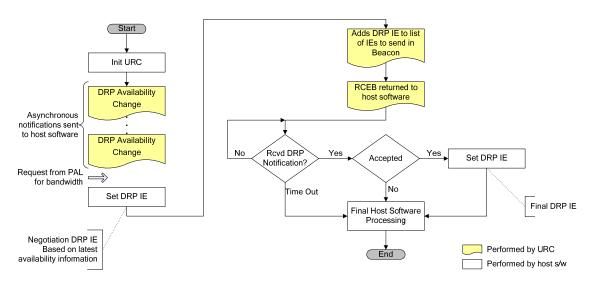

# 2. Register Interface