# **Source-Synchronous Timing** with TimeQuest

Wiki Release 1.2 October 6<sup>th</sup>, 2011

By: Ryan Scoville

#### Introduction:

Although Altera has created much literature on source synchronous interfaces, I find it to still be one of the most difficult things to do in TimeQuest, and field questions quite often. There are many reasons for this difficulty. Third party datasheets spec their interfaces in many different ways. Altera's literature provides multiple strategies for adding constraints, which allows flexibility but often leave users confused. Most material concentrates on entering constraints but without showing how to analyze the results. And perhaps most importantly, with multiple registers working off of multiple edges, the analysis is actually quite complex.

This document is not meant to be a cook-book where the user just cuts and pastes the .sdc into their system. Instead, it starts with the most common and easy to understand scenarios and tries to explain how the constraints and analysis are done. The purpose is to help the user understand what each constraint does and how it relates to their system, so not only can they enter the correct constraint, they can feel confident that the analysis is correct. Once that framework has been built and hopefully understood, we will delve into corner cases and other scenarios that might cause confusion.

#### Notes:

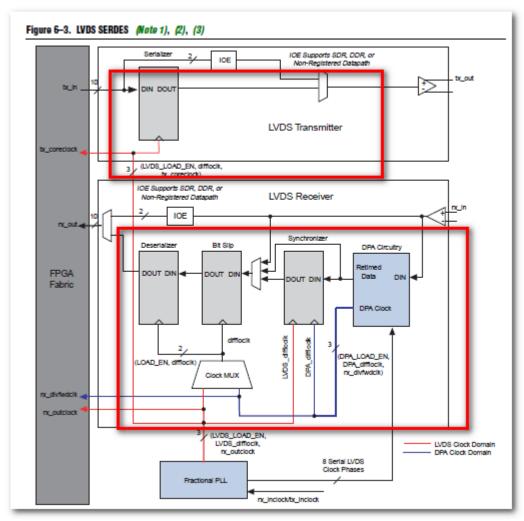

- This document is not mean for dedicated High-Speed SERDES(altlvds) built into many families. The <u>following section discusses why</u>.

- This document assumes the user is familiar with the TimeQuest User Guide at: <a href="http://www.alterawiki.com/wiki/TimeQuest\_User\_Guide">http://www.alterawiki.com/wiki/TimeQuest\_User\_Guide</a>

Specifically Sections 1) Getting Started and 2) Timing Analysis Basics.

- I recommend turning on the Bookmarks when viewing this .pdf, allowing for easier navigation and to help understand the organization

#### Contact:

TimeQuest support is not my primary responsibility, and so I will not be able to directly assist users. That being said, if there is anything ambiguous, incorrect, or missing, please contact me via <a href="www.alteraforum.com">www.alteraforum.com</a>, sending an email to user Rysc. Be sure your account can accept emails too. I also monitor the forum a good amount and will try to answer questions there, as I much prefer helping with issues on the forum rather than direct email, since it can hopefully help multiple users. If you post something and I don't respond, feel free to send me an email through the forum. That being said, if I am unable to respond, please don't be offended.

© 2011 Altera Corporation. The material in this wiki page or document is provided AS-IS and is not supported by Altera Corporation. Use the material in this document at your own risk; it might be, for example, objectionable, misleading or inaccurate.

## **Table of Contents**

| SECTION I: GETTING STARTED                                                               | 4  |

|------------------------------------------------------------------------------------------|----|

| Organization – Suggestions for Using this Document                                       | 4  |

| SOURCE-SYNCHRONOUS BASICS                                                                |    |

| THE KEY TO SOURCE-SYNCHRONOUS PERFORMANCE                                                |    |

| I/O TIMING BASICS                                                                        |    |

| INTRO TO TWO METHODS: EXPLICIT AND IMPLICIT CLOCK SHIFT                                  | 10 |

| SECTION II: THE EXPLICIT CLOCK SHIFT METHOD                                              | 11 |

| Case 1: The FPGA is the receiver and phase-shifts the clock                              | 13 |

| Case 2: The FPGA is the receiver and does not phase-shift the clock                      |    |

| Case 3: FPGA is the transmitter and phase-shifts its clock                               |    |

| Case 4: FPGA is the transmitter and sends a non-shifted clock                            |    |

| EXTERNAL DELAYS OF THE EXPLICIT METHOD                                                   |    |

| FPGA-Centric versus System-Centric                                                       |    |

| Case 3 and Case 4: FPGA is the Transmitter                                               |    |

| BENEFITS OF THE EXPLICIT METHOD                                                          |    |

| REPORT TIMING: PUTTING IT ALL TOGETHER                                                   |    |

| SECTION III: THE IMPLICIT CLOCK SHIFT METHOD                                             | 30 |

| THE IMPLIED PHASE-SHIFT                                                                  | 32 |

| Case 5: FPGA is Receiver, Implicit Method                                                |    |

| Case 6: FPGA is Transmitter, Implicit Method                                             |    |

| REALLY, THE INTERFACE HAS NO CLOCK SHIFT                                                 |    |

| SECTION IV: SDR – SINGLE DATA RATE                                                       | 38 |

| THE SDR EXPLICIT METHOD                                                                  | 39 |

| Case 1: The FPGA is the receiver and centers the clock                                   | 39 |

| Case 2: The FPGA is the receiver and does not center the clock                           |    |

| Case 3: FPGA is the transmitter and phase-shifts its clock                               |    |

| Case 4: FPGA is the transmitter and sends a non-shifted clock                            |    |

| THE SDR IMPLICIT METHOD                                                                  |    |

| Case 5: FPGA is Receiver, Implicit Method                                                |    |

| Case 6 : FPGA is Transmitter, Implicit Method                                            |    |

| SECTION V: MISCELLANEOUS TOPICS                                                          |    |

| Edge-Aligned versus Center-Aligned                                                       |    |

| OUTPUT CLOCK IS UNCONSTRAINED                                                            |    |

| FALSE PATHS FOR LOOSE REQUIREMENTS                                                       | 44 |

| DIFFERING RISE/FALL TRANSFERS: +90° VERSUS -90° CLOCK SHIFTS, NEXT-EDGE VERSUS SAME-EDGE | 10 |

| Transfers  Exactly 90°?                                                                  |    |

| IMPLICIT METHOD: SAME-EDGE TRANSFERS                                                     |    |

| DDR OUTPUTS: WHERE ARE MY REGISTERS?                                                     |    |

| TIMING CLOSURE                                                                           |    |

| HIGH-SPEED DIFFERENTIAL I/O, DPA, CDR                                                    |    |

| SECTION VI: EXTERNAL DEVICE CONSTRAINT EXAMPLES                                          | 61 |

| Examining Common Specs                                                                   |    |

| GENERIC: EXTERNAL DEVICE IS TRANSMITTER/ FPGA IS RECEIVER EXAMPLES                       | 62 |

| TI – ADC/DAC examples                                                                    |    |

| ADS5485 – Based on Case 1  | 65 |

|----------------------------|----|

| ADS4149 – Based on Case 2  | 66 |

| DAC5675a – Based on Case 3 | 69 |

| DAC5681 – Based on Case 4  |    |

| FPGA TO FPGA INTERFACES    |    |

|                            |    |

# **Section I: Getting Started**

## Organization - Suggestions for Using this Document

I had a lot of difficulty in organizing this document. There is a lot of information and a lot of different ways to analyze an interface. It's all there for anyone who wants to read it all, but most people have a specific scenario they want to constrain and don't care about all the subtleties and different options available. On the one hand, I completely understand, while on the other, I have seen user's cut-and-paste constraints without understanding, and end up doing incorrect analysis. Here are three different approaches, from the most difficult to the easiest:

- 1) Read the entire document, or at least the parts that could pertain to your design, i.e. if your FPGA is receiving data, skip the sections where the FPGA a transmitter. It's really not as long as it looks.

- 2) Read this initial Getting Started section, and then go to Section VI: External Device Constraints. This will have many examples of external devices and how they're constrained, and then give explicit instructions on what method to use and how to enter the constraints. Find the one most similar to the device you're interfacing with and follow the instructions. I currently have four good examples based on real TI devices, and would like to add examples from other vendors.

- 3) If the user really wants to constrain their FPGA in ~15 minutes, then just look at the four cases for an Explicit Clock Shift and decide which one applies to them:

- Case 1: The FPGA is the receiver and phase-shifts the clock

- Case 2: The FPGA is the receiver and does not phase-shift the clock.

- Case 3: The FPGA is the transmitter and phase-shifts the clock.

- Case 4: The FPGA is the transmitter and does not phase-shift the clock.

#### Based on that:

- a. Open the Quartus II project for the selected case.

- b. Open the PLL Megawizard and change the frequency to match the user's clock rate.

- c. Open the top level schematic (.bdf) and go to File -> Create HDL File and choose what you need, VHDL or Verilog.

- d. Open ssync\_test .sdc and change the –period options to match the user's clock rate.

- e. For case 2, modify the –waveform option to show a 90° shift based on the clock period.

- f. Change the set\_input/output\_delay constraint's -max and -min values to reflect how much skew the FPGA can have on the data. This is calculated with:

+/- (90° - allowed\_FPGA\_skew)

For example, if DDR interface runs off an 8ns clock, and the user wants to allow 800ps of skew within the FPGA, the calculation is:

+/- (90° - allowed FPGA skew) = +/- (2ns - 0.8) = +/-1.2

The user now knows how much skew they have allowed on the data inside the FPGA, and based on the case selected, if the FPGA is skewing the clock, so they can determine exactly what the FPGA is doing. For example, if the above was used with Case 3, then data would be sent out with a skew of +/-0.8ns and the clock would be sent center-aligned since it has a phase-shift. If it were Case 4, then it would be sent edge-aligned.

Likewise, if the above was used for Case 1, then the FPGA would be allowed to internally skew the data by  $\pm -0.8$ ns and there would be an internal 90° phase-shift of the clock into the middle of the data eye. That means the external device is sending clock/data edgealigned, and that there is  $\pm -1.2$ ns skew from the external device and board skew.

If case 2 were being used, then the FPGA would still be skewing data internally by +/-0.8ns, but it would not be phase-shifting the clock. That means the external device and board layout are still adding +/-1.2ns of data skew, but the external device is center-aligning the clock.

## Source-Synchronous Basics

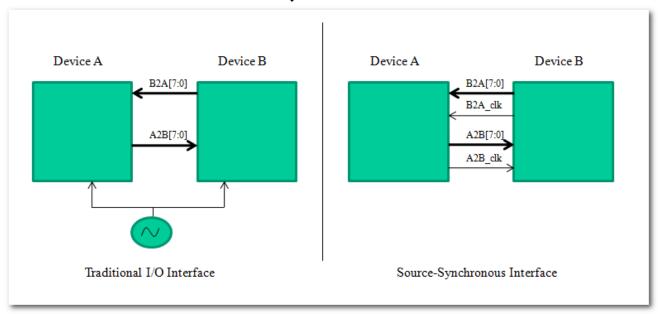

Traditional I/O interfaces consist of a board-level clock that feeds two devices, and those devices send data back and forth. A source-synchronous interface sends a clock with its data:

A source-synchronous interface may only pass data in one direction, such as when interfacing with an ADC or DAC. Note that I did not draw the clock sources in the source-synchronous interface because there are multiple topologies. They could be driven by the same external clock, they might be driven by independent clocks, the Device A may have a clock driver and Device B just uses A2B\_clk, etc.

Source-synchronous interfaces can be quite messy because they send a new clock domain with the data, which often needs to be passed back to the device's core clock domain. That often

requires a FIFO to take care of any differences in clock phase, and if the clock rates are not matched exactly, could even require some sort of rate-match FIFO. So why do designs use source-synchronous interfaces? The major reason is that they can run considerably faster than traditional I/O interfaces. Why?

Devices vary considerably over PVT(Process, Voltage and Temperature). As a quick guesstimate, I usually say that delays can vary by 2x across PVT. So in the traditional I/O example above, if Device A's Tco was a worst case of 6ns, it might also be as fast as 3ns. There is no way to control this, and hence we state that it varies by 3ns. That comes directly out of our margin. In the source-synchronous interface, the data from a device still might have a Tco that varies by 3ns, but the clock is routed alongside it, and so it will also vary in-step with the data.

## The Key to Source-Synchronous Performance

We just stated that source-synchronous interfaces achieve high performance by making sure the clock and data travel along similar paths, and hence their delays will track each other over PVT. Most users are aware of this, but there is one key point that is often over-looked. For a given interface:

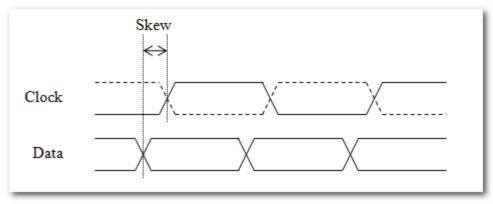

If the clk and data delays are identical, then the clock edge and data edge arrive at the Receiver's register at the exact same time. Having the clock and data change at the same time is the worst possible scenario. What we really want is the clock to change in the middle of the data eye, so that the data is stable for as long before and after the clock edge as possible.

How is this done? Basically, all source synchronous interfaces need a way to shift the clock into the middle of the data eye, and the shift must occur in a way that does not vary over PVT. For SDR(Single-Data Rate Interfaces), this is easy. Inverting the clock will put the rising edge right into the middle of the data eye. If the clock does not have a 50/50 duty cycle, then a PLL can be used to shift the clock 180 degrees. For DDR(Double-Data Rate Interfaces), there needs to be a PLL that shifts the clock 90 degrees, in order to put it in the middle of the data eye.

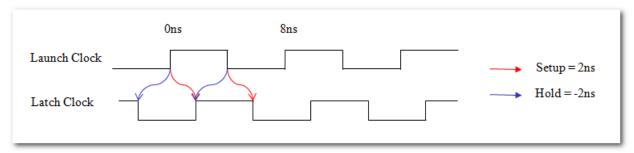

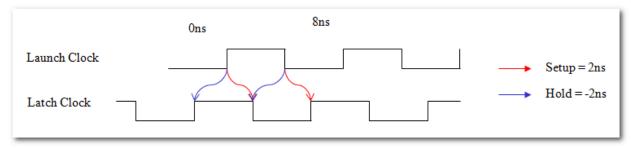

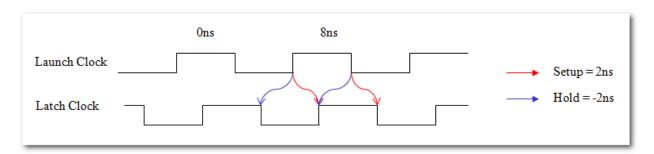

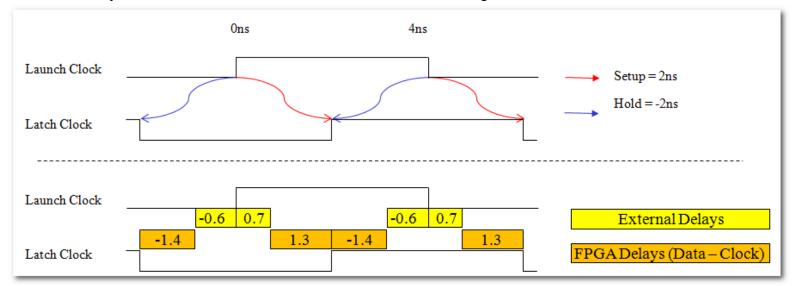

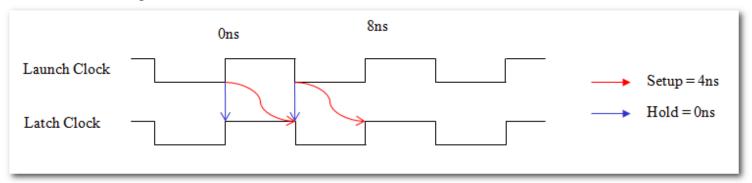

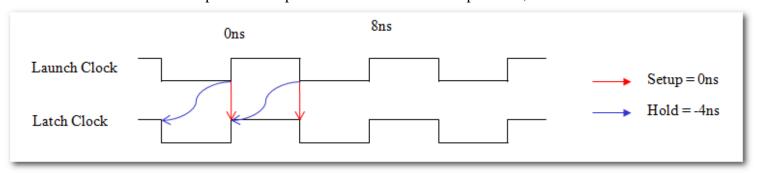

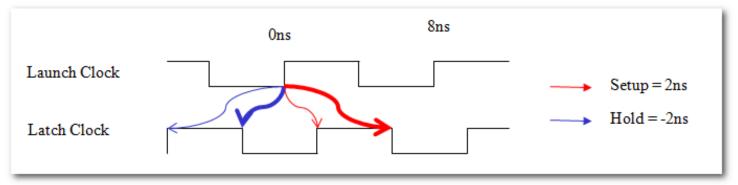

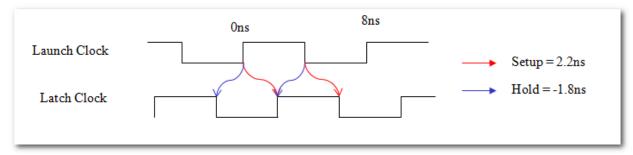

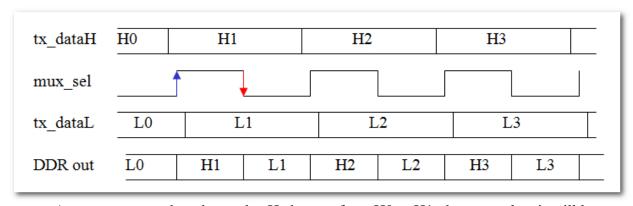

Once the clock is phase-shifted and centered in the middle of the data eye, we get a clock relationship like so:

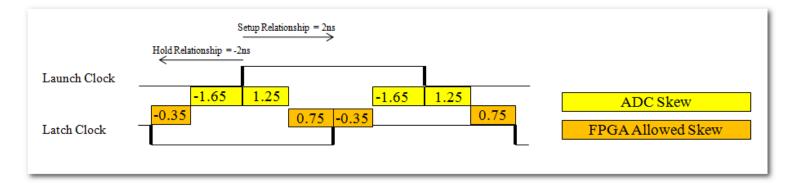

This waveform shows an 8ns clock running a DDR interface. I will use this for all the upcoming examples. Although the clock is 125MHz, the data rate is 250Mbps because it transfers on both edges. This means the window is 4ns. In the waveform, there is a 90 degree phase-shift on the Latch Clock, which results in a 2ns setup relationship and -2ns hold relationship. These relationships are valid for when the rising edge sends data and the falling edge sends data, as shown by both sets of arrows.

For now we are going to concentrate on DDR interfaces, since they are the most common, but later on will discuss <a href="SDR(Single Data Rate">SDR(Single Data Rate</a>) examples.

Note that this waveform does not specify if the FPGA is the transmitter or the receiver. That is fine since TimeQuest analyzes the entire I/O interface, and hence the clock relationships will look like this when the FPGA is the transmitter and when it's the receiver. It also does not specify which device is phase-shifting the clock, the transmitter or the receiver. That is also fine, since the clock relationship is the same either way.

## I/O Timing Basics

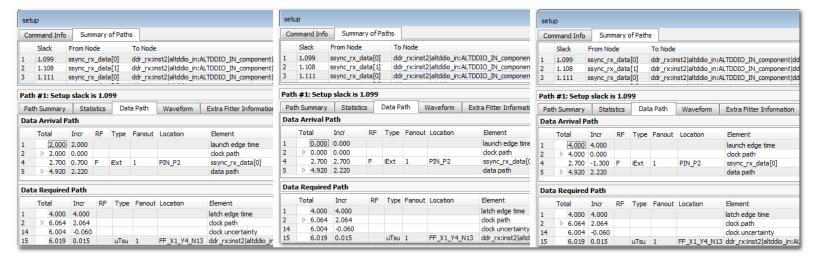

When doing setup analysis on an I/O path, there are only two relevant numbers that come from the .sdc. One is the setup relationship, and the other is the external delay. The setup relationship will be shown in the timing report summary, and is also shown as the difference between the launch edge and latch edge. The other number is external delay, which will be iExt or oExt. The following setup report screenshot shows an example, where the top right box is the setup relationship, with arrows pointing to the launch and latch times used in the equation, and the other box shows the external delay of 0.7ns, iExt.

| set | un.         |                                      |            |                     |                |                  |                                                   |                                       |                   |                   |                  |

|-----|-------------|--------------------------------------|------------|---------------------|----------------|------------------|---------------------------------------------------|---------------------------------------|-------------------|-------------------|------------------|

|     | •           | _                                    |            |                     |                |                  |                                                   |                                       |                   |                   |                  |

| Co  | mmand Info  | Summary of                           | of Paths   |                     |                |                  |                                                   |                                       |                   |                   |                  |

|     | Slack       | Slack From Node To Node              |            | Lau                 | Launch Clock L |                  | Latch Clock                                       |                                       | Clock Skew        | Data Delay        |                  |

| 1   | 1.099       | ssync_rx_data                        | [0] ddr r: | ddr_rx:inscell_l[0] |                | nc_dk_ext        | inst1 altpll_component auto_generated pll1 clk[0] |                                       | 2.000             | 2.064             | 2.220            |

| 2   |             | ssync_rx_data                        |            | x:inscell_l         |                | nc_dk_ext        |                                                   | component auto_generated pll1 clkfor  | 2.000             | 2.062             | 2.209            |

| 3   | 1.111       | ssync_rx_data[0] ddr_rx:inscell_h[0] |            |                     | h[0] ssy       | nc_dk_ext        | inst1 altpl                                       | _component auto_generated pll1 clk[0] | 2.000             | 2.072             | 2.216            |

| Pat | h #1: Setup | slack is 1.09                        | 99         |                     |                |                  |                                                   |                                       |                   |                   |                  |

| Pa  | th Summary  | Statistics                           | Data Path  | Wavefo              | orm E          | xtra Fitter Info | rmation                                           |                                       |                   |                   |                  |

| Dat | a Arrival P | ath                                  |            |                     |                |                  |                                                   |                                       |                   |                   |                  |

|     | Total       | Incr                                 | DP         | Type F              | Fanout         | Location         |                                                   | Element                               |                   |                   |                  |

| 1   | 4.000       | 4.000                                | _          |                     |                |                  |                                                   | launch edge time                      |                   |                   |                  |

| 2   | 4.000       | 0.000                                |            |                     |                |                  |                                                   | clock path                            |                   |                   |                  |

| 3   | 4.0         | 0.000                                | F          |                     |                |                  |                                                   | clock network delay                   |                   |                   |                  |

| 4   | 4.700       | 0.700                                | F          | iExt 1              |                | PIN_P2           |                                                   | ssync_rx_data[0]                      |                   |                   |                  |

| 5   | ▷ 6.920     | 2,220                                |            | $\overline{}$       |                |                  |                                                   | data path                             |                   |                   |                  |

| Dat | a Required  | Path                                 |            |                     |                |                  |                                                   |                                       |                   |                   |                  |

|     | Total       | Incr                                 | RF         | Type F              | anout          | Location         |                                                   | Element                               |                   |                   |                  |

| 1   | 6.000       | 6.000                                |            |                     |                |                  |                                                   | latch edge time                       |                   |                   |                  |

| 2   | ▶ 8.064     | 2.064                                |            |                     |                |                  |                                                   | clock path                            |                   |                   |                  |

| 14  | 8.004       | -0.060                               |            |                     |                |                  |                                                   | clock uncertainty                     |                   |                   |                  |

| 15  | 8.019       | 0.015                                |            | uTsu 1              | 1              | FF_X1_Y4_N       | 13                                                | ddr_rx:inst2 altddio_in:ALTDDIO_IN_co | mponent ddio_in_6 | 6gf:auto_generate | d input_cell_l[0 |

It's important to remember that all of your .sdc constraints will boil down to these two numbers. Everything else in the analysis is based on the FPGA's place-and-route and can be completely ignored until these two numbers are correct, because the place-and-route results do not matter until the constraints are correct.

The hold analysis of a path similarly has a Hold Relationship and iExt or oExt delay. If things get confusing, always run report timing and look at those two numbers.

Where do those numbers come from? The setup and hold relationship comes from your clock constraints. This is all discussed in the TimeQuest User Guide. The iExt and oExt values come directly from the set\_input\_delay and set\_output\_delay constraints. If a design has "set\_input\_delay -max 1.2...." and "set\_input\_delay -min 0.3..." applied to a port, then the iExt during setup analysis will be 1.2 and the iExt for hold analysis will be 0.3. The same goes for output ports, whereby a "set\_output\_delay -max 1.4..." will create an oExt of 1.4 and "set\_output\_delay -min 0.5..." will create an oExt of 0.5 during hold analysis. (Note that the oExt values show up in the Data Required Path, and are therefore negated). But it's important to see how these two numbers are used during analysis. Let's look at two straightforward equations:

Setup Analysis:

FPGA\_Data\_Delay - FPGA\_Clock\_Delay < Setup\_Relationship - External\_Delay\_Max Hold Analysis:

$FPGA\_Data\_Delay - FPGA\_Clock\_Delay > Hold\_Relationship - External\_Delay\_Min$

Note that the numbers on the right come out of the .sdc, and the numbers on the left come out of place and route. So if you're ever unsure what you're telling the FPGA to do, run "report\_timing –setup..." and "report\_timing –hold..." on your I/O port and pull out the four numbers on the right, Setup Relationship, iExt/oExt max, Hold Relationship and iExt/oExt min.

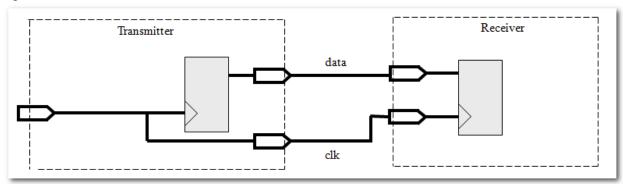

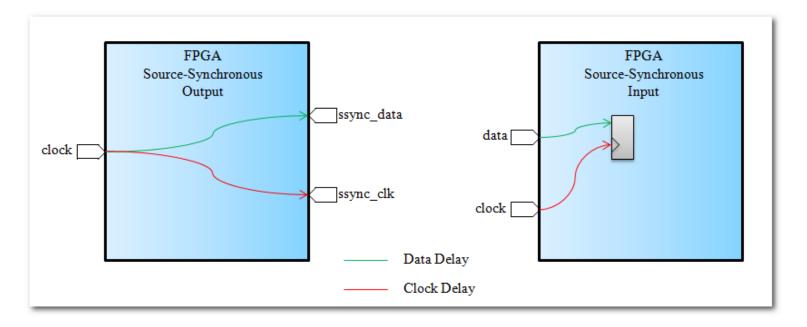

And to help visualize what the "FPGA Data Delay" and "FPGA Clock Delay" are:

This is generalized drawing, but for the output, (FPGA\_Data\_Delay – FPGA\_Clock\_Delay) is just how much longer it takes the data to come out compared to the clock coming out. Likewise for the input, this just compares how much longer the data takes to get to the register compared to the clock reaching the register. (For DDR, the input would naturally drive two registers.)

So let's do a real simple example. Let's look at an output port and assume the .sdc constrains it like so:

```

Setup Relationship = 2ns

Hold Relationship = -2ns

oExt Max = 0.8ns

oExt Min = -0.5ns

```

Our equations above would boil down to:

$$FPGA\_Data\_Delay - FPGA\_Clock\_Delay < 2 - 0.8$$

$FPGA\_Data\_Delay - FPGA\_Clock\_Delay > -2 - (-0.5)$

Or:

So what are we saying? The ssync\_data can come out of the FPGA anywhere between 1.2ns after the ssync\_clk to 1.5ns before the ssync\_clk.

Why go through this exercise? The main reason is to understand that there are 2 variables for setup analysis and 2 variables for hold analysis that come out of the user's constraints, and to see exactly how they constrain the FPGA. I find we often get too wrapped up

in high-level analysis that we forget that all this can be boiled down to a straightforward equation. So now that we've simplified it, let's complicate things a bit...

## Intro to Two Methods: Explicit and Implicit Clock Shift

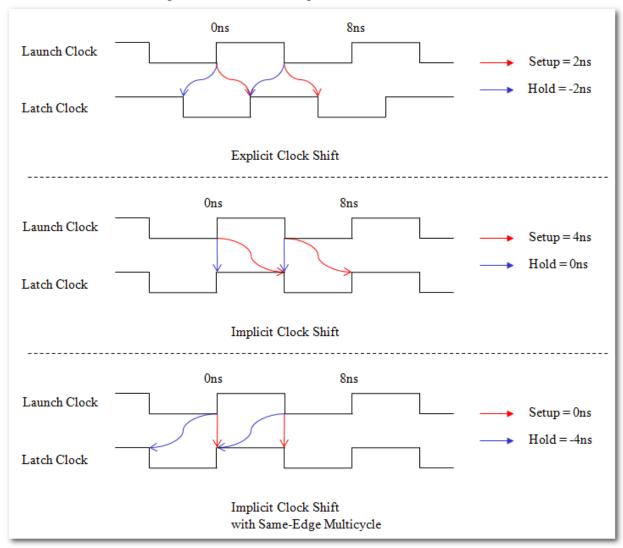

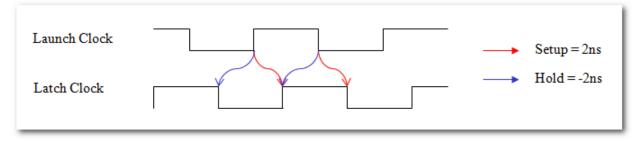

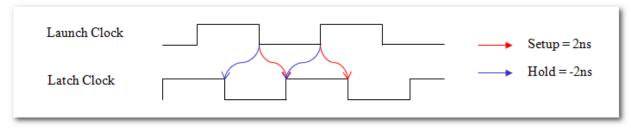

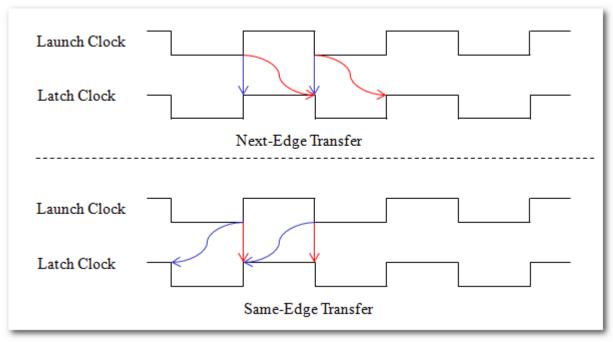

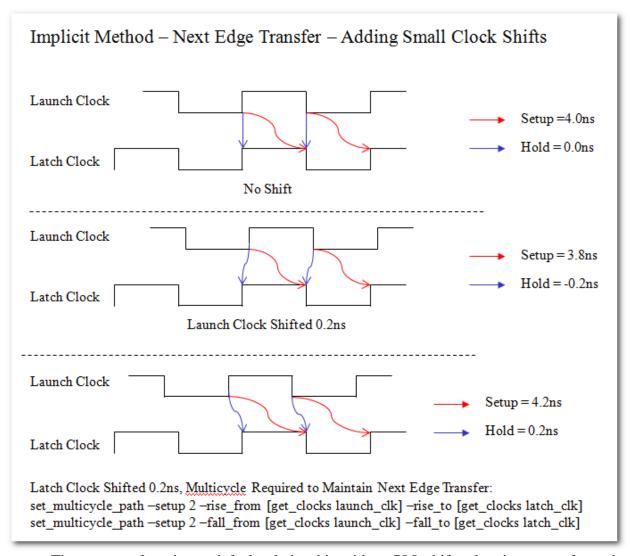

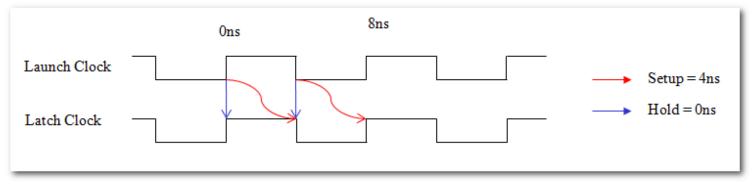

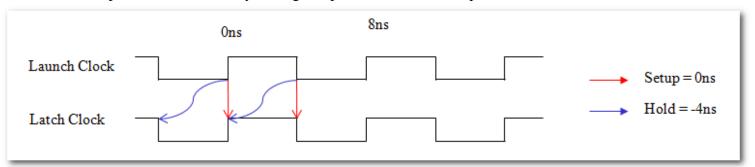

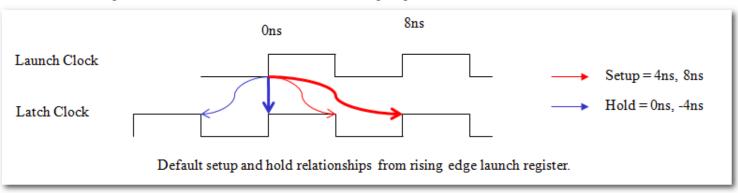

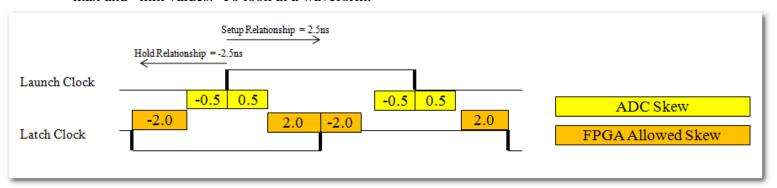

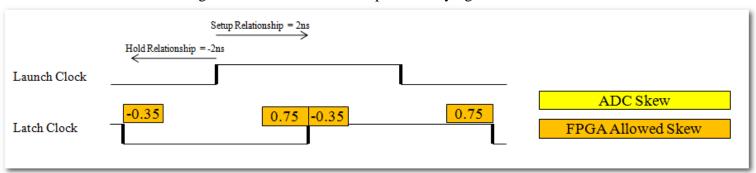

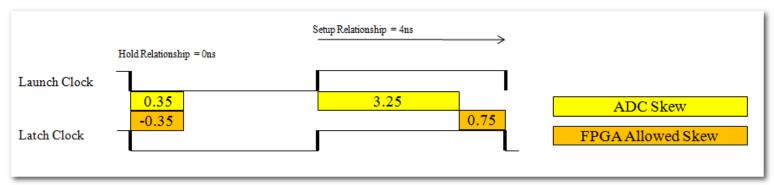

Before diving into details and examples, I want to show two major ways to analyze source-synchronous interfaces. The following examples will be DDR and have an 8ns clock period, which equates to a 4ns data window, or 250Mbps interface. Let's look at three waveforms with their setup and hold relationships, and the difference should be clear:

As mentioned, the key to getting good performance in a source-synchronous interface is that there is a clock shift to center its edge in the middle of the data window. The Explicit Clock Shift Method sets up our clocks to do that, creating a nice symmetric setup and hold relationship. The next two waveforms show the Implicit Clock Shift, or more exactly, they don't show any clock shift at all. Instead they show edge-aligned waveforms, which then gives the user the

option to send data to the next latch edge(default analysis) or to the same edge it was launched from, which is done with multicycles.

So why is it implicit and why have three ways at all? The answer comes from looking at the setup relationship when interfacing to three different devices:

```

Device #1: FPGA_Data_Delay - FPGA_Clock_Delay < 2 - 0.8

Device #2: FPGA_Data_Delay - FPGA_Clock_Delay < 4 - 2.8

Device #3: FPGA_Data_Delay - FPGA_Clock_Delay < 0 - (-1.2)

```

What you see are three different setup relationship based on the waveforms above, along with three different external delays. The net result is that the three different methods constrain the FPGA the same way. Two variables allow the user to constrain the FPGA the same way, yet with different external variables. Why would anyone want to do that? They probably wouldn't, but external devices spec themselves in different ways, and this allows some powerful flexibility to follow these different methods.

Personally, I prefer using the explicit method and think most designers could learn that one only and never have problems. That being said, there are certainly cases where the implicit method "falls out" of the external device's specs and can be much easier. External device datasheets will be examined in Section VI.

For a quick rule-of-thumb:

- Anytime the FPGA is phase-shifting the clock, that is an explicit shift and the Explicit Method should be used, specifically Case 1 where the FPGA is the receiver and Case 3 where the FPGA is the transmitter.

- If the FPGA is not phase-shifting the device, then the external device is. The user now has options on how to constrain this, which can be looked at based on how they want to describe the external delays. Let's look at an 8ns clock, so a 90 degree shift is 2ns, and say the data varies around that by +/-500ps:

- The explicit method would explicitly phase-shift the external clock and the external –max and –min values would center around 0 degrees, such as 0.5ns and -0.5ns.

- The implicit method with next-edge transfers would be used if the external

-max and -min delays were centered around 90 degrees, such as 2.5ns and

1.5ns.

- The implicit method with same-edge transfers would be used if the external max and –min delays were centered around -90 degrees, such as -1.5ns and -2.5ns.

Note: For all of these, they don't have to be centered exactly. A max value of 2.7 and min of 1.7, which would center around 2.2ns instead of 2ns, would still be constrained with the next-edge transfer Implicit Method.

- The last option is when there <u>really is no phase-shift anywhere in the system</u>.

## Section II: The Explicit Clock Shift Method

I call this the Explicit Clock Method because the clock constraints are explicitly set up to say there is a clock shift in the interface. That does not mean the FPGA has to phase-shift the

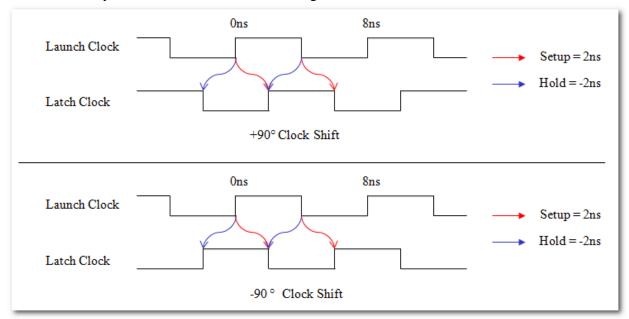

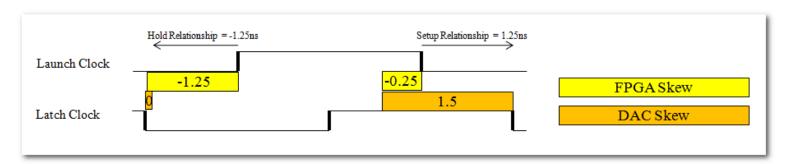

clock, as they external device might be shifting the clock. This method is flexible in that, whether the FPGA is the transmitter or receiver, or whether it shifts the clock or not, the waveform always looks like one of the following:

The top waveform has 90 degree phase-shift on the Latch clock, while the bottom waveform has a -90 degree phase-shift. Since they result in the same setup and hold analysis, the timing analysis will be the same. I will mainly show a +90 degree shift, and just note that it equally applies to a -90 degree shift.

There are two questions the user must ask before getting started, "Is the FPGA receiving or transmitting data?" and "Is the FPGA phase-shifting the clock?" This results in four cases:

Case 1: The FPGA is the receiver and phase-shifts the clock

Case 2: The FPGA is the receiver and does not phase-shift the clock.

Case 3: The FPGA is the transmitter and phase-shifts the clock.

Case 4: The FPGA is the transmitter and does not phase-shift the clock.

It should be easy to tell if the FPGA is the receiver or transmitter. If both devices are FPGAs, please look at the <u>section FPGA to FPGA Interfaces</u> after completing this section.

The second question is if the FPGA phase-shifts the clock or not. The user needs to determine this up front, not just for entering timing constraints, but for actually creating the design, since the phase-shift must be manually entered into the PLL megafunction.

All Quartus II projects can be found in the file Source\_Synchronous\_Projects.zip. Each top-level file is a .bdf schematic for easy understanding, but they can be converted to VHDL or Verilog by opening the file in Quartus II and going to File -> Create HDL Design File.

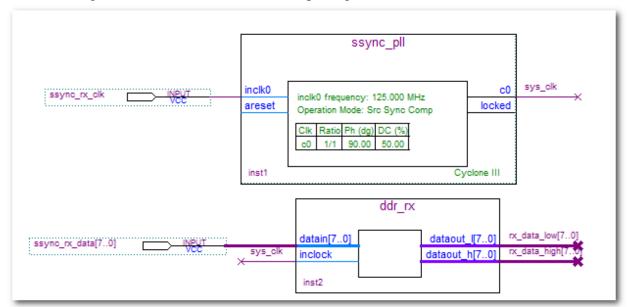

## Case 1: The FPGA is the receiver and phase-shifts the clock

This design is nothing more than a PLL that takes the source-synchronous clock, phase-shifts it 90 degrees, and then drives the DDR input registers:

An important note is that the PLL is put into Source Synchronous compensation mode. This ensures that the PLL's compensation is ideal for having the clock delay match the data delay. This should give optimum timing margin. Once this is done, the clocks constraints are created like so:

```

create_clock -period 8.0 -name ssync_clk [get_ports ssync_rx_clk] derive_pll_clocks create clock -period 8.0 -name ssync_clk ext

```

The first create\_clock just puts an 8ns constraint on the clock coming in. The derive\_pll\_clocks will constrain the output of the PLL, which has a 90 degree phase-shift, and is what centers the clock onto the data eye. The final create\_clock generates a virtual clock that represents the clock driving the external registers. Yes, it is identical to the first clock, but it is good practice to differentiate between the two.

That's it. The clocks are now constrained and there is a phase-shift in the interface, being done internally by the FPGA's PLL.

## Case 2: The FPGA is the receiver and does not phase-shift the clock

Case 2 is very similar to case 1. The PLL is still put into Source Synchronous compensation mode. The only difference is that its output does not do a 90 degree phase-shift.

The SDC constraints are also similar except the clock coming into the FPGA has been shifted 90 degrees:.

```

create_clock -period 8.0 -name ssync_clk [get_ports ssync_rx_clk] —waveform {2.0 6.0} derive_pll_clocks create clock -period 8.0 -name ssync_clk_ext

```

The –waveform option specifies where the first rising edge and the next falling edge occur after time 0. Note that phase-shifting the clock coming into the FPGA only affects its relationship to other clock domains, specifically to the external, non-shifted virtual clock. Anything inside the FPGA will have both its source and destination shifted and the shift will cancel out. What we're saying is that the external device shifts the clock 90 degrees before sending it into the FPGA, which center-aligns it onto the data.

Users sometimes protest this by stating they don't know if the external device is phase-shifting the clock or not. They will look through the datasheet and not see it anywhere. The important point is not what the external device is doing explicitly, but what this tells the FPGA. This clock relationship says the clock has already been center-aligned onto the data, and so the FPGA's goal is to maintain that relationship to the latching registers by making sure the clock and data delays match. Thinking in terms of what the FPGA is being told to do often alleviates that concern.

Although shifting the clock coming into the FPGA does not affect internal timing, some users don't feel comfortable with this approach, so I will mention two other solutions where the external clock is phase-shifted and produce the same affect. If you're not sure, use the original clock relationships and don't worry about these two other options, as they basically create the same analysis in the end.

#### Option 2:

This option entails phase-shifting the launch clock 90 degrees instead of the latch clock:

```

create_clock -period 8.0 -name ssync_clk [get_ports ssync_rx_clk]

derive_pll_clocks

create_clock -period 8.0 -name ssync_clk_ext _waveform {2.0 6.0}

```

This results in a waveform like so:

The setup and hold relationship are still +/-90 degrees. The only difference is the edges being used, so the critical setup analyses are rising edge -> falling edge and falling edge -> rising edge, while the hold analyses are from rising edge -> rising edge and falling edge -> falling edge. This is the opposite of what happens when the latch clock is shifted +90 degrees, but due to symmetries in the relationship, generally has no affect. This is discussed in more detail in the section comparing different edge transfers, but the net sum is that it generally makes no difference.

#### **Option 3:**

If the user wants the same edge relationships as the original but does not want to shift the clock coming into the FPGA, a third option is to phase-shift the launch clock 270 degrees.

```

create_clock -period 8.0 -name ssync_clk [get_ports ssync_rx_clk]

derive_pll_clocks

create_clock -period 8.0 -name ssync_clk_ext _waveform {6.0 10.0}

```

The –waveform option does not allow for negative numbers, but doing a 270 degree phase-shift is identical to doing a -90 phase-shift, as far as relationships to other clocks. This is discussed in the TimeQuest User Guide's section on Periodicity. The waveform looks like so:

The setup and hold relationships are still +/- 90 degrees, and the edges used for setup analysis and hold analysis are the same as when the latch clock is shifted 90 degrees. This is just another option that will give identical slacks as the original option, but has a shift on the external clock instead of the one coming into the FPGA.

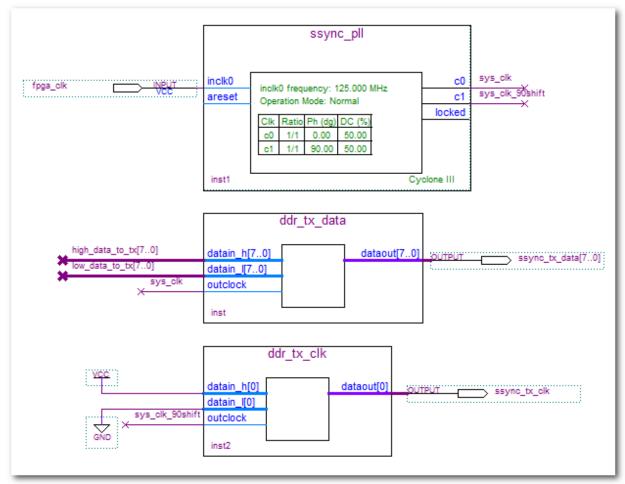

## Case 3: FPGA is the transmitter and phase-shifts its clock

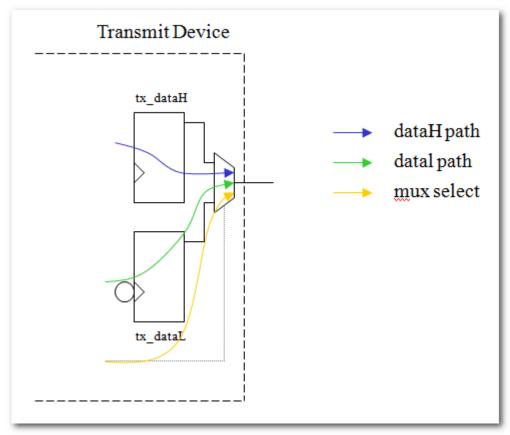

When transmitting, the user sends the clock and data out through the altddio megafunction:

For Case 3, a second PLL tap is being used to phase-shift the clock 90 degrees. Note that this design uses an altddio\_out megafunction for the clock output, and just ties off the ports to VCC and GND. This is not required, but common practice in source synchronous circuits in that it makes the clock path mimic the data path more closely. It also prevents the fitter from sending the clock out the dedicated PLL clock output path, which is not good for source-synchronous timing, since it has considerably different timing than the data output paths.

The clock constraints in the .sdc look like so:

create\_clock -period 8.0 -name fpga\_clk [get\_ports fpga\_clk]

derive\_pll\_clocks

create\_generated\_clock -source [get\_pins {inst1|altpll\_component|auto\_generated|pll1|clk[1]}] -name

ssync tx clk ext [get\_ports {ssync tx clk}]

The first two constraints are pretty straightforward. They constrain the clock coming into the FPGA and then call derive\_pll\_clocks to constrain the PLL's outputs. The third constraint puts a generated clock on the output port  $ssync\_tx\_clk$  that sends out the clock, so that it can be used as a clock for our external registers. The –source of the clock is the output of the PLL that

drives this port. I usually get the name by running Report Clocks in TimeQuest and finding the Target of the PLL clock after they've been constrained by derive\_pll\_clocks. This returns a name with only the instances, which makes it shorter. It's also possible to use the PLL name under the Global Resources section of the Fitter Report. This uses the whole entity:instance nomenclature, which looks like so:

```

create_generated_clock -source [get_pins

{ssync_pll:inst1|altpll:altpll_component|ssync_pll_altpll:auto_generated|wire_pll1_clk[1]}] -name

ssync_tx_clk_ext [get_ports {ssync_tx_clk}]

```

As you can see, the name after –source is longer due to the entity/module name being used in each hierarchy(shown in red). This refers to the same PLL tap and either can be used in TimeQuest.

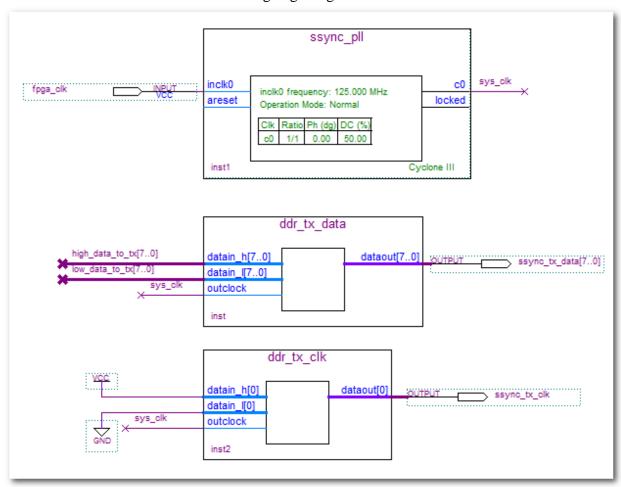

#### Case 4: FPGA is the transmitter and sends a non-shifted clock

This design is very similar to Case 3 except the PLL only has one output that drives both the data and clock so that it is transmitting edge-aligned:

In reality, this design does not need a PLL at all, as it's not really doing anything for the interface. I left it in since most designs will have the transmit domain on a PLL for other

reasons, and the generated clock on the clock output will have to use the PLL for its –source option.

The .sdc constraints look like so:

```

create_clock -period 8.0 -name fpga_clk [get_ports fpga_clk]

derive_pll_clocks

create_generated_clock -source {inst1|altpll_component|auto_generated|pll1|clk[1]} -name

ssync_tx_clk_ext [get_ports {ssync_tx_clk}] -phase 90

```

Most of this is pretty straightforward. The generated clock is applied to the output port sending the source synchronous clock off chip and using the PLL as its source. The difference from Case 3 is that this generated clock has added "-phase 90".

Does this –phase do anything to the clock inside the FPGA? No. What this option does is state that the clock being sent off chip will be phase-shifted externally, at the receiver. (I think it would have made more sense to not have a the –phase 90, and instead create a virtual generated clock sourced from this clock going off chip, and put the –phase 90 on this external clock. It is not legal to have virtual generated clocks though, so I have done it this way. The end result is identical.)

So the –phase 90 explicitly does nothing to the clock being sent off chip. What it implicitly does is say the external device receiving the data phase-shifts the clock to center it onto the data eye. Knowing the external device does the phase-shift, Quartus II will try to match clock and data delays going off-chip, sending them out edge-aligned.

## External Delays of the Explicit Method

Now that we've set up our clocks to show that there is a phase-shift in the system, we need to apply constraints to the data ports. The designer has already decided if the FPGA is phase-shifting the clock or not, and these external delays will be used to determine how much skew there can be between the data arrival path and data required path, i.e. between the data path and the clock path.

For example, when the FPGA is the transmitter, the user will be able to easily say, the data output can leave the FPGA  $\pm$ 00ps relative to the clock output. This method allows this to be done independently of the phase-shift. So if the FPGA is not phase-shifting the output clock(Case 4), then the data would leave edge-aligned  $\pm$ 00ps relative to the clock. If the FPGA is phase-shifting the clock going off-chip, then the data would still constrained to be  $\pm$ 00ps, but the clock would have a 90 degree offset.

It's very nice to be able to separate the data skew from the clock's phase-shift, as long as you remember it. Cases 2 and 4 are where the FPGA does not phase-shift the clock, and so the skew between data and clock will reflect the physical differences in the FPGA. Cases 1 and 3 will have an additional phase-shift of the clock on top of the skew constraints we are about to enter.

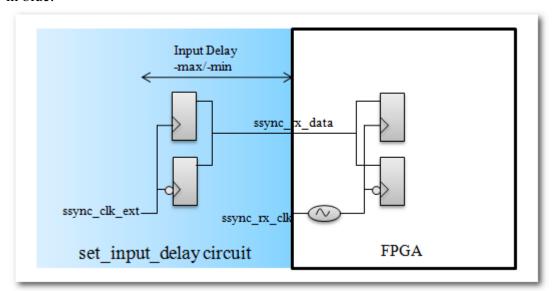

For Case 1 and Case 2, where the FPGA is the receiver, the constraints look like so:

```

set_input_delay -clock ssync_clk_ext -max 0.0 [get_ports {ssync_rx_data[*]}]

set_input_delay -clock ssync_clk_ext -min 0.0 [get_ports {ssync_rx_data[*]}]

set_input_delay -clock ssync_clk_ext -max 0.0 [get_ports {ssync_rx_data[*]}] -clock_fall -add_delay

```

set\_input\_delay -clock ssync\_clk\_ext -min 0.0 [get\_ports {ssync\_rx\_data[\*]}] -clock\_fall -add\_delay

Note that the -max and -min values are 0.0, which is just a placeholder for now. The first two constraints state that there is an external register clocked by ssync\_clk\_ext that drives data to the FPGA's ssync\_rx\_data ports. The last two constraints use the -add\_delay to state that there is a second register driving these ports, and -clock\_fall states that this second register is clocked on the falling edge of ssync\_clk\_ext. The circuit described is outside the FPGA, shown in blue:

This covers both Case 1 and Case 2.

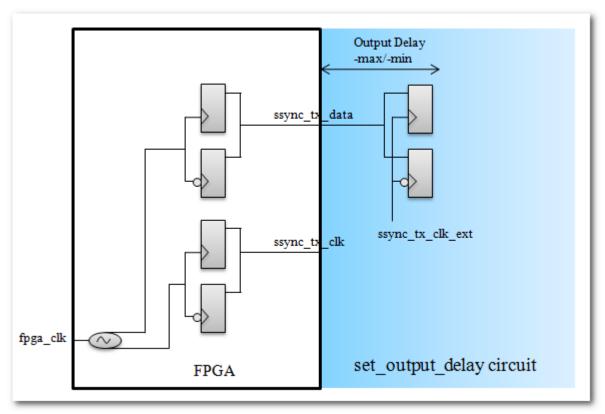

For outputs, the constraints look very similar. Once again, the –max and –min values are filled in with 0.0 as a place-holder:

```

set_output_delay -clock ssync_tx_clk_ext -max 0.0 [get_ports {ssync_tx_data[*]}] set_output_delay -clock ssync_tx_clk_ext -min 0.0 [get_ports {ssync_tx_data[*]}] set_output_delay -clock ssync_tx_clk_ext -max 0.0 [get_ports {ssync_tx_data[*]}] -clock_fall -add_delay set_output_delay -clock ssync_tx_clk_ext -min 0.0 [get_ports {ssync_tx_data[*]}] -clock_fall -add_delay

```

The first two constraints say the output ports ssync\_tx\_data[\*] drive an external register clocked by ssync\_tx\_clk\_ext. The last two constraints use the -add\_delay to say there is a second external register, and the -clock\_fall option says this register is clocked on the falling edge of ssync\_tx\_clk\_ext. This results in the external circuit in blue:

Note that Case 3 has the FPGA's output port *ssync\_tx\_clk* driven by a phase-shifted tap of the PLL, while Case 4 has both the data and clock outputs driven by the same tap. The set\_output\_delay constraints do not care, as they are describing what occurs outside the FPGA.

Now that we've created our external circuit, it's time to determine what the external – max and –min values should be.

## **FPGA-Centric versus System-Centric**

First off, I wanted to touch on the term FPGA-centric constraints, which tell the FPGA what to do, and System-Centric Constraints, which describe what is going on outside the FPGA. Although this concept can be useful they are also a bit misleading. The constraints set\_input\_delay and set\_output\_delay ALWAYS describe what is going on outside the FPGA, and are hence system-centric. That being said, once you state the external delays, you are also ALWAYS constraining the FPGA, and I believe the user should know how they're constraining the FPGA. So rather than thinking purely in terms of system-centric or FPGA-centric, they really should be thinking of both.

The point I believe that is often overlooked is that the system has a setup relationship and hold relationship, which is how the interface meets timing. Part of that relationship will be used by the external delays and part will be used by the FPGA. So when one side is constrained, so is the other. For example, if the setup relationship to an output port is 10ns, then the interface has 10ns to work with. By putting a "set\_output\_delay –max 3" on the output port, they are stating the external delay is 3ns, but they're also stating the FPGA has 7ns to work with. When the user knows the setup and hold relationships, it's easy to see how FPGA-Centric versus System-Centric constraints are really just different sides of the same coin.

I am going to concentrate on the FPGA side for the following discussion, since the user should always know what they're telling the FPGA to do. For example, if the user knows their external receiver has a Tsu of 3ns, they might put in "set\_output\_delay –max 3". If the setup relationship is 3.5ns, then they're giving the FPGA 500ps to work with, but if the setup relationship is 20ns, then they're giving the FPGA 17ns to work with, which is obviously a big difference. By knowing the setup relationship and hold relationship, as soon as the user says how much of that margin is being used externally, they will know how much they're leaving for the FPGA.

Luckily, the whole premise of the Explicit Clock Shift Method is that the clocks have a 90 degree phase-shift, and hence the setup relationship is +90 degrees and the hold relationship is -90 degrees, and just by knowing the clock period, we know the setup relationship and hold relationship. For example, if the clock period is 8ns, then 90 degrees is 2ns. If the external – max delay is 0.9ns, then the user is saying the FPGA's data path can be no more than 1.1ns longer than the clock path. Likewise, if the external –min delay is -0.9ns, then the FPGA's data path can be no less than 1.1ns shorter than the clock path. This is true whether we're constraining inputs or outputs.

#### Case 1 and Case 2: FPGA is the Receiver

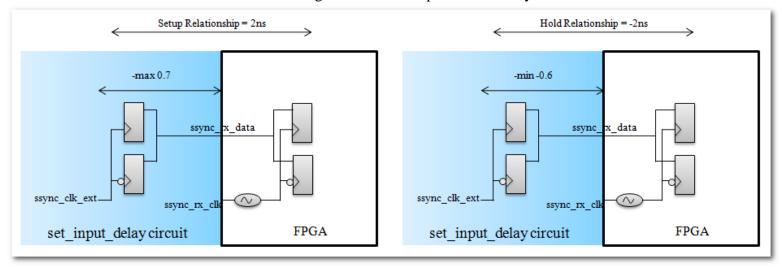

Let's look at an example set of input constraints, where I have made-up max/min values:

```

set_input_delay -clock ssync_clk_ext -max 0.7 [get_ports {ssync_rx_data[*]}] set_input_delay -clock ssync_clk_ext -min -0.6 [get_ports {ssync_rx_data[*]}] set_input_delay -clock ssync_clk_ext -max 0.7 [get_ports {ssync_rx_data[*]}] -clock_fall -add_delay set_input_delay -clock ssync_clk_ext -min -0.6 [get_ports {ssync_rx_data[*]}] -clock_fall -add_delay

```

This translates to the following circuits for setup and hold analysis:

Looking at the setup analysis on the left, the relationship between the launch clock and latch clock is 2ns. The external –max delay is 0.7ns. That leaves 1.3ns for the FPGA. That means inside the FPGA, the data delay to the register can be 1.3ns longer than the clock delay and it will still meet timing. On the right side, the hold relationship is -2ns, and the external

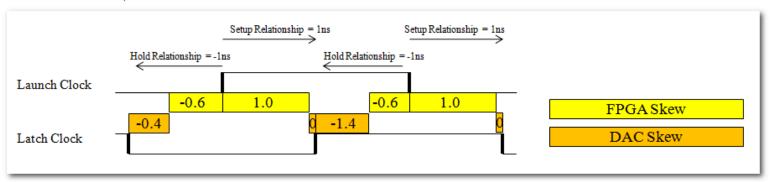

delay is -0.6ns. That means the data delay inside the FPGA can be 1.4ns shorter than the clock delay and it will still meet timing. In the upcoming <u>report\_timing section</u>, we will see this analysis. Now let's look at a waveform to show the same thing:

The top waveform shows our setup and hold relationships. The bottom waveform shows them superimposed with actual delays. The yellow bars show the external device may skew its data in relation to its clock by +0.7ns to -0.6ns. That leaves the FPGA with +1.3ns and -1.4ns to work with and still meet timing.

Using equations:

In the Explicit Method, the setup relationship is 90 degrees and the hold relationship is - 90 degrees. Using the external delays of 0.7 and -0.6, we get:

One point that has been mentioned before but worth bringing up again, is that we're looking at FPGA skew before analyzing the PLL shift. So in Case 2, where we say the clockshift occurs externally and therefore clock/data come into the FPGA center-aligned with the data, the clock and data paths will try to maintain that relationship by staying within the required 1.3/1.4 requirements. Case 1 does the same thing in trying to match the data and clock delays inside the FPGA, but since the clock/data come in edge-aligned, there is an additional 90 degree phase-shift that centers the clock into the middle of the data eye. This is very important not to forget, and easiest to think of skew and phase-shift as two separate things.

#### Case 3 and Case 4: FPGA is the Transmitter

Let's look at the sample output constraints, with made-up max/min values:

```

set_output_delay -clock ssync_tx_clk_ext -max 1.2 [get_ports {ssync_tx_data[*]}] set_output_delay -clock ssync_tx_clk_ext -min -1.1 [get_ports {ssync_tx_data[*]}] set_output_delay -clock ssync_tx_clk_ext -max 1.2 [get_ports {ssync_tx_data[*]}] -clock_fall -add_delay set_output_delay -clock ssync_tx_clk_ext -min -1.1 [get_ports {ssync_tx_data[*]}] -clock_fall -add_delay

```

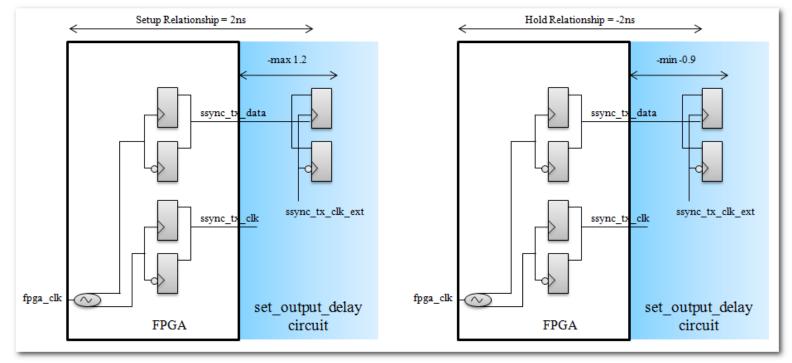

This translates to the following circuits for setup and hold analysis:

Looking at the setup analysis on the left, the setup relationship from fpga\_clk to ssync\_tx\_clk\_ext is 2ns. The -max external delay is 1.2ns, leaving 0.8ns for the FPGA to deal with. That means the FPGA's data can come out up to 0.8ns later than the clock comes out and the interface will still make timing. Likewise on the right side, the hold relationship is -2ns, and the external -min delay is -1.1ns, which means the data can come out of the FPGA up to 0.9ns before the clock and the interface will still meet timing.

Once again, the question of whether or not the FPGA phase-shifts the output clock is another layer on top of these requirements. For example, if the above constraints were in Case 4, where the FPGA does not phase-shift the output clock, the data output would be constrained within +0.8ns and -0.9ns to the clock output, and hence would be edge-aligned. If the above were used in Case 3, the same would hold true except there would be an additional 90 degree shift on the output clock, making it a center-aligned output. The Explicit Method allows the PLL phase-shift and the data skew to be analyzed separately. And of course the difference between Case 3 and Case 4 is not just how the .sdc constraints are set up. Case 3 physically uses another tap of the PLL with a 90 degree phase-shift to drive the output clock.

## Benefits of the Explicit Method

There are multiple benefits to the Explicit Clock Shift Method.

- The clock relationships are the same for all cases with a +90° setup and -90° hold relationship, making it easy to understand and analyze all four cases in a similar manner.

- The clock relationships make sense when thinking about the <u>key to source-synchronous timing.</u>

- The default setup and hold relationship are always correct so users don't have to worry about adding multicycles like the Implicit Method's <a href="mailto:next-edge/same-edge transfer">next-edge/same-edge transfer</a>.

- Even if the user adds a phase-shift that is not 90 degrees, such as 80 degrees, the default relationships remain correct. See the section on exactly 90 degrees.

- The .sdc setup follows a very cookie-cutter like recipe.

- For me, the biggest benefit is that it's easy to see how the FPGA is being constrained. I think of it as two layers:

- 1) How much the data path inside the FPGA can be skewed compared to the clock path. This is controlled by the equations:

```

Setup Analysis:

FPGA_Data_Delay - FPGA_Clock_Delay < 90° - External_Delay_Max

Hold Analysis:

FPGA_Data_Delay - FPGA_Clock_Delay > -90° - External_Delay_Min

```

2) If the clock is phase-shifted inside the FPGA. This is easy to determine since it must explicitly be done while creating the PLL.

It is the combination of these two layers that determine what the FPGA is doing with the data path and clock path.

## report\_timing: Putting it all together

For any FPGA design, I recommend users create a custom Tcl script that analyzes the I/O interfaces(and anything else the user does custom analysis on). I always create a file called TQ\_analysis.tcl, and have done so for these designs. The file can be accessed from TimeQuest's pull-down menu Scripts, so I can analyze the I/O interface any time I want. This is especially useful if doing iterations to get the constraints correct, and hence I want to keep analyzing the same paths over and over. The contents of TQ analysis.tcl for Case 1 look like so:

```

# Analyze source-synchronous data coming from external clock ssync_clk_ext report_timing -setup -npaths 50 -detail full_path -from_clock {ssync_clk_ext} -panel_name "SSYNC Inputs||setup" report_timing -hold -npaths 50 -detail full_path -from_clock {ssync_clk_ext} -panel_name "SSYNC Inputs||hold"

```

#### Some quick notes:

- These paths are already constrained and analyzed in TimeQuest. This report just breaks them out into custom reports.

- I generally do not add the TQ\_analysis.tcl to the Assignments -> Settings -> TimeQuest -> Tcl Script File. The reason is that TimeQuest will then only report what's in this file and not all the default reports. This behavior should change with Quartus 11.1, in which case I will probably start adding them.

- For I/O analysis, the –detail should be set to full\_path, so that the clock tree is broken out into detail. Unlike internal paths, the source clock path and destination clock path are not symmetric and do not cancel out, so the "-detail full\_path" is important.

- For I/O, report\_timing's "-from\_clock" and "-to\_clock" are useful for reporting all paths to/from an external clock. It's not as necessary for source-synchronous interfaces where the data ports are part of a bus, but for something like a 66MHz PCI bus, where the ports have different names like trdy, irdy, ad[\*], stop, perr, serr, etc. it's easier to report paths based on the single external clock they connect to rather than naming all the individual I/O ports.

- It's important that the -panel\_name option give a good description of the report. And note that the double-pipe || in the panel-name will create a folder in the Report window, which helps organization.

Now let's look at the timing reports. There are a couple things to analyze.

- 1) Are the setup and hold relationship correct, i.e. +/- 90 degrees?

- 2) Is the external delay correct?

- 3) Is the physical path correct?

- 4) What is the difference in delays ignoring the relationship and external delay?

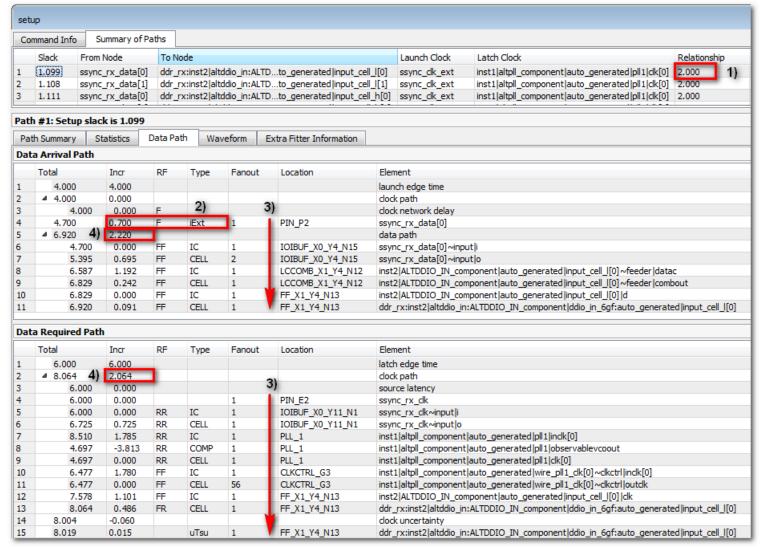

Let's look at the setup report from Case 1:

- ) The setup relationship is 2ns. This is seen in the top-right, but is also the difference between the latch edge and launch edge, 6ns 4ns = 2ns.

- 2) The external delay is labeled iExt and shown as 0.7ns. That is exactly the "set\_input\_delay –max" value from the .sdc.

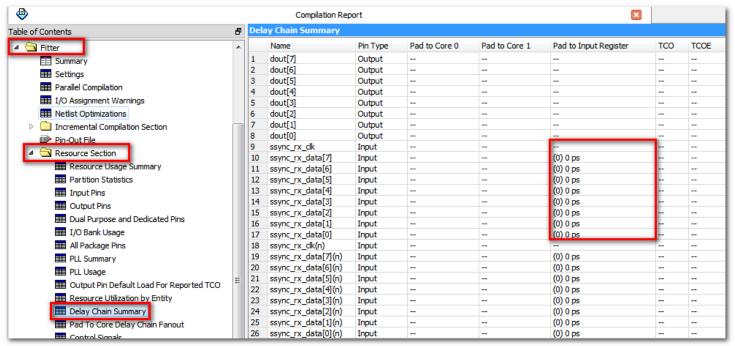

- 3) One can follow the Location and Element column to see exactly what is being analyzed. The Data Arrival Path starts with data ssync\_rx\_data[0] coming in on Pin\_P2, going through the IOIBUF, a combinatorial node LCCOMB, and to the d input of the latching FF at location FF\_X1\_Y4\_N13. The Data Required Path shows the latching clock, which comes in on Pin\_E2, going through the IOIBUF, PLL\_1, the Global Clock tree CLKCTRL\_G3, and finally to the clk port of the latching register at X1\_Y4\_N13. These are the correct paths inside the FPGA. (Note that the targeted device, Cyclone III, does not have DDR registers in the I/O, which is why the register is in the logic fabric).

- 4) Ignoring the launch edge time and the iExt, the data path takes 2.220ns to go from the input port to the FF. Ignoring the latch edge time, the clock takes 2.064ns to go from the input port to the FF, for a difference of 156ps. There is also clock uncertainty of -0.060ps and a uTsu of 15ps at the register, which subtract out for a difference of

0.201ns. So looking at raw FPGA delays, the data path could be (2.220 - 2.064 + 0.06 - 0.015) = 201ps longer than the clock path. When we add the 700ps external delay, that gets us to 901ps across the interface. Since the requirement is half the data window, or 2ns, we've met timing by 2ns - 0.901ns = 1.099ns. That is exactly equal to our slack.

One doesn't have to do this detailed analysis for every constraint, but the point is that they can, and they can feel good the numbers add up. If the user is unsure of their constraints or what is being analyzed, I suggest going through this exercise.

I won't show the hold analysis or any more timing reports, since the user can easily open the specific case projects, compile, launch TimeQuest and run the TQ\_analysis.tcl report.

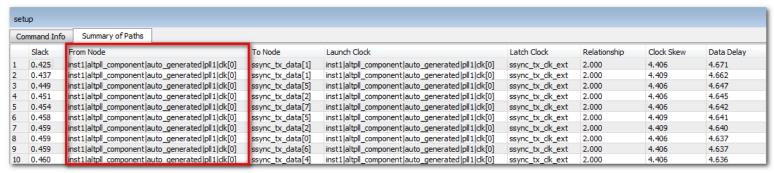

For an output report, here is the setup report from Case 3:

- 1) The setup relationship is 2ns, as it should be. This is seen both at the top-right, and in the difference of latch edge minus launch edge, i.e. 6ns 4ns = 2ns

- 2) The external output delay oExt is -1.2ns. Note that the set\_output\_delay -max value was 1.2ns, which could be added to the Data Arrival Path, but instead is subtracted from the Data Required Path. I'm not sure why it's done this way, but it works out the same.

- 3) The Data Arrival Path starts at input clock fpga\_clk on Pin\_E2, goes through an IO buffer, PLL, global clock G3, the DDIO cell, the IO buffer and out data port Pin\_P2. The

Data Required Path comes in on the same clock port, but works its way to the clock output port ssync\_tx\_clk at Pin\_F2.

**IMPORTANT NOTE:** The output clock is constrained with a create\_generated\_clcok on output port ssync\_tx\_clk, where the –source is the PLL that drives to that port. I occasionally see designs with an incorrect option for -source, whereby Quartus issues the warning:

Warning: No paths exist between clock target "ssync\_tx\_clk" of clock "ssync\_tx\_clk\_ext" and its clock source. Assuming zero source clock latency.

#### **Data Required Path** Type Fanout Location Element 1 4.000 4.000 latch edge time 2 4.000 0.000 clock path source latency 3 4.000 0.000 4 PIN\_F2 0 4.000 0.000 ssync\_tx\_clk 5 4.020 0.020 clock uncertainty oExt PIN K2 1.100 ssync\_tx\_data[4] 5.120

Besides issuing a warning, the Data Required Path would look like so:

This is wrong, as the path for getting the clock off-chip does not include any of the delays inside the FPGA. If your design gets this warning, please fix it before looking at anything else, as the timing analysis is not correct. There are two common causes for this. One is specifying the wrong output tap of the clock. For example, the incorrect timing report just shown was created by using Case 3 and specifying the –source of the create\_generated\_clock as PLL clk[0] instead of clk[1]. Since clk[0] does not actually drive the output port, this problem occurs. The second case is when the output is driven by a ripple clock, i.e. the PLL drives the .clk port of a register before driving the output port.. Clocks do not propagate through registers, and the user must assign a create\_generated\_clock assignment to each stage of a ripple clock. (If the output clock goes through an altddio\_out block, the user does not have to assign a clock to the registers, because the only relevant path is through the mux select, as discussed in the section "DDR outputs: Where are my registers?".)

4) Going back to the correct timing report, the final step is to add up the delays. The delays for the data to get off chip occur in the Data Arrival Path, -2.916 + 4.671 = 1.755ns. The delays for the clock to get off chip occur in the Data Required Path, of 1.494ns, minus the clock uncertainty of -110ps, or 1.384ns. The net difference between the data getting out and the clock is 1.755ns – 1.494 + 110ps = 371ps. Next add in the external –max delay of 1.2ns to make it 1.571ns across the interface. Since the setup relationship is 2ns, we make timing by +429ps, which is the reported slack.

Again, one does not have to go through this analysis, but it's nice to see it once and know how to do it.

# Section III: The Implicit Clock Shift Method

What is the implicit method? Simply put, the implicit method occurs when there is no phase-shift in the interface, and so the clocks are edge-aligned from end to end. Note that if the FPGA phase-shifts the clock as in Case 1 and Case 3, then the user will always use the Explicit Clock Shift Method, as the PLL phase-shift in the FPGA is always explicit. It's really only Case 2 and Case 4 of the Explicit method that could be done with the Implicit Method. There are two cases where the Implicit method occur.

- One scenario I call the "hidden phase-shift". This is where the external device does not state it phase-shifts the clock, and instead makes it sound like the delays are phase-shifted. For example, a transmitting device's datasheet might say that its data is skewed by 1.5ns-2.5ns from the clock. So rather than having a clock shift, the data has a longer output delay. Another example would be a receiving device with a Tsu of 2.5ns and a Th of -1.5ns. When we analyze <a href="External Device Constraints">External Device Constraints</a>, we will look at more examples of this.

- When there really is no phase-shift in the system, and the FPGA must use physical delays to center the clock edge onto the valid data window. The data and clock paths will no longer have matched delays and this difference will vary over PVT, making the interface run more slowly. The only scenarios where I have seen this occur are when the FPGA is the receiving data edge-aligned with the clock, but the FPGA can't phase-shift the clock with a PLL. One reason is that the FPGA does not have enough PLLs, and the other reason is that the latching signal is not a clock but a strobe, in which case a PLL can't be used since it won't remain locked when the strobe disappears. These are not very common situations, and we will discuss them later in this section.

The first thing to do with the Implicit Method is to set up the clock constraints. That is really easy, as there is only one way to do it. When the FPGA is receiving, we do:

```

create_clock -period 8.0 -name ssync_clk [get_ports ssync_rx_clk]

derive_pll_clocks

create_clock -period 8.0 -name ssync_clk_ext

```

Note that the external clock and fpga clock are identical. Also note that if there is a PLL inside the FPGA, it does not constraint the clock. Likewise, when the FPGA is the transmitter, the clock constraints are quite straightforward:

```

create_clock -period 8.0 -name fpga_clk [get_ports fpga_clk]

derive_pll_clocks

create_generated_clock -source {inst1|altpll_component|auto_generated|pll1|clk[0]} -name

ssync_tx_clk_ext [get_ports {ssync_tx_clk}]

```

There really is no need for a PLL in this example, since the clock is not being phase-shifted, but most designs use a PLL anyway. If not, the generated clock on the tx output port would use the input port fpga\_clk for its source.

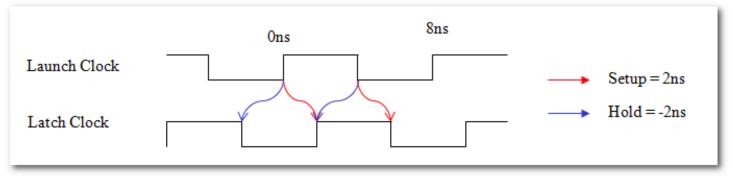

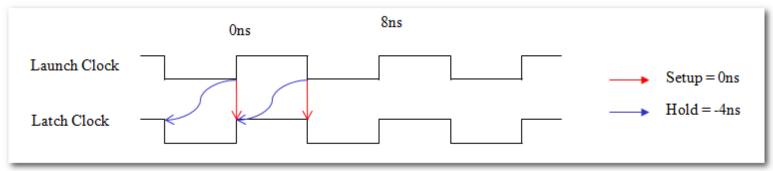

So the clock constraints are easy, but the Implicit Method has a difficult question that needs to be decided by the user that never occurred with the Explicit Method, and is one of the reasons I consider the Implicit Method to be more difficult. Let's start by looking at the relationships for a DDR interface without a clock-shift:

Since this is DDR, every edge launches data and every subsequent edge latches that data. This is called a "next-edge" transfer, although nobody really uses that term since it's just the expected behavior from default analysis. With a setup relationship of 4ns and hold relationship of 0ns, Quartus II will want 2ns added to the data path compared to the clock path, which will have the data arriving midway between the Latch Clock's setup and hold edges. This will give the optimum setup and hold slack.

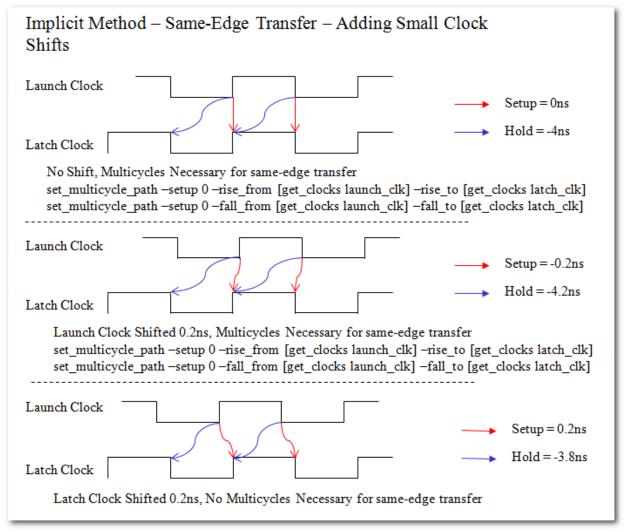

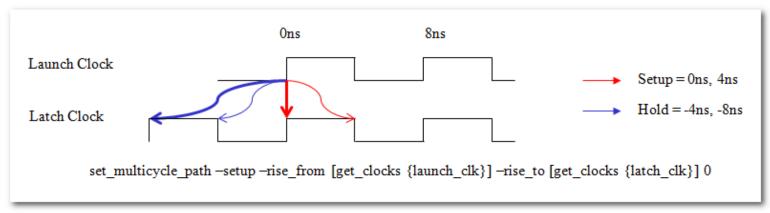

But what if it's better to skew the data -2ns compared to the clock? That would mean we need to shift the setup relationship to 0ns and hold relationship to -4ns, like so:

This is called a "same-edge transfer" because the edge that launches the data is the same edge that will latch it, i.e. when the rising edge at time 0ns launches data, that same clock edge will have a longer delay to the latching register and hence will be the one to latch it.

So how do we tell TimeQuest this is what we want? The quick answer is to add the following two multicycles:

set\_multicycle\_path -setup -rise\_from [get\_clocks {launch\_clk}] -rise\_to [get\_clocks {latch\_clk}] 0 set\_multicycle\_path -setup -fall\_from [get\_clocks {launch\_clk}] -fall\_to [get\_clocks {latch\_clk}] 0

For more details on why, please look at the Implicit Method: Same-Edge Transfers.

Note that the projects in Case 5 and Case 6 use the default relationship and hence a next-edge transfer, but the .sdc also has the multicycles that allow for a same-edge transfer, but they are commented out.

Deciding whether to use the next-edge transfer or same-edge transfer will make more sense once we cover the implied phase-shift.

## The Implied Phase-Shift

For good source-synchronous performance we want to phase-shift the clock somewhere along the interface, yet our clocks are aligned end-to-end. So how does this method get good performance? The key is that the external data delays imply a phase shift. For example, let's say a receiver said it had a Tsu of 2.5ns and a Th of -1.5ns. There is no mention of a clock-shift and the set\_output\_delay would have a -max 2.5ns and -min 1.5ns.

Taking a step back, remember that there are two variables controlled by the user for I/O constraints, the relationship and the external delay. (Four variables in total, as there is a setup relationship and external –max delay, and hold relationship and external –min delay, but they are analyzed separately). Let's look at some of the equations we used earlier:

```

Setup Analysis:

```

```

FPGA_Data_Delay - FPGA_Clock_Delay < Setup_Relationship - External_Delay_Max

Hold Analysis:

FPGA_Data_Delay - FPGA_Clock_Delay > Hold_Relationship - External_Delay_Min

```

In the Explicit Clock Shift Method, the setup relationship is +90 degrees and the hold relationship is -90 degrees, or +/-2ns for an 8ns clock. Making up terms, let's say the external – max delay is 0.7ns and the external min delay is -0.6ns, resulting in:

```

FPGA\_Data\_Delay - FPGA\_Clock\_Delay < 2 - 0.7

FPGA\_Data\_Delay - FPGA\_Clock\_Delay > -2 - (-0.6)

```

Or:

```

FPGA_Data_Delay - FPGA_Clock_Delay < 1.3

FPGA_Data_Delay - FPGA_Clock_Delay > -1.4

```

Now with the Implicit Method, the default setup relationship is 4 and the default hold relationship is 0. But what if the external delays had 2ns added to both of them for a –max delay of 2.7 and –min delay 1.4. The new analysis would be:

```

FPGA_Data_Delay - FPGA_Clock_Delay < 4 - 2.7

FPGA_Data_Delay - FPGA_Clock_Delay > 0 - 1.4

```

Or:

```

FPGA_Data_Delay - FPGA_Clock_Delay < 1.3

FPGA_Data_Delay - FPGA_Clock_Delay > -1.4

```

As you can see, the FPGA is constrained in the exact same manner, where the (FPGA\_Data\_Delay – FPGA\_Clock\_Delay) must be less than 1.3ns and greater than -1.4ns. Remember that the FPGA is NOT phase-shifting the clock. In the Explicit Method, we say that the external device is phase-shifting the clock, which affects our setup and hold relationship. In the Implicit Method we do not say it phase-shifts the clock, and instead state that the external device's delays are "shifted". If we want to subtract 90 degrees from the data delays, then we need to add multicycles to tell TimeQuest to use the same-edge transfer setup and hold relationships of 0 and -4. The external delays would also be shifted by -2ns to 0.7 - 2 = -1.3ns and -0.6 - 2 = -2.6ns. That allows us to do:

```

FPGA_Data_Delay - FPGA_Clock_Delay < 0 - (-1.3)

FPGA_Data_Delay - FPGA_Clock_Delay > -4 - (-2.6)

Or:

FPGA_Data_Delay - FPGA_Clock_Delay < 1.3

FPGA_Data_Delay - FPGA_Clock_Delay > -1.4

```

As can be seen, I call this the Implicit Clock Shift because the data delays have been shifted by -2ns instead of having the clock shifted. We know there needs to be a clock phase-shift in the system to get optimal timing. The explicit method clearly shows that shift in the clock relationships while the implicit method keeps the clocks aligned and instead shifts the external delays by +/-90 degrees.

A quick rule of thumb is if the external delays are symmetric around 0, such as a max of 0.5 and min of -0.5, then the explicit method is being used. If they have an offset near 90 degrees, such as a max of 2.5 and min of 1.5, then the Implicit Method is being used with the default setup and hold relationships. If they have a -90 degree offset, such as a max of -1.5 and min of -2.5, then they are using the Implicit Method and need multicycles to specify a same-edge transfer.

Why have all these methods? The main reason is to allow users to properly describe the external device, and there will be examples in the <a href="External Devices Constraint Examples">External Devices Constraint Examples</a>.

## Case 5: FPGA is Receiver, Implicit Method

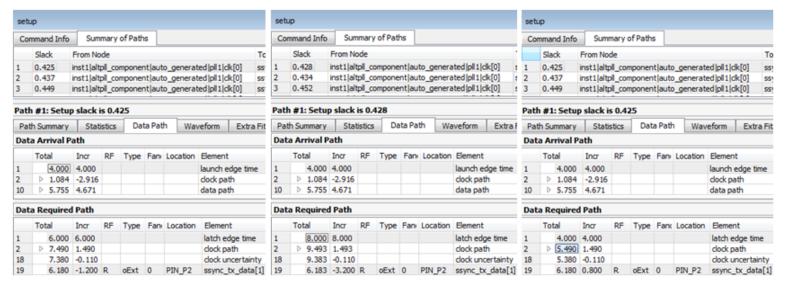

The Case 5 design is identical to Case 2 except for the .sdc. The FPGA is receiving source synchronous data, the FPGA is not phase-shifting the clock. The only difference is how we describe the external world. Using the Explicit Method in Case 2, the external device phase-shifted the clock 90 degrees and the external delays described how much skew there was from the external device. The .sdc in Case 5 does not phase-shift the external clock, but instead adds 2ns to the external delays. There is also another solution commented out, where the external delays have 2ns subtracted from them and multicycles are added to tell TimeQuest it is transferring data to the previous edge. Let's look at them side-by-side, with major differences in red:

#### Case 2 ssync test.sdc

#### **Setup Relationship = 2ns, Hold Relationship = 2ns**

```

create_clock -period 8.0 -name ssync_clk [get_ports ssync_rx_clk]

derive_pll_clocks

create_clock -period 8.0 -name ssync_clk_ext -waveform {6.0 10.0}

set_input_delay -clock ssync_clk_ext -max 0.7 [get_ports {ssync_rx_data[*]}]

set_input_delay -clock ssync_clk_ext -min -0.6 [get_ports {ssync_rx_data[*]}]

set_input_delay -clock ssync_clk_ext -max 0.7 [get_ports {ssync_rx_data[*]}] -clock_fall -add_delay

set_input_delay -clock ssync_clk_ext -min -0.6 [get_ports {ssync_rx_data[*]}] -clock_fall -add_delay

```

### Case 5 ssync\_test.sdc – Default setup and hold Setup Relationship = 4ns, Hold Relationship = 0ns

```

create_clock -period 8.0 -name ssync_clk [get_ports ssync_rx_clk]

derive_pll_clocks

create_clock -period 8.0 -name ssync_clk_ext

set_input_delay -clock ssync_clk_ext -max 2.7 [get_ports {ssync_rx_data[*]}]

set_input_delay -clock ssync_clk_ext -min 1.4 [get_ports {ssync_rx_data[*]}]

set_input_delay -clock ssync_clk_ext -max 2.7 [get_ports {ssync_rx_data[*]}] -clock_fall -add_delay

set_input_delay -clock ssync_clk_ext -min -1.4 [get_ports {ssync_rx_data[*]}] -clock_fall -add_delay

```

#### Case 5 ssync\_test.sdc – Multicycle setup and hold: Setup Relationship = 0ns, Hold Relationship = 4ns

```

create_clock -period 8.0 -name ssync_clk [get_ports ssync_rx_clk]

derive_pll_clocks

create_clock -period 8.0 -name ssync_clk_ext

set_multicycle_path -setup -rise_from [get_clocks {ssync_rx_clk}] -rise_to [get_clocks

{inst1|altpll_component|auto_generated|pll1|clk[0]} 0

set_multicycle_path -setup -fall_from [get_clocks {ssync_rx_clk}] -fall_to [get_clocks

{inst1|altpll_component|auto_generated|pll1|clk[0]} 0

set_input_delay -clock ssync_clk_ext -max -1.3 [get_ports {ssync_rx_data[*]}]

set_input_delay -clock ssync_clk_ext -min -2.6 [get_ports {ssync_rx_data[*]}]

set_input_delay -clock ssync_clk_ext -max -1.3 [get_ports {ssync_rx_data[*]}] -clock_fall -add_delay

set_input_delay -clock ssync_clk_ext -min -2.6 [get_ports {ssync_rx_data[*]}] -clock_fall -add_delay

```

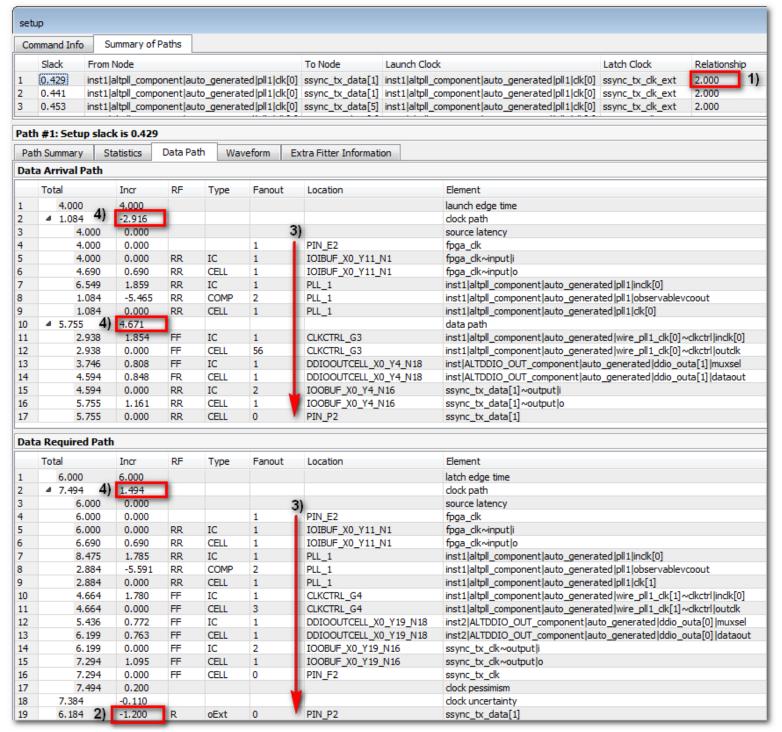

These three methods constrain the FPGA identically. I ran place-and-route of Case 5 and then ran TimeQuest with the different .sdc files. Below are the setup reports, and you'll see that the slack is identical. The only thing that changes is the Setup Relationship(which is Launch Edge – Latch Edge) and the iExt delay, which is from the .sdc's set\_input\_delay –max:

So if the three methods are identical, which one do we use? It really depends on how the user wants to describe their external device. We'll cover this more in the <a href="External Device">External Device</a> <a href="External Device">Examples</a>, but here's a quick example.

Case 2 ssync\_test.sdc – This could be used if the external transmitter said it was sending the clock center-aligned and its data could vary by +0.7ns to -0.6ns.

Case 5 ssync\_test.sdc, Default Relationships – This could be used if the external transmitter said it was sending source-synchronous data, and the data would transition between 1.4ns to 2.7ns AFTER the clock.

Case 5 ssync\_test.sdc, Multicycle – This could be used if the external transmitter said it was sending source-synchronous data, and the data would transition between 1.3 to 2.6ns BEFORE the clock(i.e. the data to clock skew would be -1.3 to -2.6).

## Case 6: FPGA is Transmitter, Implicit Method

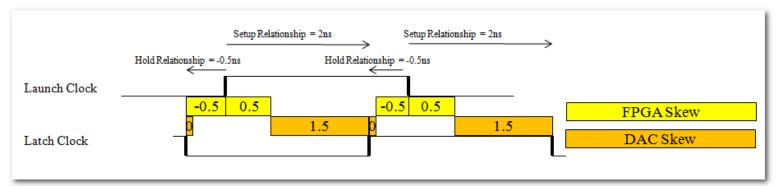

The design in Case 6 is identical to Case 4 in that the FPGA is transmitting source-synchronous clock and data and does not phase-shift the clock. The only differences are in the .sdc constraint. The first difference is that we do not say the external clock is phase-shifted by removing the –phase option from the create\_generated\_clock constraint. This makes the default setup relationship 4ns and the default hold relationship 0ns. Next, we add 2ns to the external delays.

The .sdc has a second option that is commented out, whereby multicycles are used to state that the FPGA is latching data on the same edge that launches it. This results in a setup relationship of 0ns and a hold relationship of -4ns. The external delays are then shifted by -2ns. Summarizing the three options:

Case 4 ssync\_test.sdc

Setup Relationship = 2ns, Hold Relationship = 2ns

create clock -period 8.0 -name fpga clk [get ports fpga clk]

```

derive_pll_clocks

create_generated_clock -source [get_pins {inst1|altpll_component|auto_generated|pll1|clk[0]}] -name

ssync_tx_clk_ext [get_ports {ssync_tx_clk}] -phase 90

set_output_delay -clock ssync_tx_clk_ext -max 1.2 [get_ports {ssync_tx_data[*]}]

set_output_delay -clock ssync_tx_clk_ext -min -1.1 [get_ports {ssync_tx_data[*]}]

set_output_delay -clock ssync_tx_clk_ext -max 1.2 [get_ports {ssync_tx_data[*]}] -clock_fall -add_delay

set_output_delay -clock ssync_tx_clk_ext -min -1.1 [get_ports {ssync_tx_data[*]}] -clock_fall -add_delay

```

### Case 6 ssync\_test.sdc – Default setup and hold Setup Relationship = 4ns, Hold Relationship = 0ns

```

create_clock -period 8.0 -name fpga_clk [get_ports fpga_clk]

derive_pll_clocks

create_generated_clock -source [get_pins {inst1|altpll_component|auto_generated|pll1|clk[0]}] -name

ssync_tx_clk_ext [get_ports {ssync_tx_clk}] set_output_delay -clock ssync_tx_clk_ext -max 3.2

[get_ports {ssync_tx_data[*]}]

set_output_delay -clock ssync_tx_clk_ext -min 0.9 [get_ports {ssync_tx_data[*]}] set_output_delay -clock ssync_tx_clk_ext -max 3.2 [get_ports {ssync_tx_data[*]}] -clock_fall -add_delay

set_output_delay -clock ssync_tx_clk_ext -min 0.9 [get_ports {ssync_tx_data[*]}] -clock_fall -add_delay

```

#### Case 6 ssync\_test.sdc – Multicycle setup and hold: Setup Relationship = 0ns, Hold Relationship = 4ns

```

create_clock -period 8.0 -name fpga_clk [get_ports fpga_clk]

derive_pll_clocks

create_generated_clock -source [get_pins {inst1|altpll_component|auto_generated|pll1|clk[0]}] -name

ssync_tx_clk_ext [get_ports {ssync_tx_clk}] set_output_delay -clock ssync_tx_clk_ext -max 3.2

[get_ports {ssync_tx_data[*]}]

set_multicycle_path -setup -rise_from [get_clocks

{inst1|altpll_component|auto_generated|pll1|clk[0]}] -rise_to [get_clocks {ssync_tx_clk_ext}] 0

set_multicycle_path -setup -fall_from [get_clocks {inst1|altpll_component|auto_generated|pll1|clk[0]}]

-fall_to [get_clocks {ssync_tx_clk_ext}] 0

set_output_delay -clock ssync_tx_clk_ext -max -0.8 [get_ports {ssync_tx_data[*]}]

set_output_delay -clock ssync_tx_clk_ext -min -3.1 [get_ports {ssync_tx_data[*]}]

set_output_delay -clock ssync_tx_clk_ext -max -0.8 [get_ports {ssync_tx_data[*]}] -clock_fall -add_delay

set_output_delay -clock ssync_tx_clk_ext -max -0.8 [get_ports {ssync_tx_data[*]}] -clock_fall -add_delay