# SGMII Interface Implementation Using Soft CDR Mode of Altera FPGAs

#### 2013.10.17

AN-518 Subscribe 💭 Send Feedback

The Serial Gigabit Media Independent Interface (SGMII) protocol provides connectivity between the physical layer (PHY) and the Ethernet media controller (MAC). The SGMII solution for Altera<sup>®</sup> FPGAs allows you to implement multiport Gbps Ethernet (GbE) systems with high port counts, low power, and low cost requirements.

The LVDS hard macros in the soft clock data recover (CDR) mode and Triple-Speed Ethernet MegaCore<sup>®</sup> implement the physical coding sublayer (PCS) and media access control (MAC) function for Altera FPGAs. You can use the soft CDR mode to implement SGMII systems in the following Altera FPGAs:

- Stratix<sup>®</sup> V, Stratix IV, and Stratix III

- Arria<sup>®</sup> V, and Arria II

A typical SGMII implementation uses 16 to 48 full-duplex links. With the sufficient number of transmitters and receivers in Altera FPGAs, you can implement multiple full-duplex channels. In such dense applications, the LVDS I/O standard is preferred because of its low-voltage differential signaling capability. You can implement the following SGMII connectivity with Altera FPGAs:

- Transmit side—using LVDS hard macros.

- Receive side—using LVDS hard macros configures in soft CDR mode.

### **Related Information**

- Serial-GMII Specification Revision 1.8 Cisco System's proprietary specification document for SGMII.

- High-Speed Differential I/O Interfaces and DPA in Stratix V Devices

- High Speed Differential I/O Interfaces with DPA in Stratix IV Devices

- High-Speed Differential I/O Interfaces with DPA in Stratix III Devices

- High-Speed Differential I/O Interfaces and DPA in Arria V Devices

- High-Speed Differential I/O Interfaces and DPA in Arria II Devices

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO 9001:2008 Registered

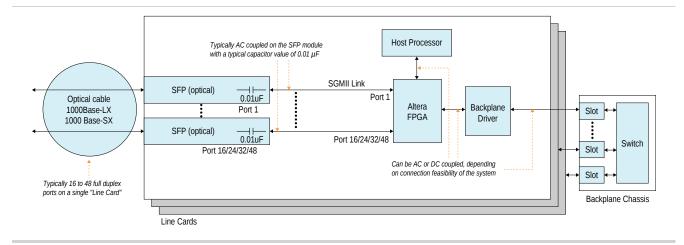

# Interfacing MAC and PHY Through SFP Transceiver

Among the wide support for interfacing with other devices on a typical line card, the Altera FPGAs provide connectivity between the following modules:

- GbE port—a small form factor pluggable optical or copper (SFP) transceiver

- Host processor

2

• Backplane driver

### Figure 1: SGMII Connectivity Using an Altera FPGA through Optical SFP Transceiver

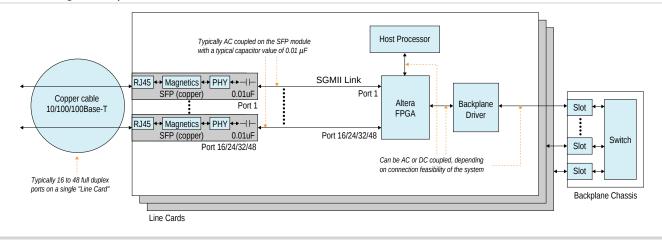

#### Figure 2: SGMII Connectivity Using an Altera FPGA through Copper SFP Transceiver

The PHY device is part of the copper SFP module. The copper SFP module retimes the data to enable interoperability.

#### **Related Information**

- Small Form-factor Pluggable (SFP) Transceiver MultiSource Agreement (MSA) Provides more information about the SFP transceiver specification.

- Interfacing 3.3 V LVPECL to 2.5 V LVDS (SFP Module to Altera FPGA) on page 3

SGMII Interface Implementation Using Soft CDR Mode of Altera FPGAs

- Interfacing 2.5 V LVDS to 3.3 V LVPECL (Altera FPGA to SFP Module) on page 4

- Interfacing PCML to 2.5 V LVDS (Altera FPGA to Altera FPGA) on page 5

- Interfacing 2.5 V LVDS to LVDS (Altera FPGA to Altera FPGA) on page 5

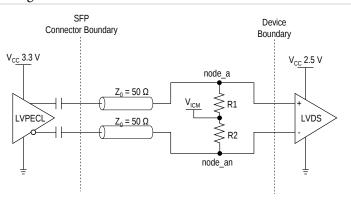

# Interfacing 3.3 V LVPECL to 2.5 V LVDS (SFP Module to Altera FPGA)

The optical or copper SFP modules are typically AC coupled on the SGMII side of the interface. This AC coupling is present within the SFP modules.

In the LVPECL-to-LVDS interface, the on-chip termination (OCT) on the FPGA LVDS receiver is disabled.

Altera recommends that you implement a resistor network that can raise the common mode voltage for the LVDS receiver. This is because the output swing of the LVPECL transmitter on the SFP and the input amplitude sustainable by the LVDS receiver on the FPGA are not compatible.

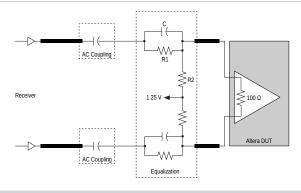

### Figure 3: LVPECL-to-LVDS (3.3 V SFP to 2.5 V FPGA)

This figure shows a resistor network example to raise the common mode voltage for the LVDS receiver. The example assumes that the signal going out of SFP module is AC coupled and the trace impedance between the two devices is 50  $\Omega$  single-ended.

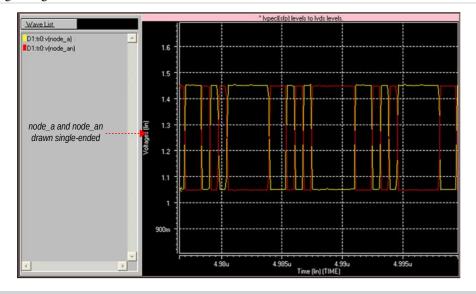

### Figure 4: LVPECL-to-LVDS HSPICE Simulation Results

This figure shows the simulation results where the resistor network raises the common mode voltage of the signal incoming to the FPGA LVDS receiver to  $V_{ICM}$ . The  $V_{ICM}$  is set to 1.25 V to match the input common mode voltage range of the receiver. The value of the resistors are 50  $\Omega$  each.

#### **Related Information**

- Stratix V Device Datasheet

- DC and Switching Characteristics for Stratix IV Devices

- DC and Switching Characteristics of Stratix III Devices

- Arria V Device Datasheet

- Device Datasheet for Arria II Devices

# Interfacing 2.5 V LVDS to 3.3 V LVPECL (Altera FPGA to SFP Module)

In the LVDS-to-LVPECL interface, you do not need a resistor network. This is because the SFP receiver LVPECL input voltage and input common mode voltage tolerances on the SFP receiver are greater than the maximum LVDS output amplitude and output common mode voltage on the transmitter FPGA.

The following conditions are assumed:

- The FPGA LVDS transmitter is operating at maximum output voltage settings with maximum preemphasis.

- The SFP module in the interface is AC coupled, as typically set for connectors in SGMII systems.

#### **Related Information**

- Stratix V Device Datasheet

- DC and Switching Characteristics for Stratix IV Devices

- DC and Switching Characteristics of Stratix III Devices

- Arria V Device Datasheet

- Device Datasheet for Arria II Devices

- **Programmable V<sub>OD</sub> and Programmable Pre-Emphasis** on page 15 Provides instructions to set the LVDS settings in Altera FPGAs.

# Interfacing PCML to 2.5 V LVDS (Altera FPGA to Altera FPGA)

In the PCML-to-LVDS interface, you do not need a resistor network if DC coupling is supported between the PCML transmitter and the LVDS receiver in the FPGA. In this interface, you can enable OCT on the LVDS receiver.

Adjust the output amplitude of the PCML transmitter device so that the signal amplitude at the input of the LVDS receiver is within the input voltage specification. For the device-specific switching characteristics and supported I/O standards of the PCML transmitter and LVDS receiver refer to the relevant device datasheet.

#### **Related Information**

- Stratix V Device Datasheet

- DC and Switching Characteristics for Stratix IV Devices

- DC and Switching Characteristics of Stratix III Devices

- Arria V Device Datasheet

- Device Datasheet for Arria II Devices

### Interfacing 2.5 V LVDS to LVDS (Altera FPGA to Altera FPGA)

In the LVDS-to-LVDS interface, you do not need a resistor network. This is because AC or DC coupling is supported between the LVDS transmitter and LVDS receiver.

Configure the receiver FPGA for LVDS I/O standards with the proper input common mode voltage and input signal amplitude range. For the input common mode voltage and input signal amplitude requirement, refer to the relevant device datasheet.

For example, if the receiver is a Stratix II GX FPGA, configure the receiver to the LVDS I/O standard with input common mode voltage of 1.2 V. The input signal amplitude range of the Stratix II GX FPGA is 100 mV to 900 mV, single-ended.

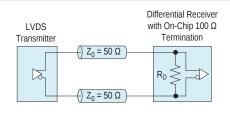

In the LVDS-to-LVDS interface, enable OCT on the LVDS receiver FPGA. Altera FPGAs provide a 100  $\Omega$  differential OCT option on each differential receiver channel for LVDS I/O standards.

#### Figure 5: On-Chip Differential I/O Termination

SGMII Interface Implementation Using Soft CDR Mode of Altera FPGAs

#### **Related Information**

- Stratix V Device Datasheet

- DC and Switching Characteristics for Stratix IV Devices

- DC and Switching Characteristics of Stratix III Devices

- Arria V Device Datasheet

- Device Datasheet for Arria II Devices

### Interfacing 2.5 LVDS to LVDS (Altera FPGA to LVDS Device)

The Altera LVDS interface is compatible with the LVDS I/O standards of third-party devices. For information and specifications, refer to the documentation provided by the specific device vendor.

# Interfacing MAC and PHY without SFP Transceiver

Altera FPGAs can interface with RJ45 device through a PHY device. This interface link can be AC or DC coupled, as shown in the following figure.

#### Host Processor SGMII Link RJ45 + Magnetics + PHY Port 1 Copper cable Port 1 Altera Backplane Slot 10/100/100Base-T FPGA Driver RJ45 ↔ Magnetics ↔ PHY Port 16/24/32/48 Switch Port 16/24/32/48 Slot Can be AC or DC coupled Slot Typically 16 to 48 full duples ports on a single "Line Card Backplane Chassis Line Cards

#### Figure 6: SGMII Connectivity using Altera FPGA without SFP Transceiver

# **Receiver Data Path Modes for SGMII in Altera FPGAs**

You can configure the built-in serializer/deserializer (SERDES) circuitry in Altera FPGAs to support source-synchronous and asynchronous serial data communication for SGMII interfaces.

You can achieve data communication for SGMII interfaces using the soft CDR and DPA modes in the receiver data path.

### Table 1: Typical SGMII System Scenarios

| Receiver Data Path Mode                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Soft CDR mode in asynchronous<br>systems | <ul> <li>No source-synchronous clock is sent with the data channels from the upstream transmitter.</li> <li>The upstream transmitter and receiver nodes use reference clocks from two different sources. This causes a potential parts per million (ppm) difference between the upstream transmitter and receiver nodes.</li> <li>The maximum ppm difference allowed between the two clock sources is ±100 ppm.</li> <li>An asynchronous system is typically used for chip-to-chip or board-to-board communication with an optional backplane.</li> </ul> |

| Soft CDR mode in synchronous<br>systems  | <ul> <li>No source-synchronous clock is sent with the data channels from the upstream transmitter.</li> <li>The upstream transmitter and receiver nodes use reference clocks from the same source.</li> </ul>                                                                                                                                                                                                                                                                                                                                             |

| Source-synchronous mode                  | <ul> <li>A source-synchronous clock is sent with the data channels.</li> <li>The receiver nodes use the source-synchronous clock to recover the received data.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                 |

# Configuring ALTLVDS\_TX Megafunction for the LVDS Transmitter

Use the MegaWizard Plug-in Manager in the Quartus II software to create a new custom variation of the LVDS transmitter and configure it for SGMII implementation.

**Note:** If you instantiate a single channel SGMII transmitter instance multiple times to create a multichannel SGMII interface, the Quartus II software automatically selects the same PLL to drive these multiple instances if the same reference clock source is shared.

### Table 2: Specific ALTLVDS\_TX Megafunction Settings for SGMII Implementation

This table lists the specific options and settings required for SGMII implementation on the transmitter.

| Option                                          | Instruction                               |

|-------------------------------------------------|-------------------------------------------|

| Which megafunction would you like to customize? | Expand I/O and select ALTLVDS_TX.         |

| What is the number of Channels?                 | Select the number of channels.            |

| What is the deserialization factor?             | Select 10.                                |

| What is the output data rate?                   | Туре 1250.                                |

| Specify the input clock rate by                 | Select clock frequency of <b>125</b> MHz. |

| Option                                           | Instruction                                                                                                                                                                               |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Use shared PLL(s) for receivers and transmitters | Turn on if you want to share the PLLs to both the<br>transmitter and receiver instances. Sharing the PLLs<br>is allowed for transmitters and receivers on the same<br>side of the device. |

| Use 'tx_outclock' output port                    | Turn off if you are using a synchronous/asynchronous system (receiver in soft-CDR mode).                                                                                                  |

| What is the outclock divide factor (B)?          | Select the divide factor so that the output clock frequency is within the device specification.                                                                                           |

|                                                  | This option is applicable if you turn on <b>Use 'tx_</b><br>outclock' output port.                                                                                                        |

- 1. Open the MegaWizard Plug-In Manager.

- **2.** Create a new custom variation of the ALTLVDS\_TX megafunction.

- 3. Navigate through the MegaWizard Plug-In Manager and specify all necessary options and settings for your design.

Refer to Table 2.

#### **Related Information**

8

**LVDS SERDES Transmitter/Receiver (ALTLVDS\_RX/TX) Megafunction User Guide** Provides more details about the ALTLVDS\_TX and ALTLVDS\_RX megafunctions.

# Configuring ALTLVDS\_RX Megafunction for the LVDS Receiver

Use the MegaWizard Plug-in Manager in the Quartus II software to create a new custom variation of the LVDS receiver and configure it for SGMII implementation.

**Note:** If you instantiate a single channel SGMII transmitter instance multiple times to create a multichannel SGMII interface, the Quartus II software automatically selects the same PLL to drive these multiple instances if the same reference clock source is shared.

### Table 3: Specific ALTLVDS\_RX Megafunction Settings for SGMII Implementation

This table lists the specific options and settings required for SGMII implementation on the receiver.

The ppm value for **What is the simulated recovered clock phase drift?** option in the ALTLVDS\_RX megafunction is used only for simulation purposes and has no significance in the real hardware.

| Option                                          | Instruction                       |

|-------------------------------------------------|-----------------------------------|

| Which megafunction would you like to customize? | Expand I/O and select ALTLVDS_RX. |

| Enable Dynamic Phase Alignment mode             | Turn on.                          |

| What is the number of Channels?                 | Select the number of channels.    |

| What is the deserialization factor?             | Select 10.                        |

| What is the input data rate?                    | Туре 1250.                        |

**Altera Corporation**

| Option                                                                                             | Instruction                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Specify the input clock rate by                                                                    | Select clock frequency of <b>125</b> MHz.                                                                                                                                                 |

| Use shared PLL(s) for receivers and transmitters                                                   | Turn on if you want to share the PLLs to both the<br>transmitter and receiver instances. Sharing the PLLs<br>is allowed for transmitters and receivers on the same<br>side of the device. |

| Use 'rx_divfwdclk' output port and bypass the DPA<br>FIFO                                          | Turn on to select soft CDR mode.                                                                                                                                                          |

| Use 'rx_reset' input port                                                                          | Turn on.                                                                                                                                                                                  |

|                                                                                                    | In soft CDR mode, it is not necessary to use the rx_<br>dpa_locked output port.                                                                                                           |

| Use a DPA initial phase selection of                                                               | Optional. Turn on if required by your design and select the degree of phase selection.                                                                                                    |

| Use 'rx_channel_data_align' input port                                                             | Turn on.                                                                                                                                                                                  |

| After how many pulses does the data alignment circuitry restore the serial data latency back to 0? | Select 10.                                                                                                                                                                                |

| Use 'rx_cda_reset' input port                                                                      | Optional. Turn on as a reset to the data realignment<br>(bit-slip) circuitry.                                                                                                             |

1. Open the MegaWizard Plug-In Manager.

- 2. Create a new custom variation of the ALTLVDS\_RX megafunction.

- 3. Navigate through the MegaWizard Plug-In Manager and specify all necessary options and settings for your design.

Refer to Table 3.

### **Related Information**

**LVDS SERDES Transmitter/Receiver (ALTLVDS\_RX/TX) Megafunction User Guide** Provides more details about the ALTLVDS\_TX and ALTLVDS\_RX megafunctions.

# Soft CDR Clocking Scheme for SGMII Implementation

There are PLLs on different sides of the device. If you use only one side of the FPGA to implement all your SGMII LVDS interfaces, you need only one PLL.

SGMII Interface Implementation Using Soft CDR Mode of Altera FPGAs

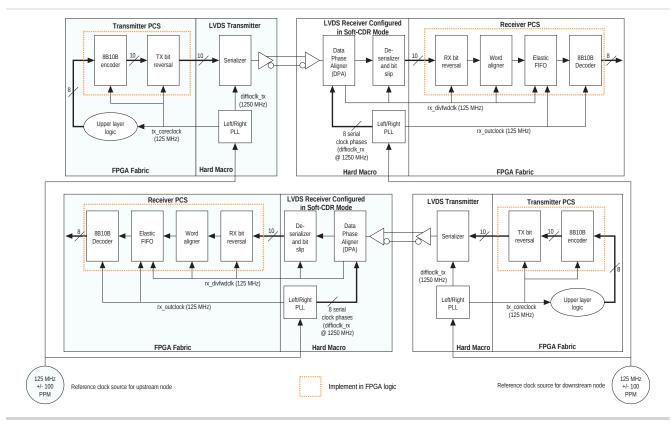

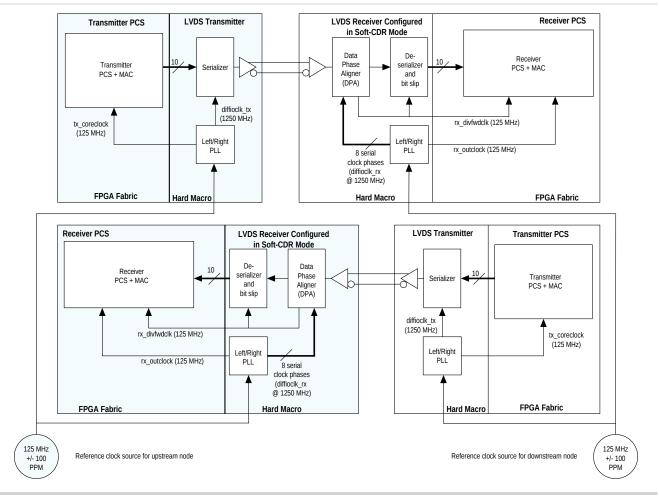

### Figure 7: SGMII Clocking Scheme for Soft-CDR Mode

This diagram shows an example SGMII system implemented on an Altera evaluation board with the Altera Triple-Speed Ethernet MegaCore using an LVDS hard macro configured as soft-CDR:

- The transmitter and receiver at the upstream and downstream node use a shared PLL. •

- Typically, the reference clock sources for transmitter and receiver use 125 MHz/62.5 MHz with ppm tolerance of  $\pm 100$  ppm.

# **Table 4: Clocks Produced by the LVDS Transmitters**

For LVDS transmitters, the PLLs typically take a 125 MHz/62.5 MHz reference clock and produces three clocks.

| Clock        | Description                                                                                                                                                                                             |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| diffioclk_tx | This LVDS serial clock runs at 1.25 GHz. The LVDS serial clock is internal to the hard macro and is not brought out to the output port of the ALTLVDS transmitter instantiation.                        |

| tx_outclock  | This clock is used in source synchronous LVDS systems (DPA mode) to<br>send the synchronous clock together with transmitted data. This clock<br>is not used in the soft-CDR mode of the LVDS receivers. |

11

| Clock        | Description                                                                                            |

|--------------|--------------------------------------------------------------------------------------------------------|

| tx_coreclock | This clock runs at 125 MHz and is used for clocking these PCS functional blocks:                       |

|              | <ul> <li>8B/10B encoder</li> <li>TX bit reversal block</li> <li>Any other FPGA fabric logic</li> </ul> |

### Table 5: Clocks Produced by the LVDS Transmitters and Receivers

For LVDS receivers, the PLL typically takes the 125 MHz/62.5 MHz reference clock and produces two clocks.

| Clock        | Description                                                                                                                                                                                                                                                              |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| diffioclk_rx | There are eight LVDS fast clocks running at 1.25 GHz with eight varying phases in the 45 degrees steps. The LVDS serial clock is internal to the hard macro and is not brought out to the output port. All eight clocks with different phases are sent to the DPA block. |

| rx_outclock  | This is the LVDS slow clock at 125 MHz that is sent to the FPGA fabric.<br>You can use this clock for decoupling the clock domain from the<br>rx_divfwdclk clock in the rate matcher or elastic FIFO block.                                                              |

On the LVDS receiver, the DPA block takes eight phases of serial clock from the PLL and chooses the serial clock that is best phase-aligned to the incoming serial data. The DPA block also divides this selected high speed serial clock (1.25 GHz) by the serialization factor of 10 and sends rx\_divfwdclk (125 MHz) together with the parallel data to the FPGA fabric.

# **Implementing the Transmitter PCS Datapath**

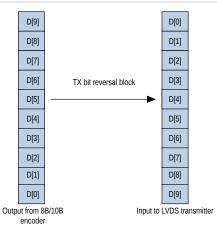

On the upstream transmitter side, upper layer logic sends 8-bit data to the 8B/10B encoder block in the PCS layer. After encoding, the 8B/10B encoder sends the 10-bit data to the transmitter reversal block. After inverting the bit order in the 10-bit word, the transmitter bit reversal block sends the data to the LVDS transmitter. In the LVDS transmitter, parallel data is serialized and sent to the transmitter buffers.

#### Table 6: Transmitter PCS Blocks

| Block                    | Description                                                                                                                                                                                                                                                                                                    |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8B/10B encoder           | • The 8B/10 encoder performs the following function:                                                                                                                                                                                                                                                           |

|                          | <ul> <li>Takes in 8-bit data from the MAC layer of the GbE protocol in the FPGA fabric.</li> <li>Generates a 10-bit code group with proper running disparity from the 8-bit character.</li> <li>Feeds the 10-bit encoded data output from the 8B/10B encoder to the transmitter bit reversal block.</li> </ul> |

|                          | • Implement the 8B/10B decoder according to the IEEE 802.3 specifica-<br>tion.                                                                                                                                                                                                                                 |

| Transmitter bit reversal | <ul> <li>By default, the bit order of the LVDS transmitter serializer is from most significant bit (MSB) to least significant bit (LSB).</li> <li>Use the transmitter bit reversal block to reverse the bit order to LSB-to-MSB in accordance with the IEEE 802.3 standards.</li> </ul>                        |

Implement these blocks to complete the transmitter PCS layer with an LVDS hard macro.

### Figure 8: Transmitter Bit Order Reversal

This figure shows the transmitter bit reversal block function for 10 bit wide data.

#### **Related Information**

- High-Speed Differential I/O Interfaces and DPA in Stratix V Devices

- High Speed Differential I/O Interfaces with DPA in Stratix IV Devices

- High-Speed Differential I/O Interfaces with DPA in Stratix III Devices

- High-Speed Differential I/O Interfaces and DPA in Arria V Devices

- High-Speed Differential I/O Interfaces and DPA in Arria II Devices

# **Implementing the Receiver PCS Datapath**

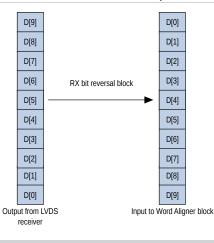

The PLL typically takes a 125 MHz/62.5 MHz reference clock and sends eight phases of 1.25 GHz serial clocks to the DPA block. The DPA block takes the serial data at 1.25 Gbps and selects the best phase-aligned clock using the incoming serial data. This selected DPA phase-aligned clock is used to clock the bit-slip and deserializer circuitries. The deserializer block converts the serial data stream into parallel 10-bit data and sends it to the RX bit reversal block in the FPGA fabric.

### Table 7: Receiver PCS Blocks

Implement these blocks to complete the receiver PCS layer.

| Block                 | Description                                                                                                                                                                                                                                                                                           |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Receiver bit reversal | <ul> <li>By default, the LVDS receiver assumes an MSB-to-LSB bit order transmission in accordance with the IEEE 802.3 standards.</li> <li>If the transmission order is LSB-to-MSB, the receiver bit reversal block reverses the data word bit order received on the FPGA fabric interface.</li> </ul> |

Send Feedback

|              | - 2013.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Block        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Word aligner | SGMII interfaces require synchronization to align the byte boundaries of the receiver and upstream transmitter. Use the word aligner block to align the byte boundary with the first /K28.5/ 10-bit comma character in the serial data stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|              | <ul> <li>Implement a pattern detector module in the word aligner block using data realignment (bit-slip) circuitry in the LVDS hard macro. The data realignment (bit-slip) circuit realigns the data by inserting bit latencies into the serial stream.</li> <li>An optional rx_channel_data_align port controls the bit insertion of each receiver, which is independently controlled from the internal logic. The data slip one bit for every pulse on the rx_ channel_data_align signal. Follow these requirements for the rx_channel_data_align signal:</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                |

|              | <ul> <li>The minimum low time between pulses is one period of the parallel clock.</li> <li>The minimum pulse width is one period of the parallel clock in the logic array.</li> <li>This signal is an edge-triggered signal.</li> <li>Valid data is available two parallel clock cycles after the rising edge of the rx_channel_data_align signal.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | <ul> <li>After byte boundary alignment is fixed using the bit-slip module, your pattern detector module checks for the standard patterns and sends the data to synchronize the state machine.</li> <li>Implement the SGMII synchronization state machine according to the IEEE 802.3 specification. Synchronization of the state machine is for hysteresis purpose.</li> <li>For SGMII implementation, set the programmable bit rollover point at 10. The data realignment circuit can have up to 11 bit-times of insertion before a rollover occurs. An optional status port, rx_cda_max, is available to the FPGA fabric from each channel to indicate the time when the preset rollover point is reached.</li> <li>Synchronization is achieved when the receiver detects three consecutive ordered sets. An ordered set defined for synchronization is a / K28.5/ comma followed by any odd number of valid /Dx.y/ code where /Dx.y/ denotes any valid data code group.</li> </ul> |

| Block                       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Elastic FIFO (rate matcher) | In GbE, the rate matcher compensates up to $\pm 100$ ppm (a total of 200 ppm) frequency difference between the upstream transmitter and receiver.                                                                                                                                                                                                                                                                                            |

|                             | <ul> <li>The write port of the rate matcher FIFO in each LVDS receiver channel is clocked by its forwarded clock (rx_divfwdclk).</li> <li>The read port is clocked by the LVDS low-speed parallel clock output of the PLL.</li> </ul>                                                                                                                                                                                                        |

|                             | In accordance with IEEE 802.3 specification, the rate matcher logic must insert or delete /I2/ (idle ordered sets) to or from the rate matcher FIFO during the interframe or interpacket gap (IFG or IPG). If the autonegotiation feature is implemented as part of the system, the rate matcher must insert/delete the first two bytes of the /C2/ (configuration ordered sets) in addition to the insertion/deletion of /I2/ ordered sets. |

| 8B/10B Encoder              | <ul> <li>In GbE, the 8B/10B decoder clocks in 10-bit data from the rate matcher and decodes it into 8-bit data.</li> <li>The 8-bit decoded data is fed to upper layer logic.</li> <li>Implement the 8B/10B decoder according to the IEEE 802.3 specification.</li> </ul>                                                                                                                                                                     |

### Figure 9: Receiver Bit Reversal Block

This figure shows the receiver bit reversal block functionality for 10-bit wide data.

# **Programmable V<sub>OD</sub> and Programmable Pre-Emphasis**

You can use the programmable  $V_{OD}$  and programmable pre-emphasis features in Altera FPGAs to optimize the SGMII interface. These features provide advantages in driving serial data in chip-to-chip or backplane applications.

You can assign the programmable  $\rm V_{OD}$  and programmable pre-emphasis settings using the Quartus II Assignment Editor.

SGMII Interface Implementation Using Soft CDR Mode of Altera FPGAs

#### Soft-CDR Jitter Tolerance for SGMII Interface

**Related Information**

- High-Speed Differential I/O Interfaces and DPA in Stratix V Devices

- High Speed Differential I/O Interfaces with DPA in Stratix IV Devices

- High-Speed Differential I/O Interfaces with DPA in Stratix III Devices

- High-Speed Differential I/O Interfaces and DPA in Arria V Devices

- High-Speed Differential I/O Interfaces and DPA in Arria II Devices

# Soft-CDR Jitter Tolerance for SGMII Interface

To meet the receiver jitter tolerance for 1000 Base LX/SX specification, implement passive equalization circuitry at the LVDS receiver input.

For GbE protocols, the total jitter specification consists of the following elements:

- Inter-symbol interference (ISI)

- Random jitter

To reduce ISI, implement passive equalization circuits.

### Figure 10: Receiver Soft-CDR Passive Equalizer for GbE

This figure shows the passive equalization circuit at the LVDS receiver input pins for the GbE protocol. The circuit uses 100  $\Omega$  on-chip termination (OCT).

### Table 8: GbE 1000BASE-CD Passive Equalizer Parameters

This table lists parameter values that Altera recommends for the GbE 1000BASE-CD passive equalizer.

| Parameter | Recommended Value |

|-----------|-------------------|

| R1        | 35 Ω              |

| R2        | 15 Ω              |

| С         | 30 pF             |

16

Altera provides the Early Power Estimator (EPE) software—a tool for power estimation in the early design phase. Perform a power assessment using the EPE software to calculate approximate power consumption values for your design.

- Power dissipation also depends on the device selected for the implementation.

- Core dynamic power consumption involves total power consumption the following modules:

- • Clock network

- PLL

- LVDS transmitter and receiver hard macros

- FPGA fabric

In the following example, the PCS logic per channel in the FPGA fabric implementation is assumed to use approximately 500 ALUTs:

- Transmitter PCS—includes the 8B/10B encoder and transmitter bit-slip.

- Receiver PCS—includes the receiver bit reversal, word aligner, elastic FIFO, and 8B/10B decoder.

# Table 9: Approximate Power Consumption Example for 24-Channel SGMII Physical Layer Design ImplementedUsing Soft-CDR Mode

The power consumption values in this table were calculated using the EPE software. Actual power consumption values will vary depending on your design.

| Power Consumption Type | Consumption Value (mW) |

|------------------------|------------------------|

| Core static power      | 632                    |

| Core dynamic power     | 460                    |

| I/O power              | 940                    |

| Total power            | 2032                   |

#### **Related Information**

PowerPlay Early Power Estimators (EPE) and Power Analyzer

# Example Implementation of SGMII Interface Using Soft-CDR

The LVDS specifications of Altera FPGA comply with the SGMII specifications. For Ethernet application, Altera implements a complete solution using the Triple-Speed Ethernet MegaCore with the PMA, PCS, and MAC.

### Figure 11: Altera Triple-Speed Ethernet MegaCore Solution

This diagram shows an example SGMII system implemented on an Altera evaluation board with the Altera Triple-Speed Ethernet MegaCore. The Triple-Speed Ethernet MegaCore uses an LVDS hard macro configured as soft-CDR.

#### **Related Information**

#### Altera Worldwide Sales Support

For more information about the Altera Triple-Speed Ethernet MegaCore, contact the Altera sales team.

# **Document Revision History**

| Date          | Version    | Changes                                                                                                                                                                                                                                |

|---------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| October 2013  | 2013.10.17 | <ul> <li>Rewritten and restructured document to improve clarity and speed of reference.</li> <li>Added topics about implementing passive equalization circuitry to meet receiver jitter tolerance for SGMII implementation.</li> </ul> |

| December 2012 | 2.1        | Added support for Arria V devices.                                                                                                                                                                                                     |

**Altera Corporation**

| Date         | Version | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| January 2011 | 2.0     | <ul> <li>Removed the "Introduction" heading and updated the section.</li> <li>Added information for Stratix V, Stratix IV, and Arria II.</li> <li>Added link to Cisco's SGMII specification document.</li> <li>Updated the labels of the AC coupled, 1.25 Gbps links in Figure 1 and Figure 2.</li> <li>Updated the "I/O Standards Interoperability" section.</li> <li>Replaced previous Table 1 and Table 5 with links to relevant documents.</li> <li>Added links to relevant Stratix V, Stratix IV, and Arria II documents.</li> <li>Simplified the "LVDS Transmitter and Receiver (Soft-CDR)", "Configuring the ALTLVDS Transmitter and Receiver for SGMII Implementation", "Programmable VOD and Pre-Emphasis", and "Results" sections.</li> <li>Removed all figures from the simplified sections except Figure 10 (previously Figure 22).</li> <li>Added new Table 1 and Table 2.</li> <li>Removed "Referenced Documents" section.</li> <li>Text edits throughout the document.</li> </ul> |

| March 2008   | 1.0     | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |