# **Preface**

Lin Chao

Editor

Intel Technology Journal

This Q4'97 issue of the *Intel Technology Journal* focuses on innovations in memory chips and on better-yielding manufacturing techniques.

The first two papers are written by the co-inventors of Intel StrataFlash<sup>TM</sup> memory. Intel's engineers produced the first flash memory product that could store multiple bits of digital information in one memory cell. Specifically, they gave us "2x the bits in 1x the space," and at a much lower cost.

The road to success for StrataFlash memory was not without its trials and tribulations. Staffing and development resources were minimal, and at one time, the project was even shut down for a year. In the end, however, the engineers triumphed and proved that StrataFlash memory worked and could be produced reliably. It can be used in a variety of different applications: memory cards, resident code and file storage, digital imaging, and audio storage mediums. It is one of Intel's strategic assets.

The third and fourth papers in this issue describe redundancy, the technique of using spare array elements in SRAM memory to replace elements that have tested defective. A mathematical model for redundancy is described in the third paper. The second-level cache packaged in the Pentium®Pro processor is one of the first devices at Intel to use redundancy, and its usage is outlined in the fourth paper in this issue. The fifth paper introduces a new PROM element compatible with CMOS logic processes.

# **Intel StrataFlash Memory Technology Overview**

Greg Atwood, Flash Technology and Manufacturing, Santa Clara, CA, Intel Corp. Al Fazio, Flash Technology and Manufacturing, Santa Clara, CA, Intel Corp. Duane Mills, Memory Components Division, Folsom, CA, Intel Corp. Bill Reaves, Memory Components Division, Folsom, CA, Intel Corp.

Index words: StrataFlash, MLC, flash, memory

#### **Abstract**

The Intel StrataFlash<sup>TM</sup> memory technology represents a cost breakthrough for flash memory devices by enabling the storage of two bits of data in a single flash memory transistor. This paper will discuss the evolution of the two bit/cell technology from conception to production.

The flash memory business has grown from about \$50M in 1987 to roughly \$2.5B in 1997 due to its unique mix of functionality and cost. Flash memory devices are now found in virtually every PC and cellular phone and are one of the key components of the emerging digital imaging and audio markets.

Cost per bit reduction of flash memory devices has been traditionally achieved by aggressive scaling of the memory cell transistor using silicon process-scaling techniques such as photolithography line width reduction. In an attempt to accelerate the rate of cost reduction beyond that achieved by process scaling, a research program was started in 1992 to develop methods for the reliable storage of multiple bits of data in a single flash memory cell. The Intel StrataFlash two bit/cell memory technology is the first output of the multi-bit per cell storage effort. By storing two bits in a single memory transistor, the memory cell area is effectively cut in half allowing the storage of twice as much data in the same area as the standard single bit per cell technology.

This paper provides insight into the Intel StrataFlash memory technology development effort. It discusses the evolution of the two bit/cell capability from conception to production and the challenges that were successfully overcome to produce a high-quality product compatible with the standard single bit per cell devices. This paper also presents examples that showcase the benefits of the current Intel StrataFlash memory devices and discusses some of the driving forces for high density flash memory.

## Introduction

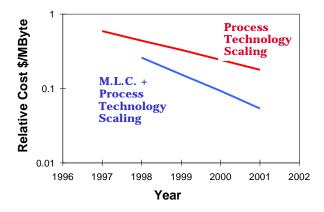

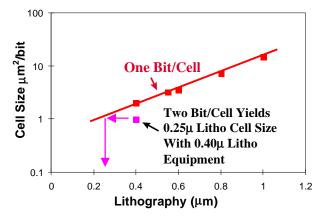

History has shown that as the price of memory drops and the density increases, the application usage and demand for that memory will increase. The cost for semiconductor memories (i.e., DRAM, SRAM, ROM, and flash) is largely determined by the amount of silicon area it takes to store a data bit of information. As with other semiconductor memories, flash memory, which retains its data even when the power is removed, achieves higher density and lower cost through traditional silicon process scaling techniques, such as feature size reduction. To build on process scaling, a concept called Multi-Level-Cell (M.L.C.) technology was introduced. This technology lowers the cost by enabling the storage of multiple bits of data per memory cell thereby reducing the consumption of silicon area. The two bit/cell Intel StrataFlash memory technology provides a cost structure equivalent to the next generation of process technology while using the current generation of process technology Figure 1 illustrates the substantial acceleration of the rate of cost reduction possible with M.L.C.

Figure 1: Accelerated cost reduction using M.L.C.

# **Introduction to Flash Memory**

A discussion of the Intel StrataFlash memory and technology first requires a brief overview of the standard ETOX<sup>TM</sup> flash memory technology and its use. Flash memory is a member of the non-volatile class of memory devices, storage devices that maintain their data in the absence of applied power. The ETOX technology is the predominate flash technology, representing over 70% of flash memory shipments. Data is entered into the flash memory on a bit, byte, word, or page boundary through an operation called programming. Once data is entered into the device it will remain, regardless of the presence or absence of power. Data is cleared from the flash memory with an erase operation. The contents of the flash memory are erased on a block boundary, where a block size can be anywhere from 8Kbits to 1Mbit depending on the product design.

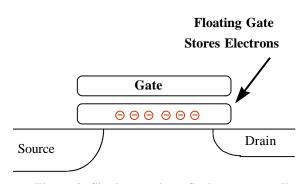

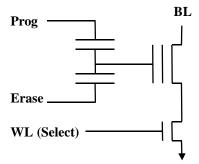

The ETOX flash memory storage element, or memory cell, shown in Figure 2, is a single transistor with the addition of an electrically isolated polysilicon floating gate capable of storing charge (electrons). The amount of stored charge modifies the behavior of the memory cell transistor. This change in transistor behavior is translated into stored data: the presence of charge is interpreted as data "0;" the absence of charge is interpreted as data "1." The single transistor memory cell results in a small cell size, and thus a small amount of silicon area is consumed for the storage of one bit of data, resulting in low cost.

Figure 2: Single transistor flash memory cell

# Flash Memory Market

The combination of non-volatility, electrical alterability, and low cost is attractive to small systems that do not have access to a continuous power source such as battery-powered devices. For example, almost every cellular phone sold today contains a flash memory device. This device stores the program that the cellular phone uses to communicate over the wireless network and interact with

the phone user. In some cases, the memory device also stores incoming messages, much like a cellular digital answering machine. The non-volatility of flash ensures that, when you remove the battery from the phone, it will not forget how to communicate nor will it loose any of your messages.

The unique combination of features provided by flash memory has enabled the market for these devices to grow from less than \$50M in 1987 to over \$2.5B in 1997. Flash memory devices are found in over 90% of PC's, over 90% of cellular phones, and over 50% of modems. Applications are as diverse as airline flight recorders, medical recording equipment, digital answering machines, arcade games, printers, and network routers. Flash memory is a key component of the emerging digital imaging and audio markets where it serves as the digital "film" or digital "tape."

# The Pursuit of Lower Cost Memory

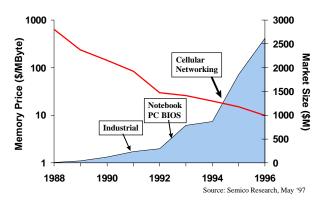

The growth of the flash memory market has been driven by a continual increase in density and reduction in cost, enabling new applications to emerge and further fuel the demand for more flash. Figure 3 illustrates the rapid increase in the flash market size driven by the reduction in memory price. As the price of memory was reduced, new applications for flash memory emerged (some examples are shown in Figure 3) fueling further market growth.

Figure 3: Flash memory price and market size

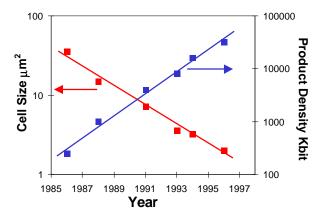

Traditionally, cost reduction and density increase for flash memory has been driven by process scaling in the same way as other semiconductor memory devices such as DRAMs and SRAMs. As the ability of the semiconductor manufacturing process equipment improves, smaller features can be resolved on the silicon wafer resulting in a smaller memory cell and thus more bits in a given amount of silicon area. More bits in a given silicon area result in higher density memories and lower cost per bit. Using the technique of process

technology scaling, the flash memory cell size has been reduced by 18 times in the past 10 years as shown in Figure 4. The reduced cell area combined with increases in the size of the memory product (brought about by improved manufacturing techniques and yields) has resulted in a product density increase of over 100 times in the same 10-year period.

Figure 4: Cell area and product density in time

The flash memory cell is a single transistor; one bit of data is stored in one transistor. By comparison, a SRAM memory cell requires six transistors (or four transistors and two resistors), a DRAM memory cell requires one transistor and one capacitor, and an  $E^2PROM$  cell requires two transistors.

A single transistor has been generally considered the smallest practical unit for the storage of a bit of data. In 1992, the Intel flash development team began a research effort to reduce the amount of silicon required to store a bit of data to a fraction of a transistor through the storage of more than one bit in a single memory cell transistor. The Intel StrataFlash two bit/cell memory technology recently introduced is the first achievement of this multibit per cell storage effort. It provides the cost structure of the next-generation process technology while using the current generation process technology equipment (see Figure 5).

Figure 5: Cell area as a function of lithography

# The Multi-Bit Storage Breakthrough: Intel StrataFlash Technology

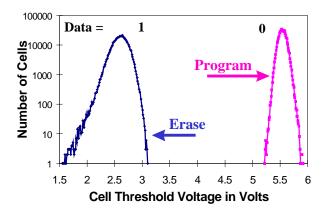

As discussed earlier, the flash memory device is a single transistor that includes an isolated floating gate. floating gate is capable of storing electrons. behavior of the transistor is altered depending on the amount of charge stored on the floating gate. Charge is placed on the floating gate through a technique called programming. The programming operation generates hot electrons in the channel region of the memory cell transistor. A fraction of these hot electrons gain enough energy to surmount the 3.2eV barrier of the Si-SiO<sub>2</sub> interface and become trapped on the floating gate. For single bit per cell devices, the transistor either has little charge (<5,000 electrons) on the floating gate and thus stores a "1" or it has a lot of charge (>30,000 electrons) on the floating gate and thus stores a "0." When the memory cell is read, the presence or absence of charge is determined by sensing the change in the behavior of the memory transistor due to the stored charge. The stored charge is manifested as a change in the threshold voltage of the memory cell transistor. Figure 6 illustrates the threshold voltage distributions for a half million cell (1/2Mc) array block. After erasure or programming, the threshold voltage of every memory cell transistor in the 1/2Mc block is measured, and a histogram of the results is presented. Erased cells (data 1) have threshold voltages less than 3.1v, while programmed cells (data 0) have threshold voltages greater than 5v.

Figure 6: Single bit/cell array threshold voltage histogram

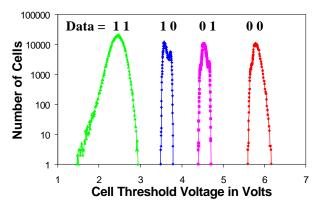

The charge storage ability of the flash memory cell is a key to the storage of multiple bits in a single cell. The flash cell is an analog storage device not a digital storage device. It stores charge (quantized at a single electron) not bits. By using a controlled programming technique, it is possible to place a precise amount of charge on the floating gate. If charge can be accurately placed to one of four charge states (or ranges), then the cell can be said to Each of the four charge states is store two bits. associated with a two-bit data pattern. Figure 7 illustrates the threshold voltage distributions for a 1/2Mc block for two bit per cell storage. After erasure or precise programming to one of three program states, the threshold of each of the 1/2Mc is measured and plotted as a histogram. Notice the precise control of the center two states, each of which is approximately 0.3v (or 3,000) electrons in width.

Figure 7: Two bit/cell array threshold voltage histogram

Higher bit per cell densities are possible by even more precise charge placement control. Three bits per cell requires eight distinct charge states; four bits per cell requires sixteen distinct charge states. In general, the number of states required is equal to  $2^N$  where N is the desired number of bits.

The ability to precisely place charge on the floating gate and at some later time sense the amount of charge that was stored has required substantial innovations and extensive characterization and understanding of cell device physics, memory design, and memory test. These innovations are discussed in detail in the paper entitled "Intel StrataFlash Memory Technology Development and Implementation" also published in this issue of the Intel Technology Journal.

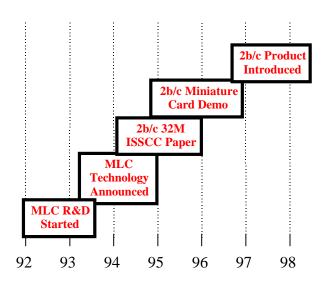

# **Evolution of the Intel StrataFlash Memory Technology Development**

This section will outline the development of the Intel StrataFlash memory technology from conception in 1992 to productization in 1997, highlighting the key innovations along the way. The 64Mbit product recently introduced differs markedly from the 1992 view of what a two bit/cell product might look like. The learning that has occurred over the past four years has enabled the development of a two bit/cell memory device that functionally looks almost identical to a one bit/cell device, far exceeding the capability that was considered possible when the development program started. Figure 8 shows the timeline of the major Intel StrataFlash memory technology development milestones.

Figure 8: Intel StrataFlash development program

The Multi-Level-Cell (M.L.C.) Concept

Storage of analog data in a floating gate memory device is not a new concept. It was suggested as early as 1971 for EPROM devices<sup>[1]</sup> and was implemented on E<sup>2</sup>PROM devices for use in neural networks, voice recorders, and toys as early as 1982. These analog storage applications can tolerate a high error rate and thus do not place stringent requirements on the memory reliability or accuracy. Neural networks are, by their nature, fault tolerant. Voice storage and simple talking toys can tolerate a few lost bits without any audible impact. These high error rate, lossy memories are generally not usable for mainstream digital storage and thus have had limited acceptance. The goal of the M.L.C. program was to produce a two bit/cell digital storage technology capable of penetrating the larger non-volatile memory market, enabling the growth of new digital flash memory applications.

# The 1992 View of M.L.C.

In the early 1990s, flash memory was considered as a potential replacement for hard disks at lower densities for applications that require small, rugged, and low-power storage. One of the main issues for use of flash in this application was the high cost of the flash memory as compared to that of magnetic storage. A lower cost flash memory was required. The hard disk requirements are much relaxed over silicon memory due to the inclusion of error correction in the hard disk subsystem, the block transfer of data (no byte access), and the relative low read performance. Multi-level cell technology appeared to be an ideal solution for the solid state disk, addressing the lower cost through two bit/cell (and later three or four bit/cell) technology. The use of error correction, and the large block transfer of data in the solid state disk would address any reliability issues with multi-level storage. The Intel M.L.C. program was thus started with a goal of a high-density, low-cost, solid-state disk.

The basic techniques for accurate charge placement and sensing were developed in the lab and implemented into a 32Mbit silicon test chip. During this time frame, the three major challenges for multi-bit storage were identified:

- Precise Charge Placement: The flash memory cell programming must be very accurately controlled, requiring a detailed understanding of the physics of programming as well as the control and timing of the voltages applied to the cell.

- Precise Charge Sensing: The read operation of a M.L.C. memory is basically an analog to digital conversion of the analog charge stored in the memory cell to digital data- a concept new to memory devices.

• Stable Charge Storage: Meeting the data retention goals would require the stored charge to be stable with a leakage rate of less than one electron per day.

The 32Mbit test chip clearly demonstrated the ability to

The 32Mbit test chip clearly demonstrated the ability to store multiple bits in a single cell. Based on the functionality of this device, the M.L.C. technology was announced in 1994.

## The 'First' M.L.C. 'Product'

With the knowledge gained from the 32Mbit test chip, the first attempt at a two bit/cell storage product was started. This device was aimed at the solid-state disk goal. The solid-state disk system would include error correction and would generate non-standard voltages to interface to the two bit/cell memory device. A special DC to DC voltage converter was commissioned that would generate 12v+1% and 5.5+1% from a 3v+10% external supply. The M.L.C. part required these precise supply voltages to perform the accurate program and read operations. An error corrector was designed to be integrated with the other control logic of the solid state disk. A paper based on this 32Mbit M.L.C. memory was presented at the prestigious International Solid State Circuits Conference (ISSCC) in 1995<sup>[2]</sup>, winning the best paper of the conference award. The 32Mbit device became the workhorse for the M.L.C. technology development effort, demonstrating the ability of M.L.C. to meet Intel's stringent reliability requirements and to produce yield equivalent to single bit/cell flash memories. It was also used to develop the M.L.C. testing and to debug the manufacturing process for test and packaging.

# The Question of Reliability

The primary concern for M.L.C. was the reliability of the storage of the multiple charge states. Charge states would be separated by a few thousand electrons in an M.L.C. device, and a loss of one electron per day from the floating gate could result in a bit error after ten years of storage. To understand the detailed physics of charge storage, a large experiment was started to monitor the charge storage behavior of 200 billion cells (2x10<sup>11</sup> cells). This massive experiment could resolve changes in the stored charge of as small as 100 electrons on all of the cells under evaluation. The rate of charge loss was accelerated through the use of elevated temperatures. This experiment, which was started in early 1994, is still running today with an accumulated high temperature stress time of over three years, representing over 50 years at normal operating temperatures. The knowledge gained and models developed based on this experiment have resulted in changes to the design of both the product and the process, allowing removal of the error correction requirement for two bit/cells. This data fundamentally changed the direction of the multi-bit storage program.

# **Removing the Constraints**

Toward the end of 1995, the M.L.C. project had grown from a small research effort to a full blown program. Almost two years worth of reliability data was showing excellent performance indicating that the error corrector was not required. The 32Mbit device had demonstrated the viability of the circuit techniques and the device physics used for the precision program and read operations. Moreover, the yield was looking excellent, and the manufacturing issues were understood. Test circuits had demonstrated the ability to provide the required voltages and voltage regulation on the memory chip, eliminating the need for the external DC to DC converter. It became clear that the project could accomplish much more than the initial vision of a solid state disk. The team believed that it was possible to remove the two major requirements initially envisioned for M.L.C.: error correction and precision external power supplies. The solid state disk market, while developing, had not reached the desired volume levels. The decision was made to not take the 32Mbit device to production and focus on the design of an M.L.C. two bit/cell part with functionality substantially equivalent to the standard one bit/cell products.

# The 1997 View of M.L.C.

The first two bit/cell Intel StrataFlash memory device was introduced in September of 1997, a 64Mbit device. This device has functionality that is largely equivalent to the standard one bit/cell flash products. A highlight comparison of the Intel StrataFlash memory features to an Intel 16Mbit single bit/cell product is shown in Figure 9

|                                                     | 1b/c Flash Intel StrataFlash <sup>t</sup> Memory 2b/c Memory |               |        |

|-----------------------------------------------------|--------------------------------------------------------------|---------------|--------|

| Density                                             | 16Mbit                                                       | 32Mbit        | 64Mbit |

| Read Speed                                          | 100 ns                                                       | 120 ns 150 n  |        |

| Block Size                                          | 64KByte                                                      | 128KByte      |        |

| Architecture                                        | x8                                                           | x8 / x16      |        |

| V <sub>cc</sub> Power Supply (+/-10%)               | 5V                                                           | 5V            |        |

| V <sub>pp</sub> (Program/Erase Voltage)             | 5V or 12V                                                    | 5V            |        |

| Effective Write Speed                               | 6 μS/Byte                                                    | 6 μs/Byte     |        |

| I <sub>ccr</sub> (Read Current)                     | 35 mA                                                        | 55 mA         |        |

| I <sub>ppw +</sub> I <sub>ccw</sub> (Write Current) | 75 mA                                                        | 90 mA         |        |

| Endurance                                           | 100,000 Cycles                                               | 10,000 Cycles |        |

| Operating Temperature                               | Extended                                                     | Comercial     |        |

Figure 9: Comparison of 1b/c and 2b/c product features

Read performance is in line with expectations for memories of 32Mbit and 64Mbit densities with about a 20% increase in read access time for a doubling of memory density. Two bits/cell doubles the erase block size as compared to one bit/cell since each cell now stores twice as much data. The power supply is maintained at the 5v industry standard. The two bit/cell write performance is maintained equivalent to one/bit cell, even with the more complex (and slower) precision write algorithm, through the use of an eight-byte write buffer and a higher write bandwidth into the array. The 10,000 erase/write endurance specification is more than acceptable for virtually all flash applications and easily justified by the reduced cost.

The 64Mbit device integrates all of the knowledge gained from the two previous test vehicles and advances beyond them with the introduction of precision internal voltage regulation and internal test capability. The first silicon wafer out of the manufacturing line was fully functional, and the program is on track for volume shipments. The 64Mbit two bit/cell Intel StrataFlash memory is just 5% larger than the 32Mbit one bit/cell device on the 0.4 $\mu$  ETOX flash memory process, delivering on the promise of 2x the bits in 1x the space and setting a new cost paradigm for flash memory devices. A photomicrograph of the 64Mbit Intel StrataFlash memory is shown in Figure 10.

Figure 10: The Intel StrataFlash 64Mbit memory

## Examples of Intel StrataFlash Memory Usage

Intel StrataFlash memory is finding acceptance in a wide variety of applications that all share a common need for high density and low cost. Applications evaluating the use of Intel StrataFlash memory include small office voice-mail PBX systems to store incoming messages, network routers to store operating programs, digital cameras for digital image "film," digital voice recorders for digital audio "tape," Windows\* CE hand-held computers for storage of programs and data, and set-top boxes for storage of programs and data. As for the goal of replacing hard disks in small, low-power, or rugged systems, Intel StrataFlash memory will enable solid state

disks to be cheaper than hard disks for capacities of 32MByte and lower.

## The Future of M.L.C.

With two bits per cell well along the way to mainstream production, attention turns to the prospects of even higher bit per cell densities. It is now recognized that the Intel ETOX flash memory cell and array structure is ideally suited to the storage of multiple bits per cell due to its simple direct access array architecture and proven high volume manufacturability. The direct access memory array allows the precise control of the cell voltages required to reliably and reproducibly place precise amounts of charge on the floating gate. The well controlled, high yielding ETOX process technology ensures that sufficient process margins exist for the more stringent M.L.C. requirements. Three bits per cell storage has been demonstrated in the laboratory, achieving state widths of less than 0.15v on a 48Mbit test chip.

## Conclusion

The concept of multi-level storage using an ETOX flash memory cell transistor has been demonstrated. This concept builds on traditional semiconductor process scaling, providing the cost structure of the nextgeneration silicon process technology with the current generation of silicon process equipment. The evolution of the multi-level-cell development from concept in 1992 to production in 1997 has required many innovations in the areas of device physics, circuit design, and product test. The combination of precisely controlled on-chip voltages and timing, the direct access ETOX flash memory array architecture, and a highly manufacturable silicon process technology has resulted in a two bit/cell memory device largely identical to the industry standard one bit/cell flash memory. The Intel StrataFlash memory sets a new cost paradigm for the flash industry.

\*All other brands and names are the property of their respective owners.

# Acknowledgments

A program of this scope requires many dedicated hours by many creative individuals. The authors would like to thank the members of the Intel StrataFlash memory development team for the effort leading to the world's first two bit/cell ETOX flash memory product.

## References

[1]Frohman-Bentchowsky, Floating Gate Solid State Storage Device and Methodology for Charging and

- Discharging Same, U.S. Patent #3,755,721, Aug. 28, 1973.

- [2] Bauer, M., et. al., "A Multilevel-Cell 32Mb Flash Memory," Technical Digest IEEE International Solid State Circuits Conference, 1995, pp. 132,133.

# **Authors' Biographies**

Greg Atwood is an Intel Fellow and is the director of Flash Memory Architecture. He received an M.Sc. degree in Physics from Purdue University in 1979 and joined Intel the same year. He has worked on numerous technology development programs including Logic, SRAM, EPROM, E²PROM, Flash, and Multi-Level Flash. He was the program manager for the Intel StrataFlash memory development program responsible for all aspects of the project. He holds 20 patents covering a wide range of technical topics. Greg is presently responsible for next-generation Flash and Intel StrataFlash memory technologies. His e-mail address is greg\_atwood@ccm.sc.intel.com.

Al Fazio is a principal engineer in Flash Technology development. He received a B.Sc. in Physics from the State University of New York at Stony Brook in 1982 and joined Intel the same year. He has been involved in development programs such as SRAM, EPROM, E<sup>2</sup>PROM, NVRAM, and Flash Memories. He was responsible for the technology development of the Intel StrataFlash memory. He holds more than a dozen patents and has authored or co-authored several technical papers. He is presently responsible for Intel's Multi-Level-Cell and Advanced Flash Memory Cell development and currently serves as general chairman of the IEEE Non-Volatile Semiconductor Memory Workshop. His e-mail address is al fazio@ccm.sc.intel.com

Duane Mills is the Intel StrataFlash Memory Design Engineering Manager. He received a B.Sc. in Electrical Engineering from Purdue University in 1984 and joined Intel the same year. He has worked on numerous EPROM and Flash memory designs during the past 13 years. Mr. Mills was the design manager for the first Intel StrataFlash memory product and is currently responsible for the definition and design of the next-generation Intel StrataFlash product. His e-mail address is duane\_r\_mills@ccm.fm.intel.com.

Bill Reaves is the Intel StrataFlash Memory Product Engineering Manager. He received a B.Sc. in Electrical and Computer Engineering from U.C. Santa Barbara in 1984 and joined Intel the same year. He has been involved in numerous non-volatile memory projects, including the test development and manufacturing start-up of Intel's first flash memories. He is currently the Product Engineering manager for the Intel StrataFlash Memory program and the project manager for the initial product line. His e-mail address is bill\_t\_reaves@ccm.fm.intel.com.

# Intel StrataFlash<sup>TM</sup> Memory Technology Development and Implementation

Al Fazio, Flash Technology Development and Manufacturing, Santa Clara, CA. Intel Corp. Mark Bauer, Memory Components Division, Folsom, CA. Intel Corp.

Index words: StrataFlash, MLC, flash, memory.

## **Abstract**

This paper will review the device physics governing the operation of the industry standard ETOX<sup>TM</sup> flash memory cell and show how it is ideally suited for multiple bit per cell storage, through its storage of electrons on an electrically isolated floating gate and through its direct access to the memory cell. The device and reliability physics aspects of the three key technology features of multiple-levels-per-cell (M.L.C.): precise placement, precise charge sensing, and precise charge retention are discussed. The mixed signal design implementation of these features is reviewed along with challenges for low periphery circuit overhead and standard flash memory product performance. Lastly, process manufacturing aspects are reviewed and it is shown how Intel StrataFlash<sup>TM</sup> memory is manufactured on the same process flow and at the same high yields as standard flash memory.

# Introduction

The concept of M.L.C. is ideally suited to the flash memory cell. The cell operation is governed by electron charge storage on an electrically isolated floating gate. The amount of charge stored modulates the flash cell's transistor characteristic. M.L.C. requires three basic elements: (1) Accurate control of the amount of charge stored, or placed, on the floating gate such that multiple charge levels, or multiple bits, can be stored within each cell, an operation called placement; measurement of the transistor characteristics to determine which charge level, or data bit, is stored, an operation called sensing; and (3) accurate charge storage, such that the charge level, or data bit, remains intact over time, an operation called retention. These elements are achieved by exploiting stable device operation regions and by the direct cell access of the ETOX flash memory array.

# Flash Cell Structure and Operation

An explanation of M.L.C. first requires a review of the flash memory cell. The ETOX flash memory cell and products<sup>[1]</sup> have a long manufacturing history, having evolved in the late 1980's from EPROMs, which had been an industry standard from the early 1970's.

#### **Cell Structure**

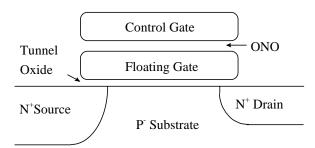

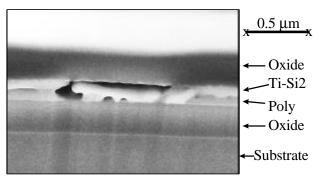

Figure 1: ETOX flash memory cell cross section

Figure 1 shows a cross-sectional view of a flash cell. It consists of an N-channel transistor with the addition of an electrically isolated poly-silicon floating gate. Electrical access to the floating gate is only through a capacitor network of surrounding SiO<sub>2</sub> layers and source, drain, transistor channel, and poly-silicon control gate terminals. Any charge present on the floating gate is retained due to the inherent Si-SiO<sub>2</sub> energy barrier height, leading to the non-volatile nature of the memory cell. Characteristic of the structure is a thin tunneling oxide (~100Å), an abrupt drain junction, a graded source junction, ONO (oxidenitride-oxide) inter-poly oxide, and a short electrical channel length (~0.3µ). Because the only electrical connection to the floating gate is through capacitors, the flash cell can be thought of as a linear capacitor network with an N-channel transistor attached. capacitance of the cell (C<sub>TOT</sub>) is equal to the additive

capacitance of the network. For convenience, coupling ratio terms, which are defined as the ratio of terminal voltage coupled to the floating gate, can be defined as follows:

GCR =control gate coupling ratio,

DCR = drain coupling ratio, and

SCR = source coupling ratio.

Therefore, a change in control gate voltage will result in a change in the floating gate voltage,  $\Delta V_{FG} = \Delta V_{CG} *GCR$ . The basic equation for the capacitor network is

$$V_{FG}=Q_{FG}/C_{TOT} + GCR*V_{CG} + SCR*V_{SRC}+DCR*V_{DRN}$$

(1)

where  $Q_{FG}$  = the charge stored on the floating gate.

A simple first-order transistor equation of drain current says

$$I_{D} = G_{M} * (V_{FG} - V_{CG} - V_{DRN}/2) * V_{DRN}$$

(2)

where  $G_M = q\mu e C_{OX} Z_E / L_E$

This equation is very inexact for the small geometry of the flash cell, but nevertheless the conclusions hold. Substituting  $V_{FG}$  of the basic coupling ratio Equation (1) into the basic transistor I-V Equation (2) leads to the conclusions that the transconductance of the transistor (and also the pre-threshold slope) degrades by GCR, while the threshold voltage,  $V_T$ , depends upon  $Q_{FG}$ , the charge stored on the floating gate. Therefore, the  $V_T$  depends upon  $Q_{FG}$ , while the I-V shape does not. Very simply, the flash cell can be thought of as a capacitor which is charged and discharged, the charge value being determined by the amplification of the transistor I-V. To give an idea of the amount of charge, every volt of cell threshold corresponds to approximately 10,000 electrons of floating gate charge.

# **Cell Operation: Programming**

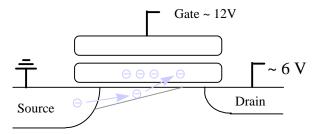

Figure 2: Cell bias conditions during programming

Programming a flash cell means that charge, or electrons, are added to the floating gate. Figure 2 shows the cell

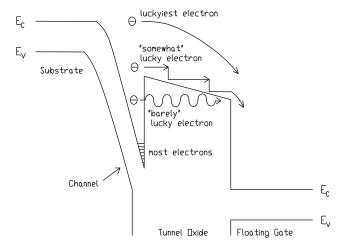

bias conditions during program operation. A high drain to source bias voltage is applied, along with a high control gate voltage. The gate voltage inverts the channel, while the drain bias accelerates electrons towards the drain. Programming a flash cell, by channel hot electrons, can be understood by use of the lucky electron model<sup>[2]</sup>, as illustrated by the energy band diagram in Figure 3. In the lucky electron model, an electron crosses the channel without collision thereby gaining 5.5-6.0eV of kinetic energy, more than sufficient to surmount the 3.2eV Si-SiO<sub>2</sub> energy barrier. However, the electron is traveling in the wrong direction. Its momentum is directed towards the drain. Prior to entering the drain and being swept away, this lucky electron experiences a collision with the silicon lattice and is re-directed towards the Si-SiO<sub>2</sub> interface, with the aid of the gate field. It has sufficient energy to surmount the barrier. However, an electron does not have to be completely lucky. It can be "somewhat lucky" or "barely lucky," making the process of programming efficient. We can observe from this model that the lateral field, determined by bias voltage, junction profiles, electrical channel length, and channel doping are important to the effectiveness of generating energetic electrons and are therefore key to the M.L.C. placement operation. Hence the abrupt drain junction and short channel length of the cell structure. After programming is completed, electrons are added to the floating gate, increasing the cell's threshold voltage. Programming is a selective operation, uniquely occurring on each individual cell.

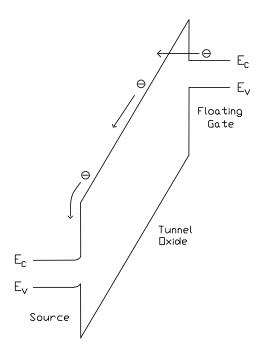

Figure 3: Energy band diagram of programming

#### **Cell Operation: Erase**

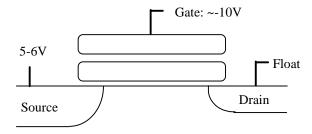

The distinguishing feature between EPROM and flash memory is the erase operation. EPROM removes electrons from the floating gate by exposure to ultra-violet light. A photon of this light source has high enough energy that if transferred to an electron on the floating gate, that electron will have enough energy to surmount the Si-SiO<sub>2</sub> energy barrier and be removed from the floating gate. This is a rather cumbersome operation requiring a UV-transmissive package and a light source. It is also rather slow and costly, often requiring the removal of the memory from the system. In flash, the contents of the memory, or charge, are removed by means of applying electrical voltages, hence to be erased in a flash, with the memory remaining in the system. The electrical erase of flash is achieved by the quantum-mechanical effect of Fowler-Nordheim Tunneling<sup>[3]</sup>, for which the bias conditions are shown in Figure 4. Under these conditions, a high field (8-10MV/cm) is present between the floating gate and the source. The source junction experiences a gated-diode condition during erase, hence the graded source junction of the cell structure. As evidenced by the energy band diagram of Figure 5, electrons tunneling through the first  $\sim 30\text{\AA}$  of the  $SiO_2$  are then swept into the source. After erase has been completed, electrons have been removed from the floating gate, reducing the cell While programming is selective to each threshold. individual cell, erase is not, with many cells (typically 64k-Bytes) being erased simultaneously.

Figure 4: Cell bias conditions during erase

Figure 5: Cell energy band diagram during erase

## Cell Operation: Read

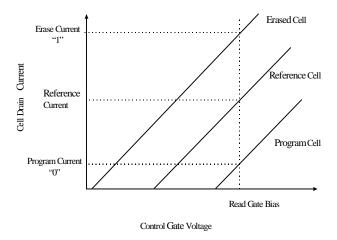

The read operation of the cell should now be apparent. Storing electrons (programming) on the floating gate ( $Q_{FG}$  < 0), increases the cell Vt. By applying a control gate voltage and monitoring the drain current, the difference between a cell with charge and a cell without charge on their floating gates can be determined (Figure 6). A sense amplifier compares the cell drain current with that of a reference cell (typically a flash cell which is programmed to the reference level during manufacturing test). An erased cell has more cell current than the reference cell and therefore is a logical "1," while a programmed cell draws less current than the reference cell and is a logical "0." The floating-gate charge difference between these two states is roughly 30,000 electrons.

Figure 6: Erase, program and reference cell I-V

## **Array Configuration**

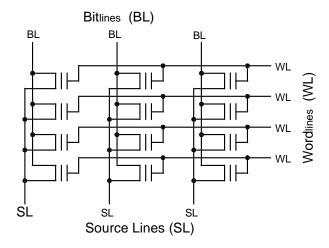

Figure 7 shows a schematic drawing of the flash memory cells in a NOR array configuration. In this configuration, cells on the same wordline, or row, share common control gates. Cells on common bitlines, or columns, share common drains, which are connected via low resistance metalization, providing direct access to each cell's drain junction. The sources for cells in the array are common. They are connected locally via common degenerately doped silicon and globally via low resistance metalization. Decoders are linked to the control gate wordlines and drain bitlines to uniquely select cells at the cross point location. The direct access to the cell in this configuration versus alternative array architectures that have parasitic resistance or devices, ensures that accurate voltages can be applied to the cell and IR drops are minimized. This is a key aspect to achieving M.L.C.

Figure 7: Array configuration

# M.L.C. Key Features

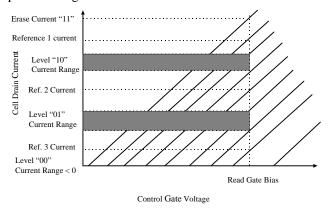

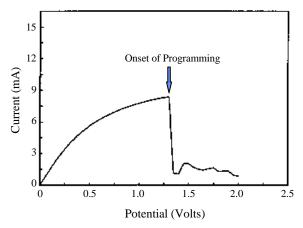

We have reviewed thus far how a one bit per cell (1B/C) flash memory operates. As can be inferred from the previous discussion, M.L.C. is simply a means by which charge on the floating gate is modulated and detected to levels lower than the 30,000 electrons described above, such that intermediate charge levels, or states, can be extracted from the cell. These states can now represent not just the simple 1B/C "1" and "0," but rather an M.L.C. representation with four distinct charge states: "11," "10," "01" and "00," or 2 bits in one cell. These four distinct levels are illustrated in the I-V curve of Figure 8. The key aspects of achieving these intermediate states, or levels, are precise charge placement, precise charge sensing, and precise charge retention.

Figure 8: Cell and reference I-V curves of 4-level 2B/C Precise Charge Placement

A comparison of Figures 6 and 8 shows that M.L.C. requires a means to control how much programming occurs within a cell. For a 1B/C product, all that is necessary is to have enough programming to change a "1" into a "0." Over-programming a cell to much higher Vt's (adding more floating gate charge) would be fine. This is not the case for M.L.C., where too much programming would cause an intermediate level to overshoot onto the next level. For instance, if a "10" was desired, but a cell was over programmed, a "01" might occur, leading to erroneous data. Therefore, a method of controlling precisely how much charge is transferred to the floating gate is required. Enough charge is needed to reach a state level without overshooting the desired level.

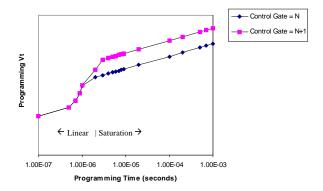

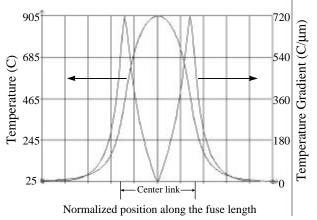

Figure 9: Programming threshold vs. time curve

To gain insight into how such precise control can be obtained, let's take a deeper look into the flash cell's programming characteristics. Figure 9 shows how the flash cell's Vt changes as a function of log-time under two different bias conditions. Two regions of operation are shown: linear and saturation, so-called because the linear region is linear when plotted in linear time, and the saturation region is where the cell Vt changes little with time, analogous to a MOS transistor I-V curve. Note also that in the linear region, the control gate voltage has little influence on the rate of programming, while in the saturation region, the control gate voltage has a strong dependence upon the saturated Vt. A characteristic of Figure 9 is that the flash cell programming slows as more charge is added to the floating gate. The reason for this behavior is that when in the linear region, energetic electrons, near the drain, are attracted to the floating gate. As programming progresses, the floating gate (which is coupled to the control gate and drain biases as governed by Equation 1) becomes charged more negatively, until it eventually reaches the same bias potential as the drain voltage. At this point, the energetic electrons become repelled by the floating gate charge. Programming slows, as near-drain electrons must tunnel through the SiO<sub>2</sub> barrier, or less energetic mid-channel electrons "jump" over the barrier. The strong gate dependence results from the vertical field limitation in this region. One can also see from Figure 9 that the saturated Vt increases in a one for one fashion with an increase in the programming control gate voltage. This is a simple result of the coupling Equation (1).

Given this characteristic curve, one could devise several possible methods of controlling the charge transfer to the floating gate. These methods would have to pass the criteria of being reliable (no overshoot), controllable (simple to implement), and fast (to ensure compatibility with standard flash memory product features). Programming in the linear region while being fast is not controllable. In this region, programming Vt is

exponentially dependent upon time and the electron energy distribution (as determined by drain bias, channel length, doping profiles, etc.). Small variations will lead to large changes in the cell threshold and therefore overshoot of the desired state, thereby having a high likelihood of being unreliable. Minimization of these variations would be also difficult to implement. In the saturated region, the cell Vt simply depends upon the applied control gate voltage. Control in this region is more achievable. With ease of control, design optimization practices can be employed to achieve fast programming. This will be shown later. Therefore, to achieve speed and control, a placement algorithm that employed programming in the saturated region was developed.

This leaves us with reliability. Unlike Fowler-Nordheim Tunneling, used for programming in addition to erase in some versions of flash memories and subject to erratic programming due to the presence or absence of as few as one or two holes trapped in the oxide<sup>[4]</sup>, channel hotelectron programming has no erratic programming mechanism. The programming threshold in saturation is simply a linear function of the applied control gate voltage. Programming in this region can be forced into an unstable operating point, known as impact-ionization induced latch- $up^{[5]}$ . This is the point where an excess of holes in the silicon substrate, created by the collisions of the energetic electrons with the silicon lattice, build up to the point where the parasitic NPN transistor in the silicon substrate turns on. Proper architectural design of the silicon process flow (i.e., use of EPI silicon) can easily prevent this from happening.

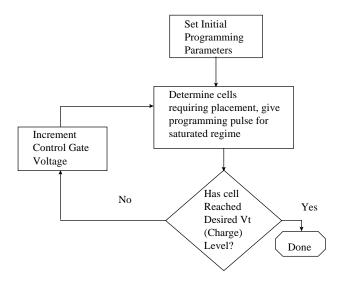

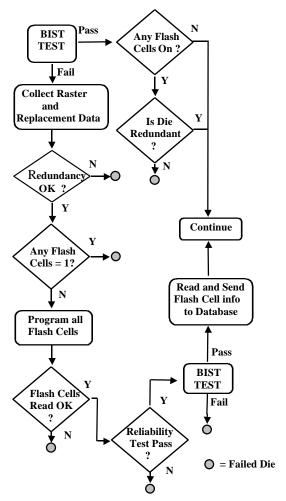

Therefore, the three success criteria are satisfied by exploiting stable device operation regions, namely programming in saturation. Now, a simple placement algorithm was chosen for implementation (outlined in the flowchart in Figure 10). The algorithm consists of the simple loop of programming in saturation, checking the cell Vt to determine if the desired state has been reached, stopping if the desired state is reached, or if not, incrementing the control gate voltage and providing an additional programming pulse and continuing in this fashion until the desired Vt has been achieved. In the Intel StrataFlash<sup>TM</sup> memory two bit per cell device, each programming pulse within the placement algorithm will transfer roughly 3,000 electrons of charge to the floating gate.

Figure 10: Placement algorithm flowchart

# **Precise Charge Sensing**

As can be seen from the flowchart in Figure 10, integral to the placement algorithm is a means of detecting whether or not the desired cell Vt has been achieved. Without a precise means of sensing the floating gate charge, precise charge placement would not be possible. A look back at Equation 2, the cell drain current-voltage relationship, gives some insight into what is required to achieve precise charge sensing. Control gate and drain voltage control and process Leff, Zeff, mobility and oxide capacitance control are important aspects of precise charge sensing. Drain voltage control is facilitated by direct access to the cell drain junction (bypassing any resistive IR drops) allowable in the ETOX NOR flash memory array architecture; and by applying a high enough drain voltage to operate in the saturated mode (normal MOS device saturated I-V, not programming saturation as previously discussed) where drain bias variations have minimal current impact. Process control is important, since the 33,554,432 memory cells contained within a single Intel StrataFlash memory 64Mbit device represent a >10 sigma variation, and is achieved by proper process architecture and manufacturing process control, derived from the ten years of manufacturing experience with flash memories. Control gate voltage control is achieved by an on-chip read regulation circuit, which is fully explained in a later section.

Flash memory has a unique feature associated with its non-volatility: the data write (placement) can occur under one condition of ambient temperature and system power supply, while the read out of data (sensing) can occur at a later date, at different ambient temperature and system

power supply. Being fundamentally a MOS transistor, the flash cell's drain current is a function of these ambient As such, the precise charge sensing is conditions. required to span wide ranges of operation. To facilitate this needed precision, the reference levels that separate charge state levels are generated by reference flash cells contained on-chip. These reference cells, whose Vt levels are precisely placed at manufacturing test under a controlled environment, will have the same tracking with temperature and power supply as the array flash cells. This contrasts to reference levels generated by other transistor types (i.e., NMOS or PMOS), which have different temperature, voltage, and process tracking than the flash memory cell. This lessens the necessary constraints on the read regulation circuitry.

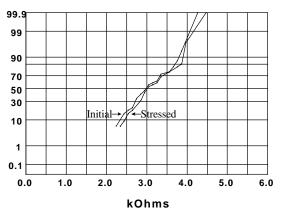

## **Precise Charge Retention**

Due to the non-volatility requirement of flash memory, it is important that any charge placed on the floating gate remain intact for extended periods of time, typically ten years. This translates to a requirement of not losing more than one electron per day from the floating gate. If electron loss occurs from even one memory cell in an array of millions, the data will be corrupted. The inherent storage capability exists due to the Si-SiO<sub>2</sub> energy barrier which traps electrons on the floating gate. The inter-polysilicon oxide (ONO film mentioned in the cell structure) is processed to maximize charge storage capabilities<sup>[6]</sup>. Under normal circumstances, the energy barrier allows charge storage for hundreds of years. conditions of trapped oxide charge, known as intrinsic charge loss<sup>[7]</sup>, which can cause one-time shifts in These shifts are rather small and are threshold. compensated for during manufacturing test. defects in the insulating oxides that can lead to charge loss are less of an issue with low-defect, high-yielding process technologies, but if still present, are screened out by the manufacturing tests. These defects are driven to low enough levels on ETOX flash memories where errorcorrecting-codes (ECC) are not needed. The remaining concern for charge retention is any degradation to the insulating oxides that occurs as a result of the stresses of device operation.

During normal operation, high fields are applied to the flash cell. The presence of the high fields over time can degrade the charge storage capabilities of the device, by effectively lowering the energy barrier, or by providing traps sites in the oxide that can act as intermediate tunneling locations. The benefit of channel hot-electron programming, compared to tunneling for programming, is that fast programming can occur at lower internal fields thereby lessening the probability of oxide damage. Nevertheless, occurrence of damage needed to be understood to ensure the stability of the M.L.C. charge.

Consequently, the charge retention ability of the insulating oxides under various process and bias field conditions were studied in great detail. Over the course of the four year M.L.C. development period, in excess of 200 billion (2e10<sup>11</sup>) flash cells were studied for charge retention, each to a resolution of floating gate charge of ~100 electrons. This exhaustive study provided more physical insight into the oxide damage mechanisms and has enabled us to build large scale empirical models for charge retention. The net result of this study was the ability to optimize process recipes and operating bias fields to maximize charge retention. This allows Intel StrataFlash memory to maintain high reliability performance, without the use of any ECC.

# **Mixed Signal Design Implementation**

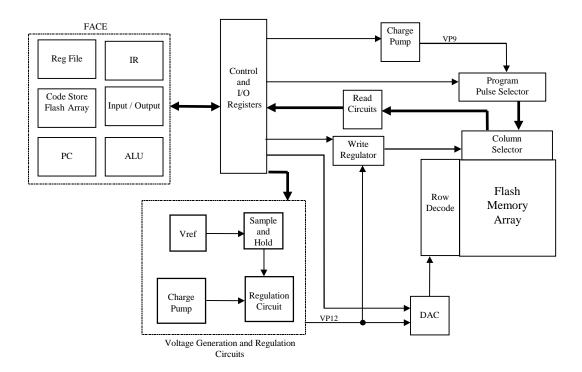

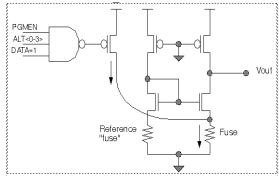

The implementation of the described charge-placement algorithm and charge-sensing operation required a mixed signal circuit design of both digital and precision analog voltage generation, regulation and control circuits. The placement algorithm is executed by utilizing an on-board control engine, or the Flash Algorithmic Control Engine (FACE). FACE runs the placement algorithm by sequencing through the programming and sensing loops. During a read operation (sensing of data at a later time), the user has random access to the memory array. A read operation performs a precision-sensing operation and invokes circuitry controlling the precise cell bias voltages.

# **Placement Algorithm Implementation**

The placement algorithm executed by FACE is stored in a small on-chip programmable flash array. The programmable microcode allows for flexibility in algorithm changes. FACE, illustrated in Figure 11, consists of the microcode storage array, program counter (PC), arithmetic logic unit (ALU), instruction decoder, clock generator, register files, and input/output circuitry. FACE uses 6,000 transistors for logic and 32k bits of flash memory for algorithm storage.

To describe the implementation of the placement algorithm, let us assume that a group of cells (i.e., a double-word, or 32-logical bits, 16-physical cells) is to be placed and is initially in the erased state (lowest floating gate charge state). Any cells not to remain in the erased state (representing logical data "11") will receive a programming pulse. FACE will look up the drain and initial control gate voltage stored in a permanent read-only register located on-chip. FACE will then set the control gate voltage through the digital to analog converter (DAC). The DAC circuit receives the FACE digital input and divides the on-chip generated 12-volt power supply (VP12) to achieve the desired control gate voltage for that particular programming pulse. The drain voltage, used

during the programming pulse, is generated from a regulation circuit that sets the gate voltage on a source follower. FACE will continue to supply the programming voltages for the pre-determined amount of time sufficient to reach the saturation region. When the programming pulse is complete, FACE will reconfigure the circuits to perform the sensing portion of the algorithm, an operation called verification. The drain and control gate voltages are now set to the same values as used in a user read access to ensure common mode between verification and read. FACE will take the result of the verification and determine which cells have reached their destination charge level and which have not. Those that have not will require an additional programming pulse with an increased control-gate voltage. A cell that no longer requires additional programming pulses will have the drain voltage disabled by the program pulse selector circuit. This sequence of events continues until all cells in the double-word have completed programming.

## **Analog Circuit Blocks for Precise Charge Placement**

Placement requires precision voltages covering a range of 4-12 volts, while the chip Vcc (user supplied voltage) is kept at a typical value of 5 volts. The voltages applied to the memory array need to be internally generated and precisely regulated. On-chip voltage generation is achieved by use of charge pumps, in which switched capacitors boost the user-supplied Vcc to higher values. Voltages are controlled using a precision voltage reference circuit and voltage regulation circuits (Figure 11).

During a programming pulse, two charge pumps are used. One charge pump generates the internal 12V supply (VP12). This is used to supply a precision control gate voltage to the flash cells, through the DAC circuit.

Figure 11: FACE and placement operation block diagram

VP12 also serves to generate the precision flash drain voltage through the write regulation circuit (WRC). The WRC generates a voltage that is applied to an NMOS transistor configured as a source follower. This transistor is in the bitline (or drain) path of the flash cell. The flash cell drain current is supplied through a second pump that generates the signal VP9. This pump is required to supply the programming current for up to 32 flash cells at a time.

During the placement algorithm, voltage stability is critical to precise charge storage. Any variations in the reference circuit voltages will be seen as variations in the flash control gate voltage, to which the programming saturated Vt is directly related. To achieve this absolute stability in the voltage reference circuit, a sample and hold circuit is employed. At the start of the placement algorithm, the sample and hold circuit samples the reference voltage and holds the value on a capacitor during the running of the entire algorithm. This guarantees the control gate voltage varies from pulse to pulse by only the desired step value and not by any additional components.

#### **Circuit Blocks for Precise Charge Sensing**

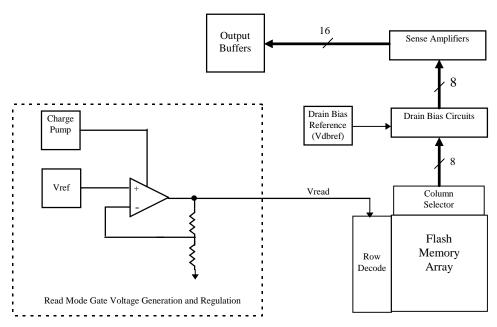

When the device is in the read mode of operation, FACE is disabled and the user has control to access the memory array. A read operation consists of sensing 16 bits worth of data from a random location in the memory array. With M.L.C., 8 flash cells are used to obtain 16 bits of data. During the read operation (Figure 12), the flash cell control gate voltage is controlled through a read

regulator circuit (RRC). Minimizing this voltage variation will minimize the variations in cell current (Equation 2). This allows for more precise measurement of the charge level stored on the floating gate. Drain voltage stability is also important to ensure that the flash cell being sensed has a high enough drain voltage to keep the memory transistor operating in the saturated region of the MOS I-V.

Due to fluctuations in user supplied Vcc and a lower value than may be needed during read, an internal voltage charge pump is used during a read operation to generate the internal voltage to supply the flash cell control gate. The RRC uses the same voltage reference circuit that is used for voltage regulation during a placement operation, as mentioned above. However, in the case of a read operation, not as much voltage stability is required so the sample and hold circuitry is not used.

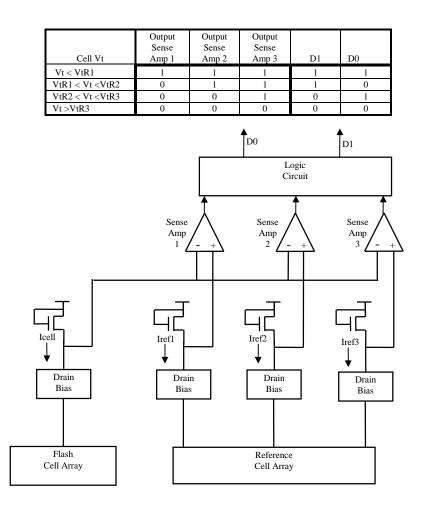

#### **Parallel Charge Sensing**

High speed random access and precise charge sensing are accomplished through a parallel charge-sensing scheme. Through direct connections to each memory cell, the data read operation determines the level of each memory cell quickly, accurately, and reliably. The data read operation senses which of the four levels the memory cell falls within based on the threshold voltages of three reference cells. This is done simultaneously with three sense amplifiers (Figure 13), where each sense amplifier compares the flash cell current being sensed to

Figure 12: Read operation block diagram

the current of the flash reference cells.

The memory cell and the reference cells are biased in such a way that each conducts a current (Icell and Iref) proportional to their respective threshold voltage (Vt and VtRef). During a read operation, Vread is placed on the control gates of the memory and reference cells, the source terminals are grounded, and the drain voltages are set through a bias circuit that utilizes a precision voltage reference circuit.

The current for the memory cell being sensed is compared to the current of the three reference cells. The memory cell and reference cell current is converted to a voltages through an active load transistor. The resultant voltages are compared by the three sense amplifiers. A sense amplifier is associated with each of the three reference cells. Each sense amplifier also has an input from the flash cell being sensed. If the current of the cell being sensed is greater than the current of the reference cell (Icell > Iref or Vt < Vtref,), the sense amplifier output is a logic "1." If the current of the cell being sensed is less than the current of the reference cell, the sense amplifier output is a logic "0." The outputs of the three sense amplifiers are connected to a logic circuit that interprets the two data bits in parallel.

Figure 13: Parallel charge sensing

# **Low-Cost Design Implementation**

Traditionally, a storage element in a memory corresponds to one bit of information. To double the amount of memory, the memory array or memory storage elements would need to be doubled. In addition to doubling the number of memory elements in the array, certain memory interface circuits must also be doubled. In particular, the memory array needs to be decoded requiring wordline and bitline decoders. In a typical single transistor non-volatile memory device (flash, EPROM), approximately 20% of the silicon area used is due to these interface circuits required to access the array. These interface circuits typically do not scale with process technology at the same rate as the memory array because they have high voltage and analog requirements.

Intel StrataFlash memory doubles the storage capacity of a memory device without doubling the memory array and the associated interface decoding circuitry. Additional circuitry is required to achieve the multiple bits per cell, but takes up a relatively small additional area. The additional overhead for circuitry is due mostly to the additional sense amplifiers, reference circuitry, and circuitry for voltage generation or charge pumps. The additional silicon area required for this circuitry represents only an additional 5% over what is necessary for a one bit per cell device. Implementations of M.L.C., which require externally supplied components (i.e., microcontroller, ECC, and voltage regulators), have the cost savings of M.L.C. diminished by these peripheral overheads. Intel StrataFlash memories achieve 2x the density at very close to 1x the area.

# **Low-Cost Process Manufacturing**

ETOX flash memory has a long manufacturing history. As such, it was necessary that any implementation of M.L.C. not disrupt that history by having unique process requirements, which would cause a slow yield learning period or poor manufacturing throughput. First and foremost for M.L.C. to be successful, it must be able to ride on a technology that produces error-free one bit per cell flash memory. This requirement throughout Intel's ETOX NOR flash memory's history has resulted in tight manufacturing margins and the learning necessary for achieving such margins. Memories that rely on ECC for even one bit per cell operation have little margin built into the basic technology. Throughout the previous discussions, mention has been made of process manufacturing attributes for M.L.C. These attributes have been achieved by utilizing the same process flow as the standard one bit per cell flash memory.

approach has maintained shared learning and has lead to lower costs. In other words, low-cost process manufacturing was achieved through an understanding of M.L.C. requirements up-front in the design of the basic process architecture at the generation where M.L.C. is introduced. The tight manufacturing margins required for M.L.C. are a natural extension of the learning from manufacturing of error-free one bit per cell flash memory and are well within the manufacturing, equipment, and process module capability.

## **Standard Product Feature Set**

One of the main challenges in implementing M.L.C. is maintaining product performance, usability, and reliability at the same levels as standard flash memories. If the implementation of M.L.C. resulted in a product that did not satisfy these goals, it would be relegated to a niche in the marketplace. Key features for a non-volatile memory are programming speed, read speed, power supply requirements, and reliability. This paper shows how our implementation of M.L.C. achieves these features. Before finishing, however, let us briefly discuss each one of them.

## **Programming Speed**

Programming speed is achieved by choosing a placement algorithm that exploits stable device operating points to enable circuit performance optimization to occur, with little limitations of flash device operation. Parallel cell programming (32 cells, or 64 bits) at a time also amortizes the placement algorithm run time. The choice of charge sensing approaches also affects programming speed as it is integral to the placement algorithm. Sensing approaches other than those described in this paper can be used. An example would be a sensing scheme that varies control gate voltage to detect the threshold voltage directly. Such a scheme, while a more direct measure of floating gate charge, does not exploit the current drive capability of the flash cell, the drive used for sensing speed performance. To sum up, the choices of algorithms, optimizations, and architecture are what allow M.L.C. programming to be as good or better than one bit per cell flash memories.

# Read Speed

As mentioned above, the choice of fixed control gate sensing and utilization of the flash cell's current drive capability allows fast read operation. In addition, parallel charge sensing allows for fast decode of the logic level, with little circuit overhead. As such, the read speed of Intel's StrataFlash memory is consistent with that of one bit per cell flash memories of comparable bit density.

#### **Power Supply**

As also discussed, the on-chip voltage generation and regulation is key to the implementation of M.L.C. One could specify an M.L.C. product that uses externally supplied precision voltages, but such a product would be more costly to the user, who would have to pay for the power supply, memory, and board space. Having the voltages generated and regulated on-chip allows for the Intel StrataFlash memory to plug directly into existing flash memory applications.

#### Reliability

Starting with high-yielding, low-defect memory, exhaustive cell studies and process and bias optimizations allow for an implementation of M.L.C. that achieves non-volatility and high reliability without requiring on-chip or system ECC. Thus the user can interface to the device with random memory location access, without latency for correction. Additionally, ECC requires overhead bits, which would diminish the cost advantages of M.L.C.

These standard flash memory product features, coupled with low-cost circuit design and manufacturing process implementation allow users to benefit from the low cost of M.L.C. without having to sacrifice needed features or performance.

#### Conclusion

It has been shown how Intel StrataFlash memory achieves multiple bits per cell, coupled with traditional process scaling, to provide an advance in memory cost reduction. The M.L.C requirements of precise charge placement, precise charge sensing and precise charge retention are achieved by exploiting stable device-operating points and direct access to the memory cell, employing mixed signal digital and analog design. Noncell-related costs are held low by riding on the tight manufacturing margins developed for error-free one bit per cell flash memories. A standard product feature set ensures that the cost advantages of M.L.C. are available to the mainstream flash memory market.

## Acknowledgments

The authors would like to thank the members of the M.L.C. development groups, whose dedicated work helped turn a few ideas into a product reality.

#### References

- [1] Kynett, V.N., et. al., "An In-System Reprogrammable 256K CMOS Flash Memory," Technical Digest IEEE International Solid State Circuits Conference, 1988, pp. 132-133.

- [2] Tam, S., Ko, P.K., and Hu, C., "Lucky-Electron Model of Channel Hot Electron Injection in MOSFET's," IEEE Transactions Electron Devices, September 1984.

- [3] Lenzlinger, M. and Snow, E.H., "Fowler-Nordheim Tunneling into Thermally Grown SiO<sub>2</sub>," Journal of Applied Physics, vol. 40, No. 1, January 1967, pp. 278-283.

- [4] Ong, T.C., et. al., "Erratic Erase in ETOX<sup>TM</sup> Flash Memory Array," IEEE VLSI Symposium, 1993, p. 145.

- [5] Eitan, B. and Frohman-Bentchkowsky, D., "Surface Conduction in Short-Channel MOS Devices as a Limitation to VLSI Scaling," IEEE Transactions on Electron Devices, vol. ED-29, No. 2, February 1982, pp. 254-266.

- [6] Wu, K., et. al., "A Model for EPROM Intrinsic Charge Loss Through Oxide-Nitride-Oxide (ONO) Interpoly Dielectric," 28<sup>th</sup> Annual Proceedings IEEE International Reliability Physics Symposium, 1990, p. 145.

- [7] Mielke, N., "New EPROM Data-Loss Mechanisms," 21<sup>st</sup> Annual Proceedings IEEE International Reliability Physics Symposium, 1983, p. 106.

# **Authors' Biographies**

Al Fazio is a Principal Engineer in Flash Technology Development. He received a B.Sc. in Physics from the State University of New York at Stony Brook in 1982 and joined Intel the same year. He has been involved in development programs including SRAM, EPROM, E<sup>2</sup>PROM, NVRAM, and Flash Memories. He was responsible for the Technology Development of the Intel StrataFlash<sup>TM</sup> memory. He holds more than a dozen patents and has authored or co-authored several technical papers, two of which have received Outstanding Paper Awards at the IEEE International Reliability Physics Symposium and at the IEEE International Solid State Circuits Conference. He is presently responsible for Intel's Multi-Level-Cell and Advanced Flash Memory Cell Development and currently serves as General Chairman of the IEEE Non-Volatile Semiconductor Memory Workshop. His e-mail address is al fazio@ccm.sc.intel.com

Mark Bauer is a Senior Staff Engineer in Flash Circuit Design. He received his B.S.E.E. from the University of California, Davis in 1985. He joined Intel's Memory Components Division that same year, working on EPROM design. He was responsible for Circuit Design Development of the Intel StrataFlash<sup>TM</sup> memory. He holds more than a dozen patents in the field of nonvolatile memories and has authored two technical papers, one of which received an Outstanding Paper Award at the IEEE International Solid State Circuits Conference. He is presently responsible for Intel's next generation Multi-Level-Cell Circuit Design. His e-mail address is mark\_bauer@ccm.fm.intel.com

# **Redundancy Yield Model for SRAMS**

Nermine H. Ramadan, STTD Integration/Yield, Hillsboro, OR, Intel Corp.

Index words: Poisson's formula, yield, defect density, repair rate

## **Abstract**

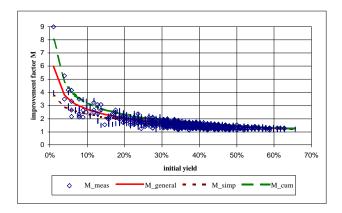

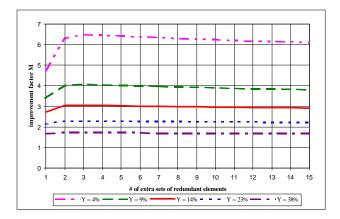

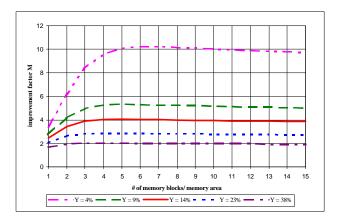

This paper describes a model developed to calculate the number of redundant good die per wafer. A block redundancy scheme is used here, where the entire defective memory subarray is replaced by a redundant element. A formula is derived to calculate the amount of improvement expected after redundancy. improvement is given in terms of the ratio of the overall good die per wafer to the original good die per wafer after considering some key factors. These factors are memory area, available redundant elements, defect density and defect types with respect to the total reject die and defect distribution on the memory area. The model uses Poisson's equation to define the yield, then the appropriate boundary conditions that account for those factors are applied. In the case of a new product, knowing the die size, memory design, and total die per wafer, the model can be used to predict the redundancy yield for this product at different initial yield values. Optimizing the memory design by varying the number of memory blocks and/or redundant elements to enhance redundancy is also discussed. The model was applied to three products from two different process generations and showed good agreement with the measured data.

# Introduction

Due to the continuing increase in the size of memory arrays, reaching a high yield from the same wafer is more challenging than ever. Redundancy is a way to improve the wafer yield and to reduce the test cost per good die by fixing potentially repairable defects. In order to forecast the volume of a certain product when redundancy is applied, it is important to estimate, as accurately as possible, the number of die gained after redundancy.

Redundancy is the process of replacing defective circuitry with spare elements. In SRAMs, rows and/or columns can be replaced, as well as an entire subarray. In a

previous study[1], a redundant yield estimation methodology was developed. It is applicable to row, column or block redundancy schemes. It distinguishes between repairable and non-repairable faults within a memory block. In order to apply this method, new CAD tools are required. This method is useful if row or column redundancy is used.

This paper will focus only on the yield estimation for block redundancy, as block redundancy was preferred over row and column redundancy for the SRAM architecture. It is usually easier to replace the entire subarray. This might seem like overkill; however, replacing the entire subarray allows for the replacement of defective peripheral circuits in addition to just the memory array elements. It also allows for the replacement of multiple bad bits, or other combinations of failing bits, rows and columns.

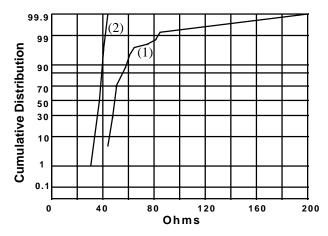

A yield multiplier M is defined as the ratio of the total good die after redundancy to the original good die per wafer, or

$$M = total redundant good/original good$$

(1)

so that the redundant yield,  $Y_{red}$ , is given as

$$Y_{red} = M \times Y \tag{2}$$

where Y is the initial yield. Forecasting of the redundancy yields is based on how accurately the factor M is calculated. A formula for M was obtained by using the correlated defect model. According to this model, an expression for the yield of die containing a number of defects, I, is given by

$$y_I = \{(n+I+1)! \times (DA)^I\} / \{(I! n^{I-1}) \times (1+D A/n)^{n+I}\} \times f^I$$

(3)

where

$y_I$  = yield of a die with I defects

D = average defect density ( #/cm<sup>2</sup> )

A = die area (cm<sup>2</sup>)

n= correlation factor between defects

f = fraction of the die area that contains the defects

The yield of die with zero defects can be obtained by setting I=0 and f=1 as

$$Y = 1 / \{ 1 + (A D / n) \}^{n}$$

(4)

With n = 4 and using equation (4) to substitute for the defect density, equation (3) becomes

$$y_i = Y \times ((I+3)(I+2)(I+1)/6) \times f^I \times (1-Y^{1/4})^I$$

(5)

Introducing g as the fraction of repairable defects, g varies depending on the number of repaired defects. An expression for M was obtained by summing  $y_I$  over the ratio of correctable defects and substituting in (2)

$$M = 1 + {}^{k}\Sigma_{I=1} ((I+3)(I+2)(I+1)/6) \times (gf(1-Y^{1/4}))^{I}$$

(6)

M was calculated by entering arbitrary values of g and f in equation (6). However, there was no evidence to support the values of the repairable defect density represented by g used to calculate M.

Another formula was used to estimate the yield multiplier M. The yield is derived from Poisson's equation [2]

$$Y = \exp(-AD) \tag{7}$$

Instead of using a constant defect density, D, Murphy assumed several defect density distributions[3]. The most preferred distribution was a Gaussian. Stapper used a gamma distribution, which led to the following yield formula [4]

$$Y = 1 / \{ 1 + (A D / \alpha) \}^{\alpha}$$

(8)

where  $\alpha$  is the average value of the coefficient of variation for the gamma function. The yield multiplier derived from the previous yield formula is given by

$$M = S \times (1 + 0.01 (L + I) A_{sb} D / k)^{k}$$

(9)

where

S =fuse programming success rate

I = number of redundant elements

L = number of subarrays

$A_{sb}$  = area of subarray ( mm<sup>2</sup> )

k = constant for MOS process

0.01=conversion from mm<sup>2</sup> to cm<sup>2</sup>

This simple formula is actually overestimating the redundancy improvement, since it assumes that all the defects are repairable.

In order to get a better estimate of the yield improvement, the nature and distribution of the defect need to be understood. These are taken into account in this model. When considering defects, it is important to realize that not all reject die are repairable: a die failing for a short, for example, cannot be repaired. Also the number of defective subarrays that could be repaired depends on the available redundant elements per memory block. This means that having more than one defect per die requires a certain distribution of those defects in order for redundancy to be successful.

Taking into account the above factors and using Poisson's equation to describe the yield, the present model was able to predict the redundant yield within the same range as shown by the real data. The following section illustrates how the key parameters affecting redundancy are used to develop the model.

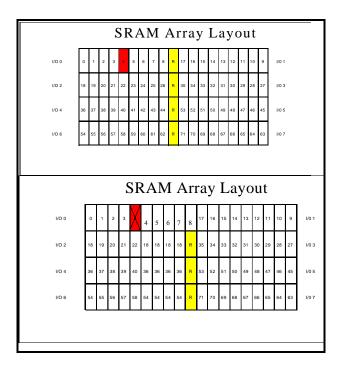

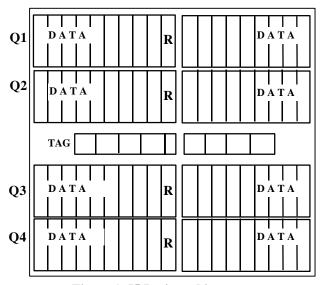

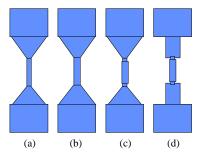

# **SRAM Array Layout**

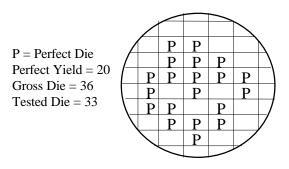

Figure 1 shows the layout of a SRAM memory array. Before going into details, the following terms are defined as they will be used throughout the paper:

- Subarra y This is a unit array of the memory area, and is shown as subarrays 0 to 72 in Figure 1.

- *Memory block or bloc k*This is a segment of the memory area, and is one of four rows shown in Figure 1.

- Redundant element or elemen. This is a spare subarray used to replace a memory subarray, and is given as subarrays R in Figure 1.

The die consists of two areas:

- Repairable are a This includes all the circuitry in the subarray. In this model the repairable area is the sum of the areas of the memory subarrays.

- *Non-repairable are a* This includes the periphery area. The redundancy elements are also considered part of the non-repairable area.